本文介绍的是STM32F103 中等容量产品(STM32F103x

8xx和STM32F103xBxx)的硬件数据,即64KB或128KB Flash,20KB SRAM。

ST官网资料:https://www.st.com/zh/microcontrollers-microprocessors/stm32f103.html

ST官方的中等容量产品Datasheet:https://www.st.com/resource/en/datasheet/stm32f103c8.pdf

之前的文章:https://blog.csdn.net/weixin_43764974/category_11021363.html

- 一、概览

- 1.1 STM32F103 系列芯片容量的区分

- 1.2、外设概览

- 二、具体

- 2.1 内核、存储、CRC计算单元

- 2.2 嵌套向量中断控制器(NVIC)

- 2.3 外部中断/事件控制器(EXTI)

- 2.4 时钟和启动

- 2.5 自举模式与程序下载

- 2.6 供电与低功耗模式

- 2.7 DMA

- 2.8 RTC(实时时钟)和后备寄存器

- 2.9 定时器和看门狗

- 2.10 I2C总线

- 2.11 通用同步/异步收发器(USART)

- 2.12 串行外设接口(SPI)

- 2.13 控制器区域网络(CAN)

- 2.14 通用串行总线(USB)

- 2.15 通用输入输出接口(GPIO)

- 2.16 ADC(模拟/数字转换器)

- 2.17 温度传感器

- 2.18 串行单线JTAG调试口(SWJ-DP)

- 三、引脚定义

一、概览

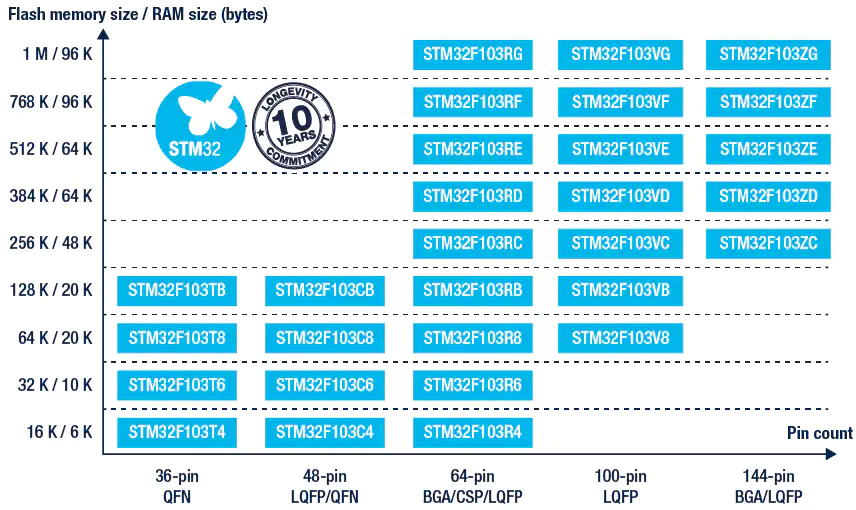

1.1 STM32F103 系列芯片容量的区分

STM32的小容量、中等容量和大容量指的是芯片的闪存(Flash)容量的大小,一般有以下的划分1:

- 小容量:闪存小于等于32K

- 中等容量:64K小于等于闪存小于等于128K

- 大容量:闪存大于等于256K

STM32F103xx是一个完整的系列,其成员之间是完全地脚对脚兼容,软件和功能上也兼容。在参考手册中,STM32F103x4和STM32F103x6被归为小容量产品,STM32F103x8和STM32F103xB被归为中等容量产品,STM32F103xC、STM32F103xD和STM32F103xE被归为大容量产品。

STM32F103x4、STM32F103x6、 STM32F103xC、STM32F103xD和STM32F103xE可直接替换中等容量的STM32F103x8/B产品,为用户在产品开发中尝试使用不同的存储容量提供了更大的自由度。

同时,STM32F103xx增强型产品与现有的STM32F101xx基本型和STM32F102xx USB基本型产品全兼容。

Flash相当于你电脑的SSD,SRAM相当于你电脑的内存。

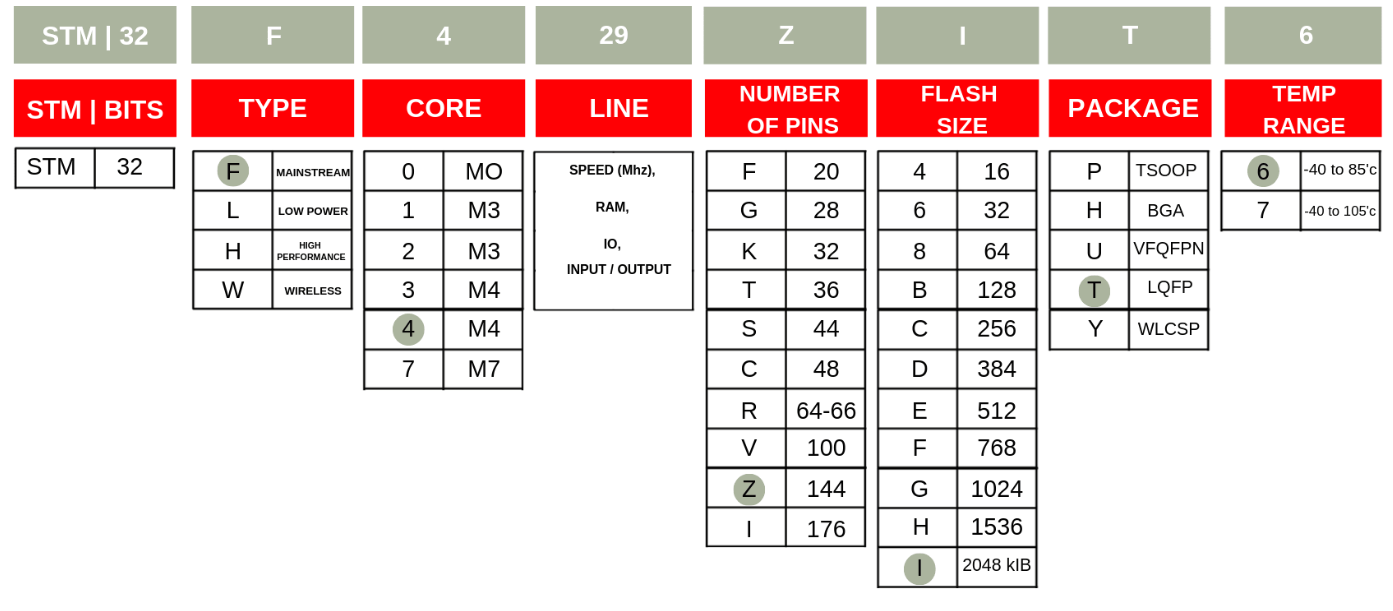

之前的文章也讲过,根据芯片的具体名称来确定内核、引脚数、Flash容量、封装等信息:

1.2、外设概览

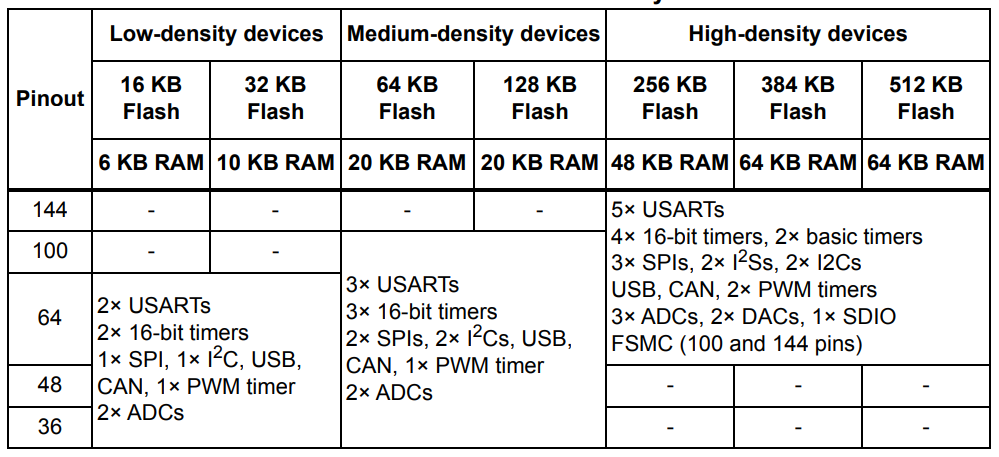

STM32F103系列不同容量产品的外设概览:

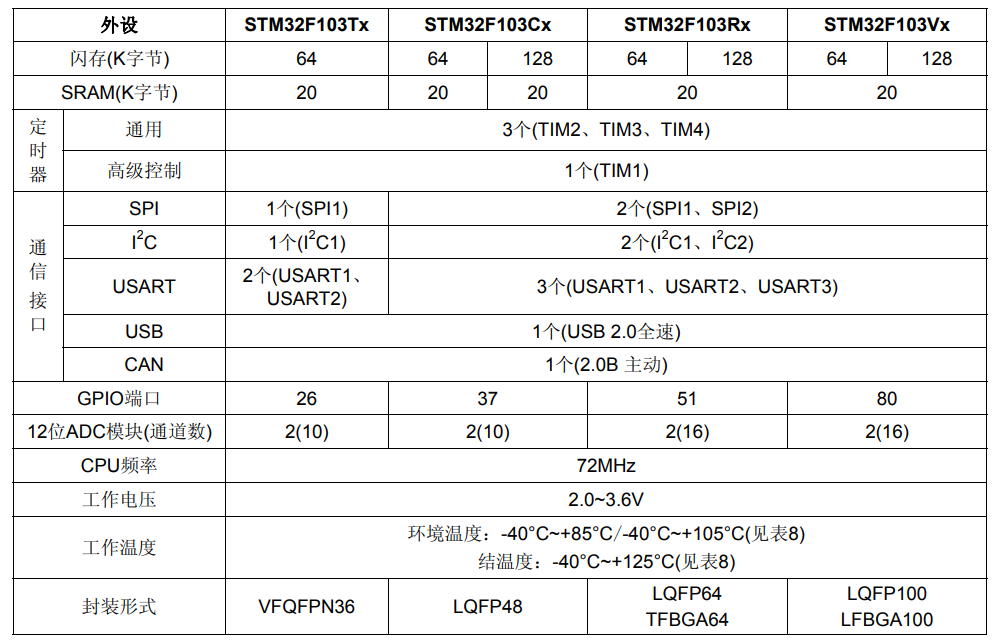

STM32F103中等容量产品外设对比:

二、具体

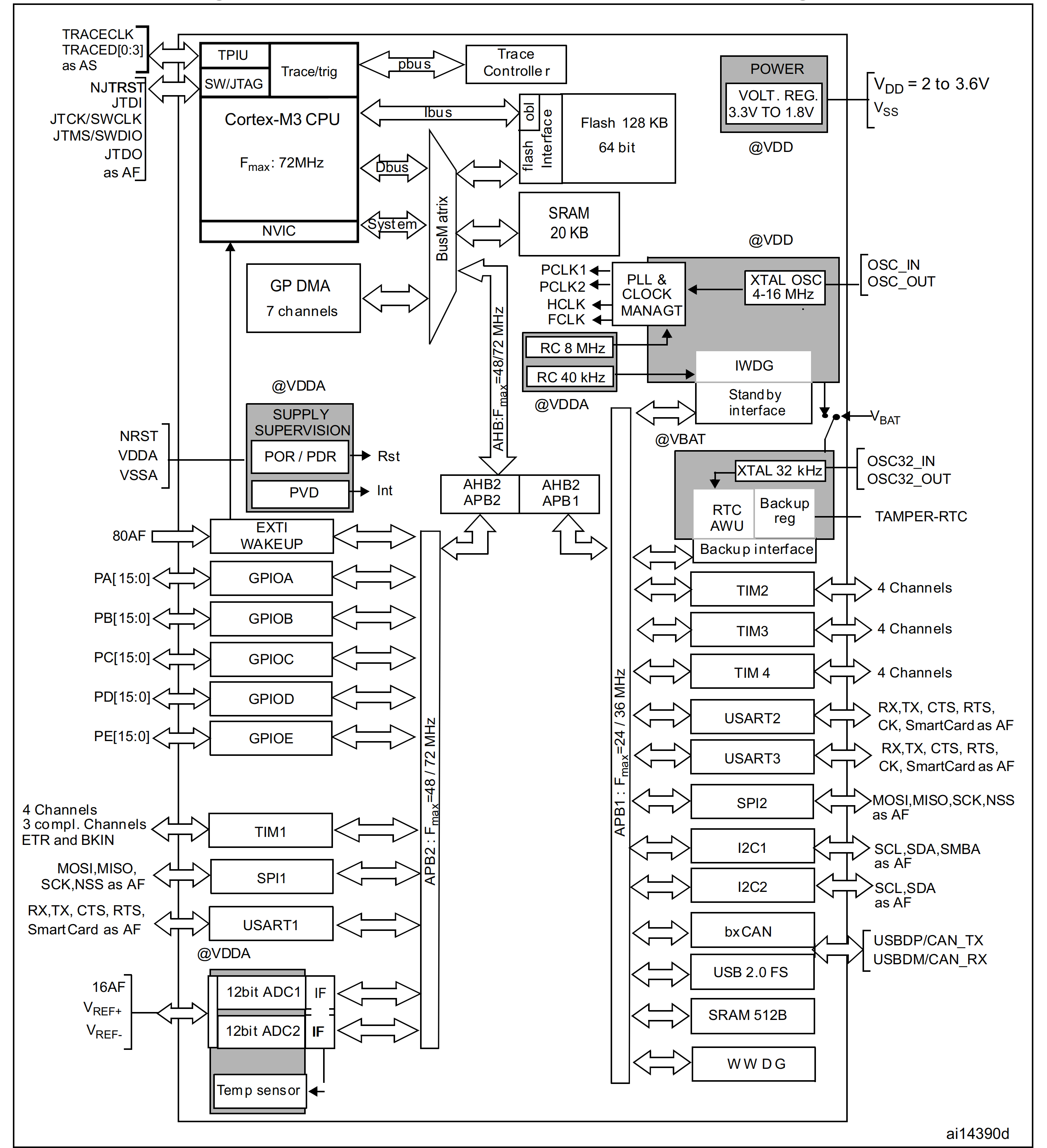

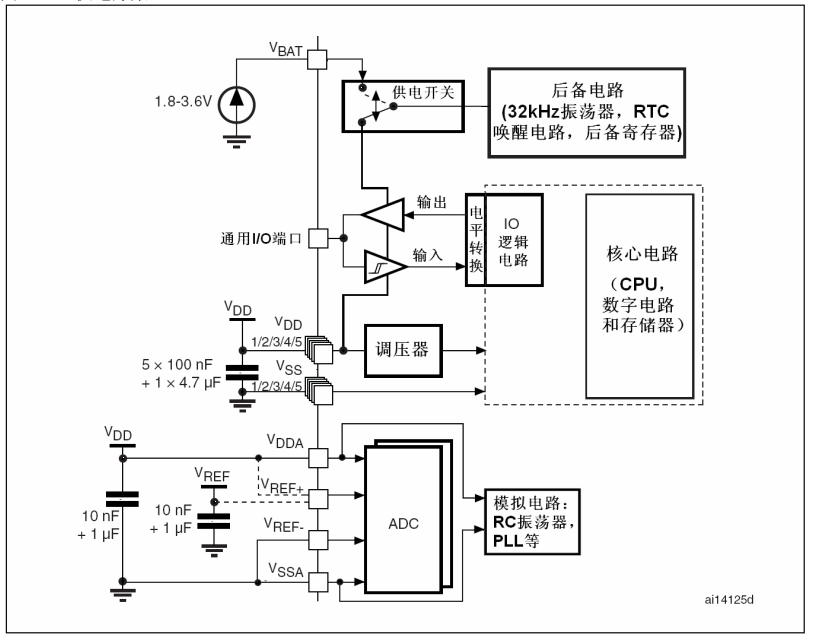

STM32F103模块框图(128KB Flash+20KB SRAM):

2.1 内核、存储、CRC计算单元

-

STM32 F1系列都是ARM的

Cortex™-M3内核。

ARM的Cortex™-M3是32位的RISC处理器,提供额外的代码效率,在通常8和16位系统的存储空间上发挥了ARM内核的高性能。

STM32F103xx增强型系列拥有内置的ARM核心,因此它与所有的ARM工具和软件兼容。 -

中等容量产品的

Flash是64KB或128KB,用于存放程序和数据。 -

20K字节的内置

SRAM,CPU能以0等待周期访问(读/写)。 -

CRC(循环冗余校验)计算单元使用一个固定的多项式发生器,从一个32位的数据字产生一个CRC码。

在众多的应用中,基于CRC的技术被用于验证数据传输或存储的一致性。在EN/IEC 60335-1标准的范围内,它提供了一种检测闪存存储器错误的手段,CRC计算单元可以用于实时地计算软件的签名,并与在链接和生成该软件时产生的签名对比。

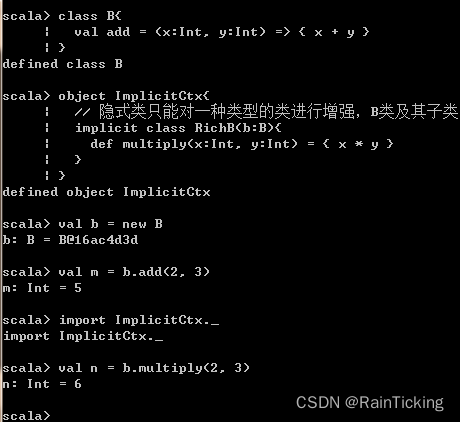

STM32的CRC单元是一个硬件外设,用于计算循环冗余校验码,以检测数据的完整性和正确性。它使用一个固定的多项式

0x4C11DB7,与以太网协议相同。它可以对输入和输出数据进行位反转操作,以适应不同的CRC标准。它有一个32位的数据寄存器,一个8位的通用寄存器,和一个32位的CRC寄存器。

STM32的CRC单元可以用于通信协议、数据存储、远程升级等应用场景,提供硬件支持,节省代码空间和CPU时间。它也可以用于验证Flash的完整性,通过在IAR中配置CRC计算参数,自动对整个Flash空间进行CRC计算,并将结果放在Flash末尾。

https://blog.csdn.net/ybhuangfugui/article/details/109831213

2.2 嵌套向量中断控制器(NVIC)

STM32F103xx增强型产品内置嵌套的向量式中断控制器,能够处理多达43个可屏蔽中断通道(不包括16个Cortex™-M3的中断线)和16个优先级。

- 紧耦合的NVIC能够达到低延迟的中断响应处理

- 中断向量入口地址直接进入内核

- 紧耦合的NVIC接口

- 允许中断的早期处理

- 处理晚到的较高优先级中断

- 支持中断尾部链接功能

- 自动保存处理器状态

- 中断返回时自动恢复,无需额外指令开销

该模块以最小的中断延迟提供灵活的中断管理功能。

NVIC是

Nested Vectored Interrupt Controller的缩写,意思是嵌套向量中断控制器。它是一种硬件外设,用于管理和分配处理器中的中断请求。它为CPU的中断请求提供了一个优先级和屏蔽方案,以便CPU可以更好地处理中断请求。NVIC还支持不同的优先级和预先定义的中断源,其中一些可以由外部和内部事件触发。NVIC有以下主要特性:

- 支持1到240个可屏蔽的中断源

- 支持16个优先级,每个优先级可以进一步分为子优先级

- 支持嵌套中断,即在处理一个低优先级的中断时,可以暂停并响应一个高优先级的中断

- 支持向量表重定位,即可以将向量表放在不同的存储区域

- 支持尾链技术,即在返回一个中断前,可以检查是否有新的中断发生,并直接跳转到新的中断处理程序,而不用恢复原来的状态

2.3 外部中断/事件控制器(EXTI)

外部中断/事件控制器包含19个边沿检测器,用于产生中断/事件请求。

每个中断线都可以独立地配置它的触发事件(上升沿或下降沿或双边沿),并能够单独地被屏蔽;有一个挂起寄存器维持所有中断请求的状态。EXTI可以检测到脉冲宽度小于内部APB2的时钟周期。多达80个通用I/O口连接到16个外部中断线。

2.4 时钟和启动

系统时钟的选择是在启动时进行,复位时内部8MHz的RC振荡器被选为默认的CPU时钟,随后可以选择外部的、具失效监控的4~16MHz时钟;当检测到外部时钟失效时,它将被隔离,系统将自动地切换到内部的RC振荡器,如果使能了中断,软件可以接收到相应的中断。同样,在需要时可以采取对PLL时钟完全的中断管理(如当一个间接使用的外部振荡器失效时)。

多个预分频器用于配置AHB的频率、高速APB(APB2)和低速APB(APB1)区域。AHB和高速APB的最高频率是72MHz,低速APB的最高频率为36MHz。

时钟树:

2.5 自举模式与程序下载

STM32的自举模式是指STM32在复位后,根据BOOT[1:0]引脚的状态,选择不同的存储器作为启动源的模式。STM32有三种自举模式,分别是:

- Main Flash memory(BOOT1=x

BOOT0=0):从STM32内置的Flash中启动,这是正常的工作模式。 - System memory(

BOOT1=0 BOOT0=1):从STM32自带的BootLoader中启动,这种模式可以通过串口或USB等接口重新编程Flash。 - Embedded Memory(

BOOT1=1 BOOT0=1):从STM32内置的SRAM中启动,这种模式可以用于调试。

STM32的自举模式可以用于不同的应用场景,比如远程升级、调试接口恢复、向量表重定位等。

下载程序的时候,选择哪种模式,取决于使用的下载工具和接口。一般来说,有以下几种情况:

- 如果使用JTAG或SWD接口,可以选择Main Flash memory模式,这种情况下,可以直接通过调试器将程序下载到STM32内置的Flash中,并进行调试。

- 如果使用串口或USB接口,可以选择System memory模式,这种情况下,需要使用STM32自带的BootLoader或者第三方的BootLoader软件,通过串口或USB将程序下载到STM32内置的Flash中。下载完成后,需要将BOOT0引脚接地,重新上电或复位,才能运行程序。

- 如果使用其他的存储器,比如外部的Flash或者SD卡等,可以选择Embedded Memory模式,这种情况下,需要在STM32内置的SRAM中运行一个自定义的BootLoader程序,通过某种方式(比如串口、USB、SPI等)将程序从外部存储器读取到STM32内置的Flash中,并跳转到程序入口执行。

Main Flash memory和System memory的区别主要有以下几点:

- Main Flash memory是STM32内置的Flash,一般我们使用JTAG或者SWD模式下载程序时,就是下载到这个里面,重启后也直接从这启动程序。System memory是STM32自带的BootLoader,这种模式启动的程序功能是由厂家设置的,一般用于通过串口或USB等接口重新编程Flash。

- Main Flash memory的容量一般比System memory大,可以存放更多的代码和数据。System memory的容量一般比较小,只能存放一个固定的BootLoader程序。

- Main Flash memory可以支持XIP(执行就地),也就是可以直接从Flash中运行代码,无需拷贝到内存中。System memory不支持XIP,需要将代码拷贝到内存中才能运行。

- Main Flash memory可以通过不同的方式进行编程和擦除,比如JTAG、SWD、IAP等。System memory只能通过厂家提供的BootLoader进行编程和擦除,而且只能按整个Block进行擦除。

2.6 供电与低功耗模式

供电:

- VDD = 2.0~3.6V:VDD引脚为I/O引脚和内部调压器供电。

- VSSA,VDDA = 2.0~3.6V:为ADC、复位模块、RC振荡器和PLL的模拟部分提供供电。使用ADC时,VDDA不得小于2.4V。VDDA和VSSA必须分别连接到VDD和VSS。

- VBAT = 1.8~3.6V:当关闭VDD时,(通过内部电源切换器)为RTC、外部32kHz振荡器和后备寄存器供电。

VDD 、VSS、VSSA、VDDA 、 VBAT 是STM32芯片的电源引脚,它们的含义如下:

VDD是芯片的工作正电压,一般为2.0~3.6V,通过内置的电压调节器提供所需的1.8V电源。VSS是芯片的工作负电压,一般接地。VDDA是芯片的工作模拟正电压,为所有的模拟电路部分供电,包括ADC模块,复位电路,PVD(可编程电压监测器),PLL,上电复位(POR)和掉电复位(PDR)模块,控制VBAT切换的开关等。即使不使用ADC功能,也需要连接VDDA,强烈建议VDD和VDDA使用同一个电源供电。VSSA是芯片的工作模拟负电压,一般接地。如果有VREF- 引脚 (根据封装而定),它必须连接到VSSA,确保共地。VBAT是电池或其他电源供电引脚,当VDD 掉电后,通过VBAT 脚为实时时钟 (RTC)和备份寄存器提供电源。

供电监视器:

内部集成了上电复位(POR)/掉电复位(PDR)电路,该电路始终处于工作状态,保证系统在供电超过2V时工作;当VDD低于设定的阀值(VPOR/PDR)时,置器件于复位状态,而不必使用外部复位电路。

器件中还有一个可编程电压监测器(PVD),它监视VDD/VDDA供电并与阀值VPVD比较,当VDD低于或高于阀值VPVD时产生中断,中断处理程序可以发出警告信息或将微控制器转入安全模式。PVD功能需要通过程序开启。

电压调压器:

调压器有三个操作模式:主模式(MR)、低功耗模式(LPR)和关断模式

- 主模式(MR)用于正常的运行操作

- 低功耗模式(LPR)用于CPU的停机模式

- 关断模式用于CPU的待机模式:调压器的输出为高阻状态,内核电路的供电切断,调压器处于零消耗状态(但寄存器和SRAM的内容将丢失)

该调压器在复位后始终处于工作状态,在待机模式下关闭处于高阻输出。

低功耗模式:

STM32F103xC、STM32F103xD和STM32F103xE增强型产品支持三种低功耗模式,可以在要求低功耗、短启动时间和多种唤醒事件之间达到最佳的平衡。

- 睡眠模式

在睡眠模式,只有CPU停止,所有外设处于工作状态并可在发生中断/事件时唤醒CPU。 - 停机模式

在保持SRAM和寄存器内容不丢失的情况下,停机模式可以达到最低的电能消耗。在停机模式下,停止所有内部1.8V部分的供电,PLL、HSI的RC振荡器和HSE晶体振荡器被关闭,调压器可以被置于普通模式或低功耗模式。

可以通过任一配置成EXTI的信号把微控制器从停机模式中唤醒,EXTI信号可以是16个外部I/O口之一、PVD的输出、RTC闹钟或USB的唤醒信号。 - 待机模式

在待机模式下可以达到最低的电能消耗。内部的电压调压器被关闭,因此所有内部1.8V部分的供电被切断;PLL、HSI的RC振荡器和HSE晶体振荡器也被关闭;进入待机模式后,SRAM和寄存器的内容将消失,但后备寄存器的内容仍然保留,待机电路仍工作。

从待机模式退出的条件是:NRST上的外部复位信号、IWDG复位、WKUP引脚上的一个上升边沿或RTC的闹钟到时。

注: 在进入停机或待机模式时,RTC、IWDG和对应的时钟不会被停止。

2.7 DMA

灵活的7路通用DMA可以管理存储器到存储器、设备到存储器和存储器到设备的数据传输;DMA控制器支持环形缓冲区的管理,避免了控制器传输到达缓冲区结尾时所产生的中断。每个通道都有专门的硬件DMA请求逻辑,同时可以由软件触发每个通道;传输的长度、传输的源地址和目标地址都可以通过软件单独设置。

DMA可以用于主要的外设:SPI、I2C、USART,通用、基本和高级控制定时器TIMx和ADC。

2.8 RTC(实时时钟)和后备寄存器

RTC和后备寄存器通过一个开关供电,在VDD有效时该开关选择VDD供电,否则由VBAT引脚供电。后备寄存器(10个16位的寄存器)可以用于在关闭VDD时,保存20个字节的用户应用数据。RTC和后备寄存器不会被系统或电源复位源复位;当从待机模式唤醒时,也不会被复位。

实时时钟具有一组连续运行的计数器,可以通过适当的软件提供日历时钟功能,还具有闹钟中断和阶段性中断功能。RTC的驱动时钟可以是一个使用外部晶体的32.768kHz的振荡器、内部低功耗RC振荡器或高速的外部时钟经128分频。内部低功耗RC振荡器的典型频率为40kHz。为补偿天然晶体的偏差,可以通过输出一个512Hz的信号对RTC的时钟进行校准。RTC具有一个32位的可编程计数器,使用比较寄存器可以进行长时间的测量。有一个20位的预分频器用于时基时钟,默认情况下时钟为32.768kHz时,它将产生一个1秒长的时间基准。

2.9 定时器和看门狗

中等容量的STM32F103xx增强型系列产品包含1个高级控制定时器、3个普通定时器,以及2个看门狗定时器和1个系统嘀嗒定时器。

下表比较了高级控制定时器、普通定时器和基本定时器的功能:

高级控制定时器(TIM1):

高级控制定时器(TIM1)可以被看成是分配到6个通道的三相PWM发生器,它具有带死区插入的互补PWM输出,还可以被当成完整的通用定时器。四个独立的通道可以用于:

- 输入捕获

- 输出比较

- 产生PWM(边缘或中心对齐模式)

- 单脉冲输出

配置为16位标准定时器时,它与TIMx定时器具有相同的功能。配置为16位PWM发生器时,它具有全调制能力(0~100%)。

在调试模式下,计数器可以被冻结,同时PWM输出被禁止,从而切断由这些输出所控制的开关。很多功能都与标准的TIM定时器相同,内部结构也相同,

通用定时器(TIMx):

STM32F103xx增强型产品中,内置了多达3个可同步运行的标准定时器(TIM2、TIM3和TIM4)。每个定时器都有一个16位的自动加载递加/递减计数器、一个16位的预分频器和4个独立的通道,每个通道都可用于输入捕获、输出比较、PWM和单脉冲模式输出,在最大的封装配置中可提供最多12个输入捕获、输出比较或PWM通道。

它们还能通过定时器链接功能与高级控制定时器共同工作,提供同步或事件链接功能。在调试模式下,计数器可以被冻结。任一标准定时器都能用于产生PWM输出。每个定时器都有独立的DMA请求机制。

这些定时器还能够处理增量编码器的信号,也能处理1至3个霍尔传感器的数字输出。

独立看门狗:

独立的看门狗是基于一个12位的递减计数器和一个8位的预分频器,它由一个内部独立的40kHz的RC振荡器提供时钟;因为这个RC振荡器独立于主时钟,所以它可运行于停机和待机模式。它可以被当成看门狗用于在发生问题时复位整个系统,或作为一个自由定时器为应用程序提供超时管理。通过选项字节可以配置成是软件或硬件启动看门狗。在调试模式下,计数器可以被冻结。

窗口看门狗:

窗口看门狗内有一个7位的递减计数器,并可以设置成自由运行。它可以被当成看门狗用于在发生问题时复位整个系统。它由主时钟驱动,具有早期预警中断功能;在调试模式下,计数器可以被冻结。

系统时基定时器:

这个定时器是专用于实时操作系统,也可当成一个标准的递减计数器。它具有下述特性:

- 24位的递减计数器

- 自动重加载功能

- 当计数器为0时能产生一个可屏蔽系统中断

- 可编程时钟源

2.10 I2C总线

多达2个I2C总线接口,能够工作于多主模式或从模式,支持标准和快速模式。I2C接口支持7位或10位寻址,7位从模式时支持双从地址寻址。内置了硬件CRC发生器/校验器。它们可以使用DMA操作并支持SMBus总线2.0版/PMBus总线。

2.11 通用同步/异步收发器(USART)

USART1接口通信速率可达4.5兆位/秒,其他接口的通信速率可达2.25兆位/秒。USART接口具有硬件的CTS和RTS信号管理、支持IrDA SIR ENDEC传输编解码、兼容ISO7816的智能卡并提供LIN主/从功能。

所有USART接口都可以使用DMA操作。

同步/异步的区别如下:

- 同步收发器 (Synchronous Receiver and Transmitter)是指在通信时需要对外提供时钟信号,以保证发送方和接收方的数据同步。同步收发器的优点是传输速率高,缺点是需要额外的线路传输时钟信号,增加了硬件成本和复杂度。

- 异步收发器 (Asynchronous Receiver and Transmitter)是指在通信时不需要对外提供时钟信号,而是通过起始位和停止位来标识每个数据帧的开始和结束。异步收发器的优点是简化了硬件设计,缺点是传输速率低,且需要额外的位来表示数据帧的边界,增加了数据冗余。

2.12 串行外设接口(SPI)

多达2个SPI接口,在从或主模式下,全双工和半双工的通信速率可达18兆位/秒。3位的预分频器可产生8种主模式频率,可配置成每帧8位或16位。硬件的CRC产生/校验支持基本的SD卡和MMC模式。

所有的SPI接口都可以使用DMA操作。

串行通信是指在计算机总线或其他数据通道上,每次传输一个位元数据,并连续进行以上单次过程的通信方式。与之对应的是并行通信,它在串行端口上通过一次同时传输若干位元数据的方式进行通信。

串行通信的特点是传输线少、成本低、适用于远距离通信,但是传输速率低、易受干扰。串行通信可以分为同步通信和异步通信,它们的区别在于是否需要对外提供时钟信号来保证数据同步。

2.13 控制器区域网络(CAN)

CAN接口兼容规范2.0A和2.0B(主动),位速率高达1兆位/秒。它可以接收和发送11位标识符的标准帧,也可以接收和发送29位标识符的扩展帧。具有3个发送邮箱和2个接收FIFO,3级14个可调节的滤波器。

2.14 通用串行总线(USB)

STM32F103xx增强型系列产品,内嵌一个兼容全速USB的设备控制器,遵循全速USB设备(12兆位/秒)标准,端点可由软件配置,具有待机/唤醒功能。USB专用的48MHz时钟由内部主PLL直接产生(时钟源必须是一个HSE晶体振荡器)。

2.15 通用输入输出接口(GPIO)

每个GPIO引脚都可以由软件配置成输出(推挽或开漏)、输入(带或不带上拉或下拉)或复用的外设功能端口。多数GPIO引脚都与数字或模拟的复用外设共用。除了具有模拟输入功能的端口,所有的GPIO引脚都有大电流通过能力。

在需要的情况下,I/O引脚的外设功能可以通过一个特定的操作锁定,以避免意外的写入I/O寄存器。在APB2上的I/O脚可达18MHz的翻转速度。

STM32的GPIO有8种工作模式,分别是:

- 模拟输入:GPIO引脚用于ADC采集电压的输入通道,信号不经过施密特触发器,直接进入ADC模块,CPU不能读取引脚状态。

- 浮空输入:GPIO引脚的电平信号直接进入输入数据寄存器,MCU直接读取引脚电平,引脚的电平状态是不确定的,完全由外部输入决定。

- 上拉输入:GPIO引脚内部接上拉电阻,引脚默认为高电平,如果外部输入低电平,则引脚为低电平。

- 下拉输入:GPIO引脚内部接下拉电阻,引脚默认为低电平,如果外部输入高电平,则引脚为高电平。

- 推挽输出:GPIO引脚可以输出强高低电平,连接数字器件,输出端由P-MOS管和N-MOS管组成的反相器驱动。

- 开漏输出:GPIO引脚只能输出强低电平,高电平需要借助外部上拉电阻完成对外驱动,输出端只有N-MOS管工作。

- 复用推挽输出:GPIO引脚复用为其他外设的功能引脚,输出数据由其他外设提供,可以输出强高低电平。

- 复用开漏输出:GPIO引脚复用为其他外设的功能引脚,输出数据由其他外设提供,只能输出强低电平。

2.16 ADC(模拟/数字转换器)

STM32F103xx增强型产品内嵌2个12位的模拟/数字转换器(ADC),每个ADC共用多达16个外部通道,可以实现单次或扫描转换。在扫描模式下,自动进行在选定的一组模拟输入上的转换。

ADC接口上的其它逻辑功能包括:

- 同步的采样和保持

- 交叉的采样和保持

- 单次采样

ADC可以使用DMA操作。

模拟看门狗功能允许非常精准地监视一路、多路或所有选中的通道,当被监视的信号超出预置的阀值时,将产生中断。

由标准定时器(TIMx)和高级控制定时器(TIM1)产生的事件,可以分别内部级联到ADC的开始触发和注入触发,应用程序能使AD转换与时钟同步。

2.17 温度传感器

温度传感器产生一个随温度线性变化的电压,转换范围在2V < VDDA < 3.6V之间。温度传感器在内部被连接到ADC12_IN16的输入通道上,用于将传感器的输出转换到数字数值。

2.18 串行单线JTAG调试口(SWJ-DP)

内嵌ARM的SWJ-DP接口,这是一个结合了JTAG和串行单线调试的接口,可以实现串行单线调试接口或JTAG接口的连接。

JTAG的TMS和TCK信号分别与SWDIO和SWCLK共用引脚,TMS脚上的一个特殊的信号序列用于在JTAG-DP和SW-DP间切换。

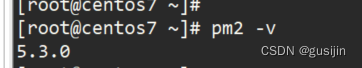

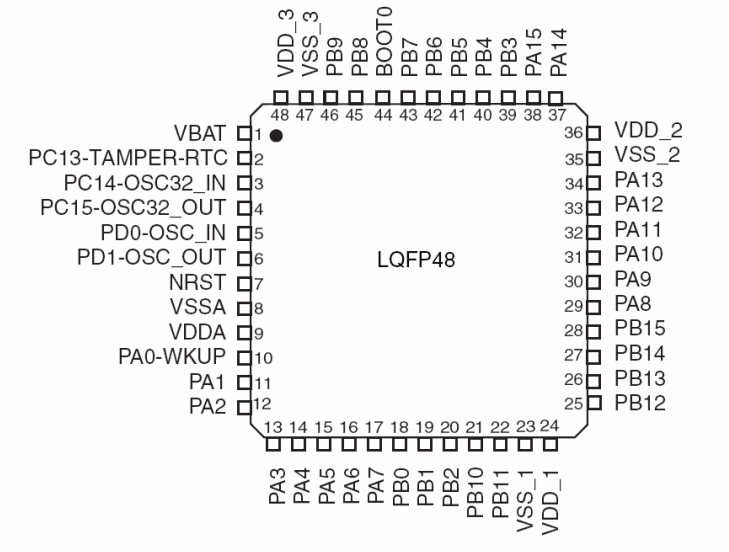

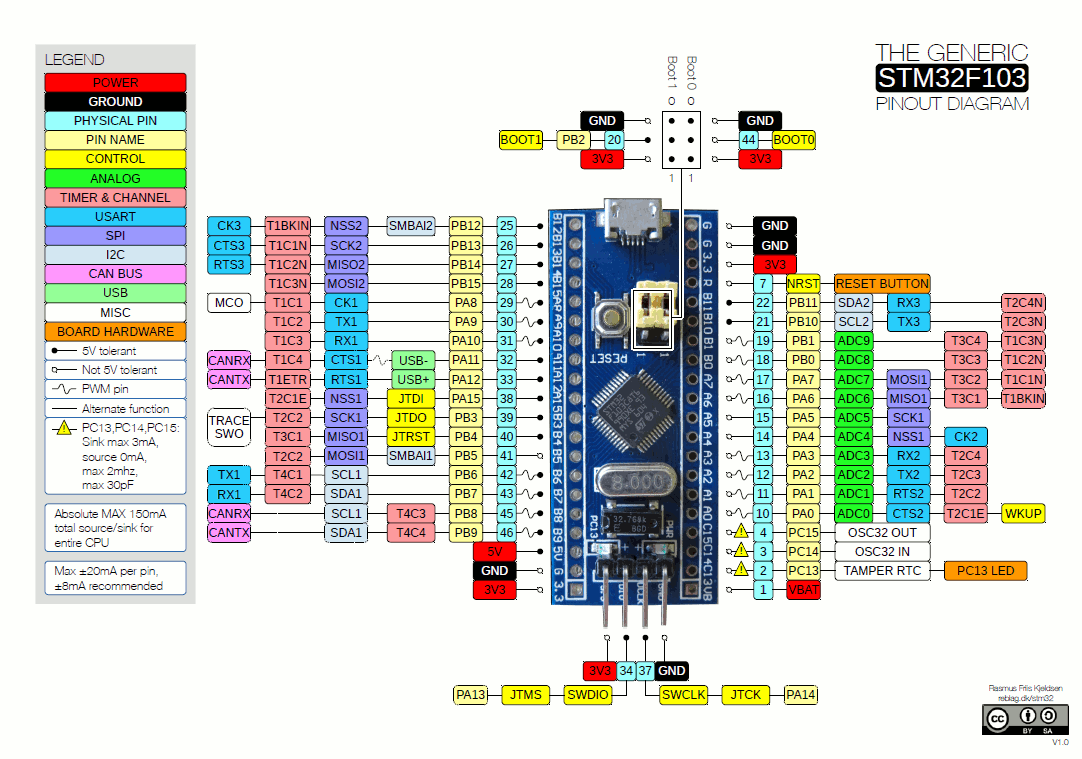

三、引脚定义

以stm32f103c8t6为例:

把 永 远 爱 你 写 进 诗 的 结 尾 ~