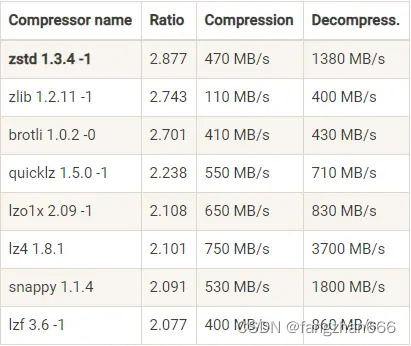

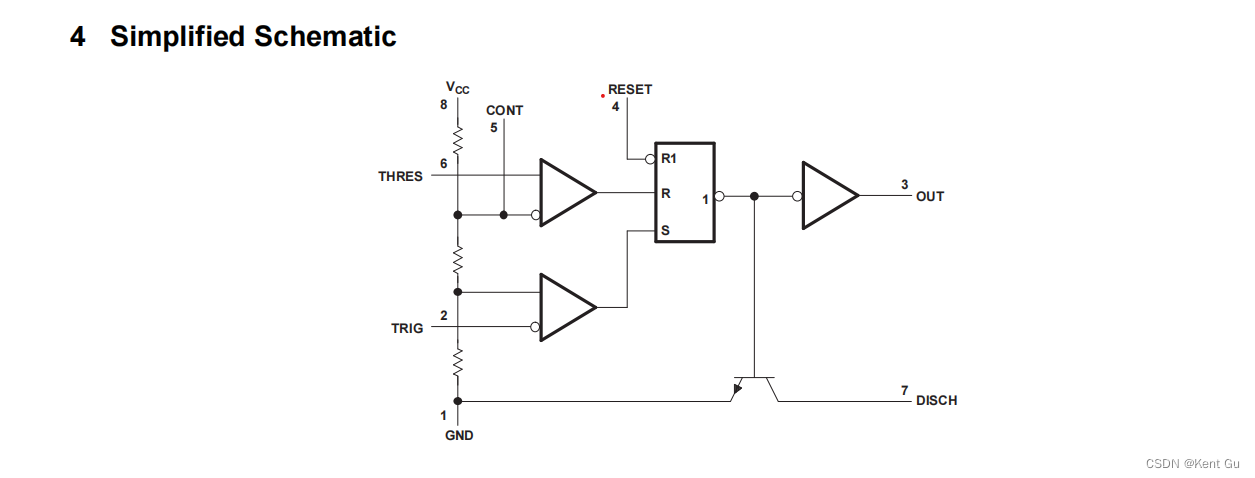

#1, Block & principle

1.1, The threshold and trigger levels normally are two- thirds and one-third, respectively, of VCC.(分压)

1.2,These levels can be altered by use of the control-voltage terminal.

When the trigger input falls below the trigger, the flip-flop is set. and the output goes high.

If threshold input is above the threshold level, the flip-flop is reset and the output is low.

The reset (RESET) input can override all other inputs and can be used to initiate a new timing cycle.When RESET goes low, the flip-flop is reset, and the output goes low.

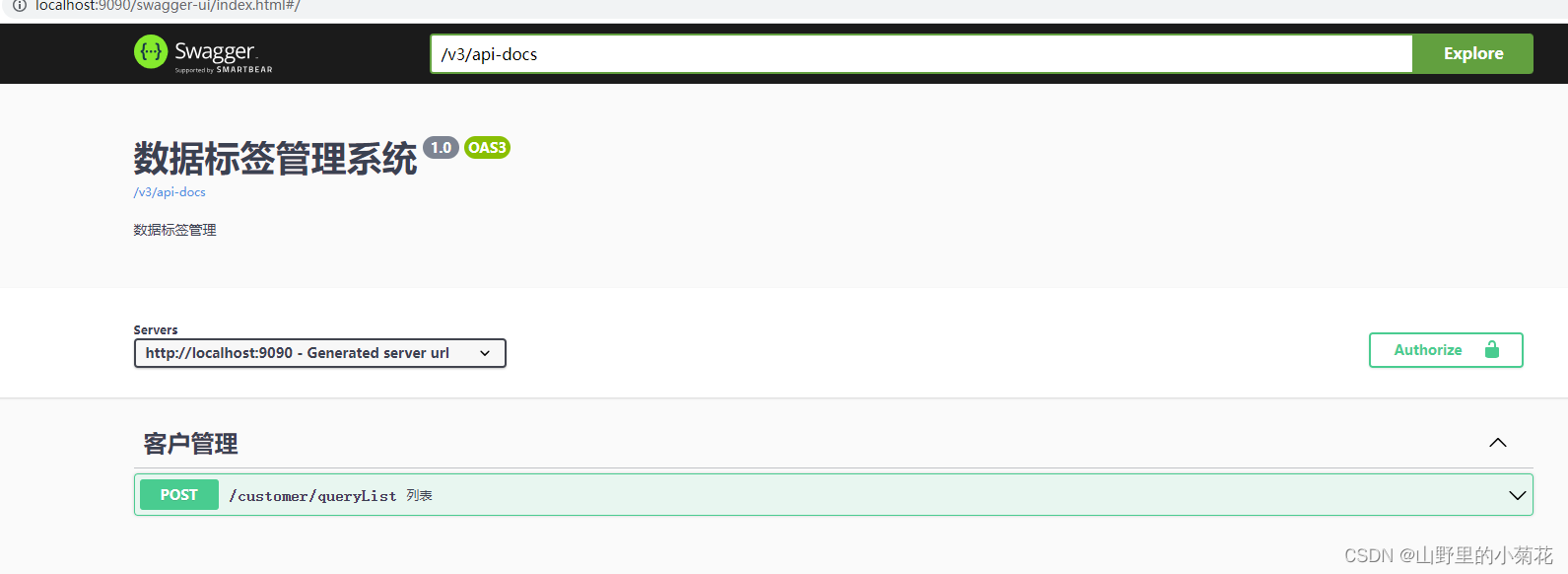

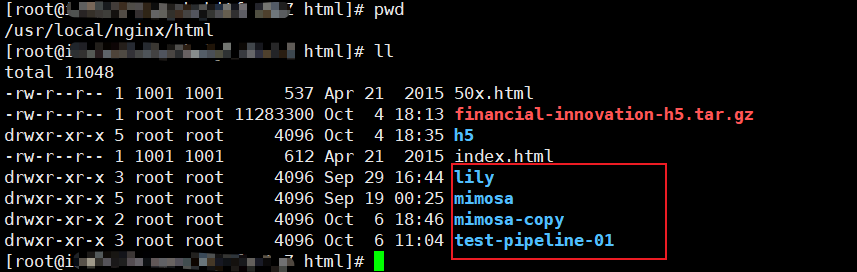

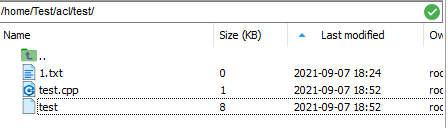

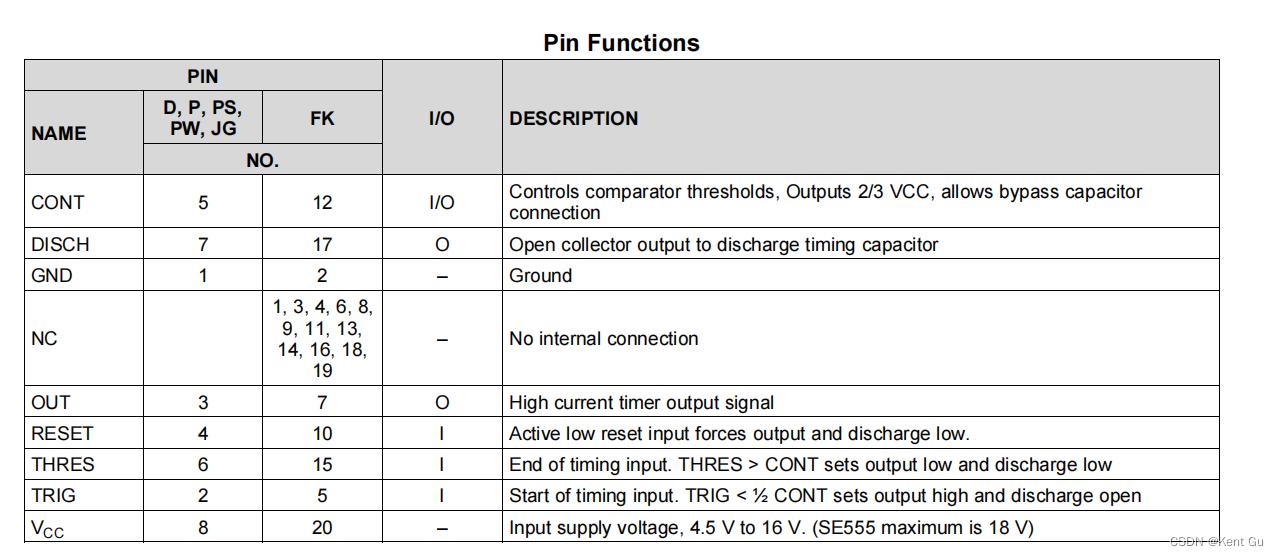

#2, Pin defintion

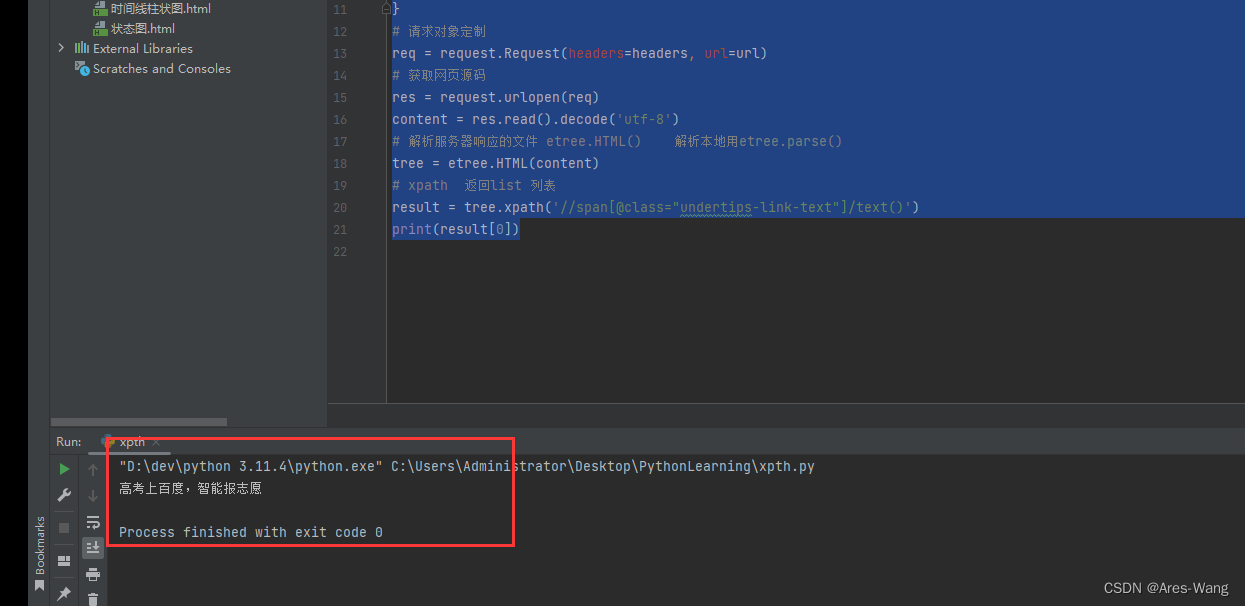

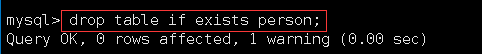

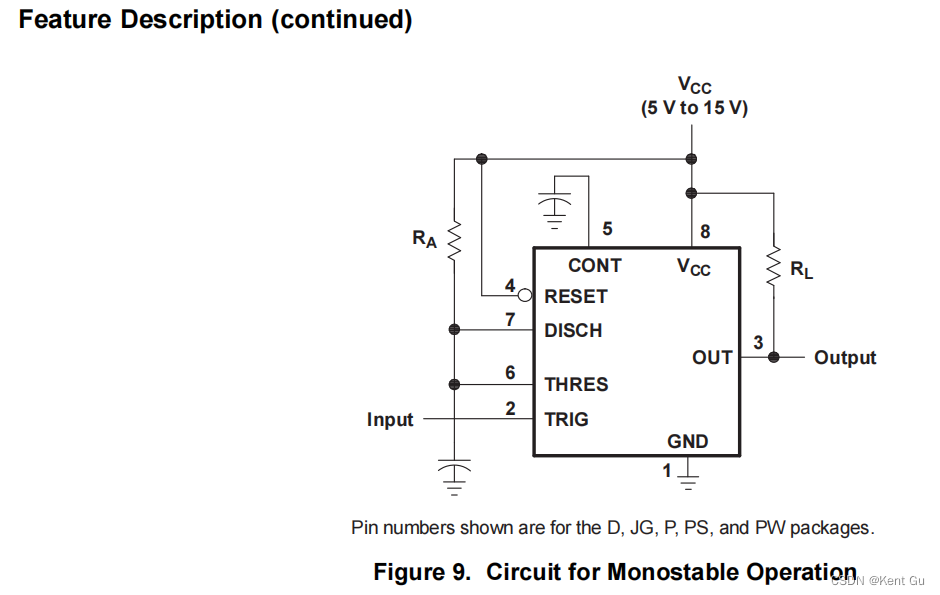

#3, Timer ctrl, should be in DISCH & THRES

the timed interval is controlled by a single external resistor and capacitor network.

#4, App circuit

Monostable operation is initiated when TRIG voltage falls below the trigger threshold. Once initiated, the sequence ends only if TRIG is high for at least 10 µs before the end of the timing interval. When the trigger is grounded, the comparator storage time can be as long as 10 µs, which limits the minimum monostable pulse width to 10 µs. Because of the threshold level and saturation voltage of Q1, the output pulse duration is approximately tw = 1.1RAC. Figure 11 is a plot of the time constant for various values of RA and C. The threshold

levels and charge rates both are directly proportional to the supply voltage, VCC. The timing interval is, therefore, independent of the supply voltage, so long as the supply voltage is constant during the time interval. Applying a negative-going trigger pulse simultaneously to RESET and TRIG during the timing interval discharges C and reinitiates the cycle, commencing on the positive edge of the reset pulse. The output is held low as long as the reset pulse is low. To prevent false triggering, when RESET is not used, it should be connected to VCC