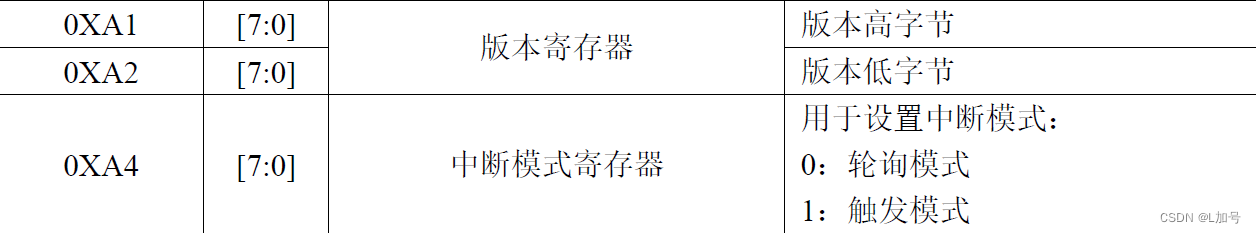

scan clocks的规则检查确保它们被正确的定义和操作。可以选择任意时钟规则检查的handling为error、warning、not或ignore。

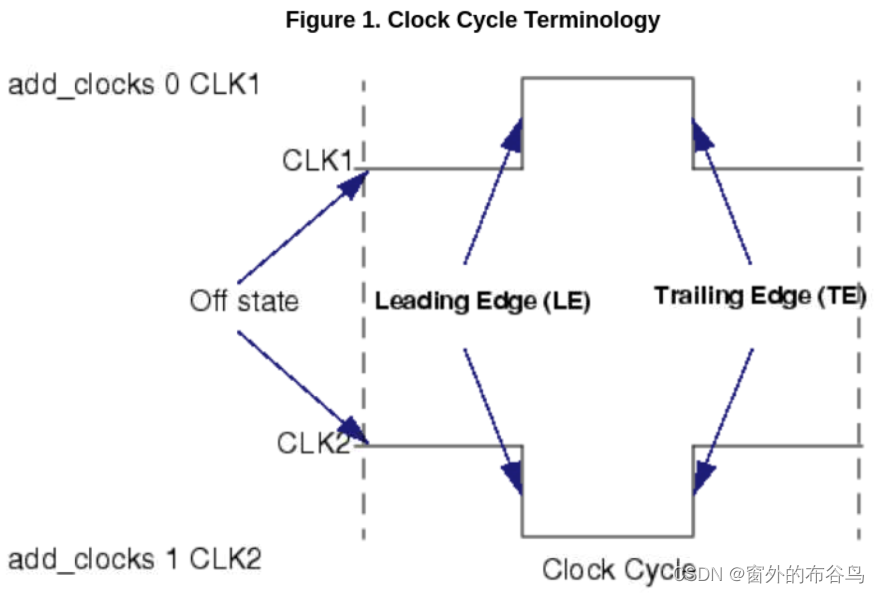

Clock Terminology

时钟规则信息包含两个重复发生的概念,为了更好地使用这些信息,应该理解以下概念。

Clock Signals

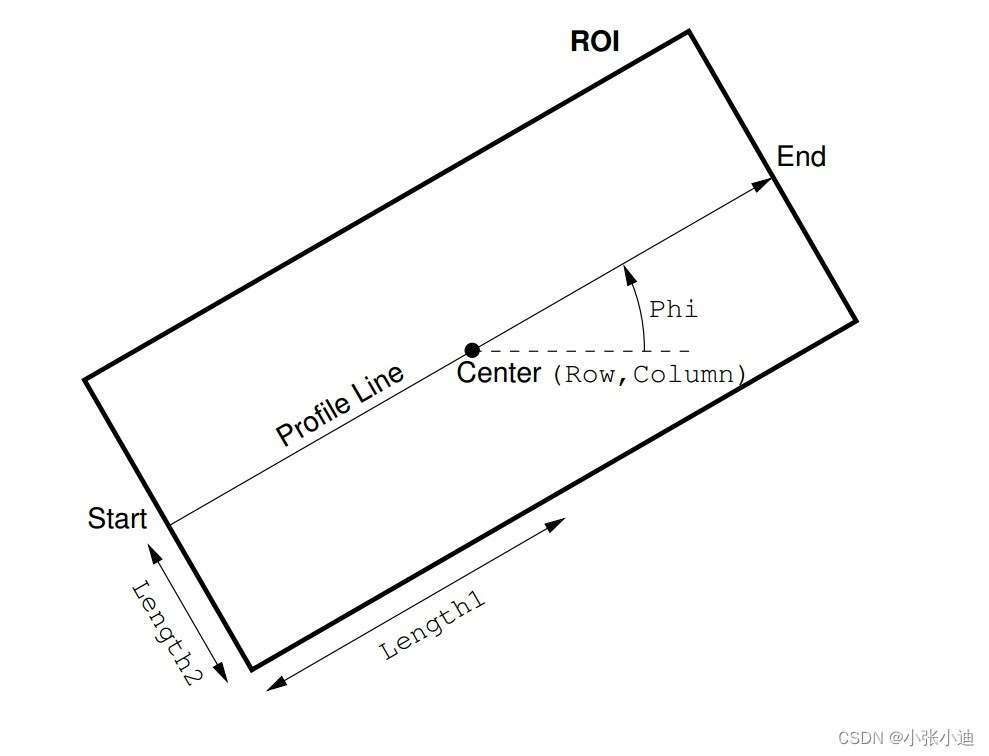

如果一个信号能够改变一个sequential element地状态,工具认为该信号是一个时钟,包括system clocks、sets和resets。当定义每个时钟的PI时(在setup mode下一个必须的步骤,使用add_clock命令或“analyze_control_signals -Auto_fix"),需要指定一个关键的信息是时钟的off state表现的pin value。这个定义产生两个重要的属于,如下图所示:

时钟从off状态变为on状态被认为是时钟的leading edge,而时钟从on状态变为off状态被认为是时钟的trailing edge。

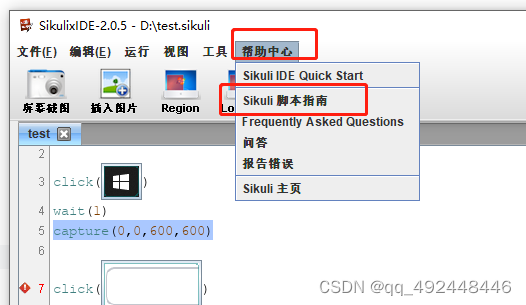

Clock Cones and Effect Cones

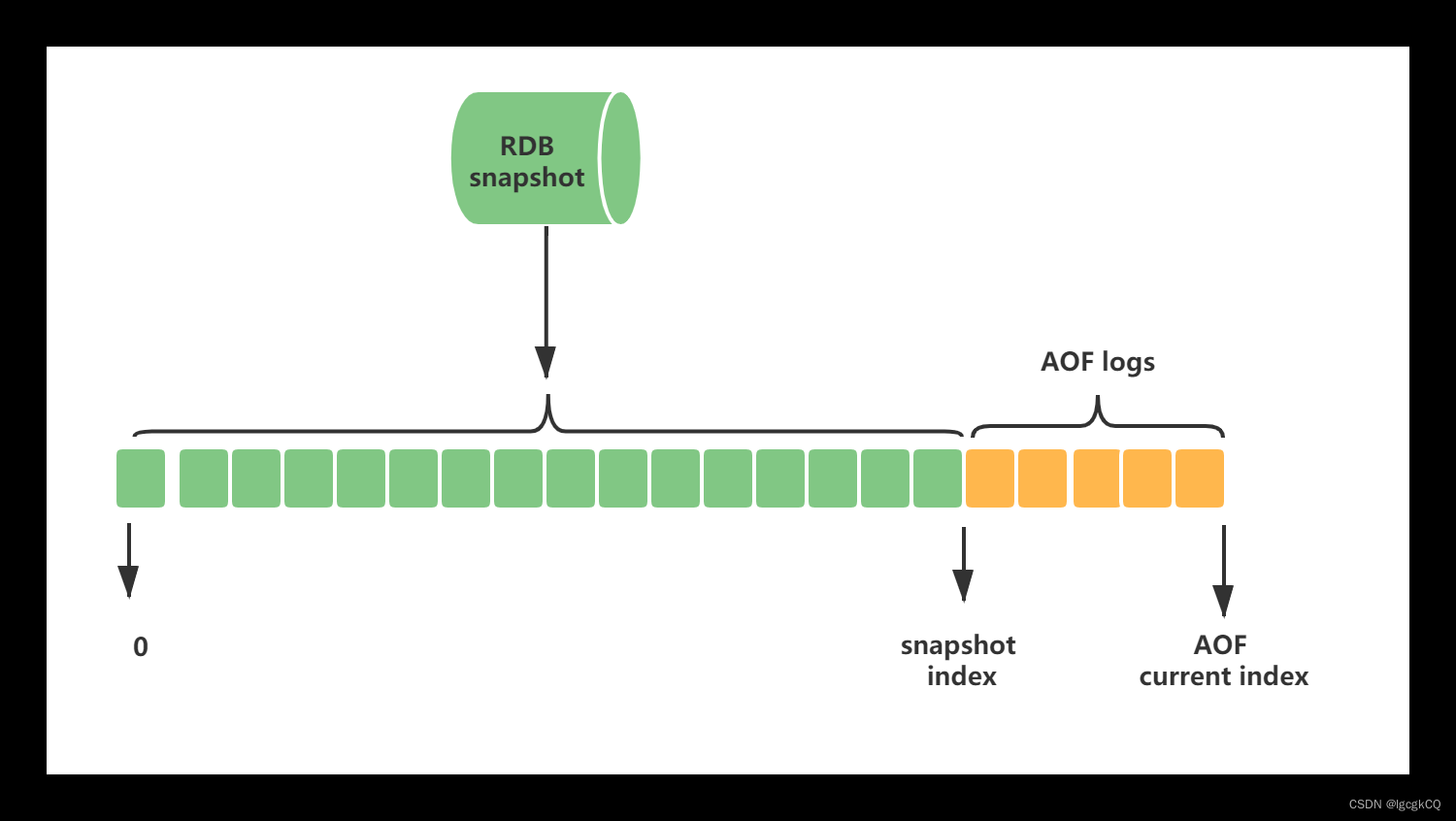

一个gate pin或output pin,当它通过组合逻辑门和transparent latches连接到时钟的PI上时,这些pin被认为在时钟信号的时钟锥中。

时钟锥是只通过组合逻辑和TLAs的时钟信号的fanout。下图中,Pins B、C、CLK和CLK2_INV都在CLK2的时钟锥中。