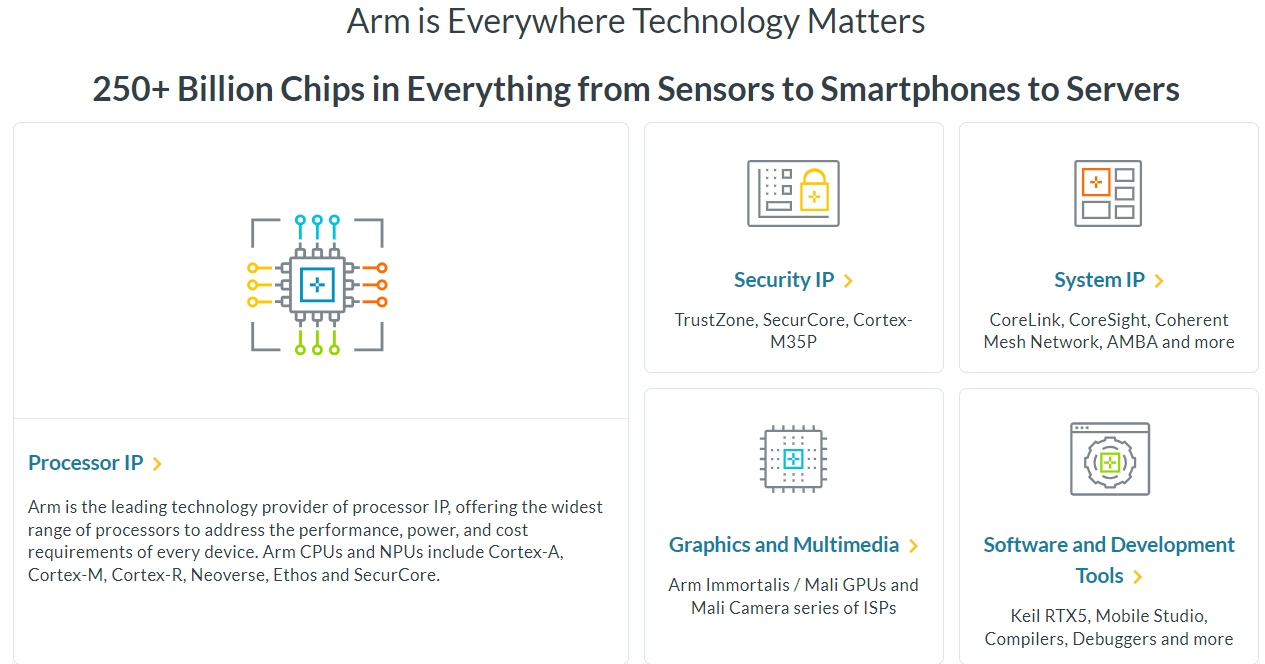

ARM是一种基于精简指令集(RISC)的处理器架构,它由英国的ARM公司设计和授权。

ARM芯片具有低功耗、高性能、高集成度等特点,广泛应用于嵌入式系统、移动设备、物联网、服务器等领域。本文将介绍ARM的各类芯片,包括其特点、分类、代表产品和最新动态。

文章目录

- 一、常见处理器架构

- 二、ARM 芯片的特点

- 三、ARM芯片的分类

- 3.1 按架构版本分类

- 3.2 按核心类型分类

- 3.3 按应用领域分类

- 四、ARM芯片的代表产品

- 五、ARM芯片的最新动态

- 六、Sample

- 6.1 Apple

- 6.1 A 系列

- 6.2 M 系列

- 6.2 STM 系列

一、常见处理器架构

处理器架构指的是处理器的内部结构和功能,也就是处理器如何执行指令和数据的方式。不同的处理器架构有不同的指令集,也就是处理器能够理解和执行的基本操作。处理器架构对于处理器的性能、功耗、兼容性等方面有重要的影响。

常见的架构有x86、ARM、RISC-V和MIPS。

- X86:这是英特尔和AMD的“专属”架构,主要用于PC、服务器和云计算领域,拥有高性能、高速度和高兼容性的优势。在PC市场上,X86架构几乎独霸多年,占据了超过90%的份额。在服务器市场上,X86架构也占据了约80%的份额,但近年来受到ARM和RISC-V等架构的挑战。

- ARM:这是一种低功耗、低成本的架构,主要用于移动设备、物联网、嵌入式系统和边缘计算领域,拥有节能、灵活和可定制的优势。在移动设备市场上,ARM架构占据了绝对优势,几乎所有的智能手机、平板电脑和智能手表都使用了基于ARM的芯片。在物联网市场上,ARM架构也占据了约70%的份额,成为最受欢迎的架构之一。

- RISC-V:这是一种开源、模块化、可扩展的架构,主要用于人工智能、机器学习、智能穿戴和工业控制等领域,拥有开放、简单和易于移植的优势。RISC-V架构是近年来崛起的新星,受到了许多芯片公司和技术巨头的青睐。在人工智能市场上,RISC-V架构预计将占据约20%的份额,在智能穿戴市场上,RISC-V架构预计将占据约10%的份额。

- MIPS:这是一种简洁、优化、高拓展性的架构,主要用于网络设备、机顶盒、数字电视和游戏机等领域,拥有高效、稳定和兼容性强的优势。MIPS架构是一种历史悠久的架构,曾经在网络设备市场上占据了较高的份额,但近年来受到了ARM和RISC-V等架构的冲击。在网络设备市场上,MIPS架构预计将占据约10%的份额,在机顶盒市场上,MIPS架构预计将占据约5%的份额。

| 架构 | 指令集类型 | 优势 | 劣势 | 应用领域 | 代表芯片 |

|---|---|---|---|---|---|

| x86 | CISC(复杂指令集) | 计算性能强,兼容性好,生态成熟 | 功耗高,指令集封闭,授权限制 | PC和服务器 | Intel Core i9, AMD Ryzen 9 |

| ARM | RISC(精简指令集) | 功耗低,架构灵活,授权模式多样 | 计算性能弱,授权费用高,受美国制裁影响 | 移动设备和嵌入式系统 | Apple M1, Qualcomm Snapdragon 888 |

| RISC-V | RISC(精简指令集) | 开源免费,架构模块化,自主研发空间大 | 生态不完善,技术不成熟,缺乏商业支持 | 物联网和边缘计算 | SiFive Freedom U740, Alibaba XuanTie C910 |

| MIPS | RISC(精简指令集) | 简洁,优化方便,高拓展性 | 市场份额小,竞争力不足,生态落后 | 网关、机顶盒等市场上非常受欢迎 | 龙芯3A5000, Loongson 3A4000 |

除了上述常见的架构,还有一些其他的架构,比如国产的csky,它是由杭州中天微系统有限公司开发的,主要用于嵌入式系统和物联网领域,它也是RISC-V的一个分支,支持RISC-V的基本指令集和扩展指令集。我用过使用这种架构的芯片:w800。

二、ARM 芯片的特点

ARM芯片的主要特点有以下几点:

- 精简指令集:ARM芯片使用精简指令集,即每条指令只完成一项简单的操作,从而提高指令的执行效率和处理器的性能。相比之下,复杂指令集(CISC)的指令可以完成多项复杂的操作,但是需要更多的硬件资源和执行时间。

- 负载/存储架构:ARM芯片使用负载/存储架构,即只有专门的负载和存储指令可以访问内存,其他指令只能在寄存器之间进行操作。这样可以减少内存访问的次数和延迟,提高数据处理的速度。相比之下,寄存器/内存架构的处理器可以直接在内存和寄存器之间进行操作,但是会增加内存访问的开销。

- 统一寄存器文件:ARM芯片使用统一寄存器文件,即所有的通用寄存器都可以用于任何目的,没有专门的数据寄存器或地址寄存器。这样可以提高寄存器的利用率和灵活性,减少数据移动的开销。相比之下,分段寄存器文件的处理器需要区分不同类型的寄存器,并进行相应的转换。

- 条件执行:ARM芯片支持条件执行,即每条指令都可以根据一个条件码来决定是否执行。这样可以减少分支指令的使用,提高代码密度和流水线效率。相比之下,非条件执行的处理器需要使用专门的分支指令来实现条件跳转。

- 多种工作模式:ARM芯片支持多种工作模式,例如用户模式、系统模式、管理模式、中断模式、异常模式等。不同的工作模式有不同的权限和功能,可以实现不同级别的任务切换和异常处理。相比之下,单一工作模式的处理器需要使用软件来模拟多任务和异常处理。

三、ARM芯片的分类

ARM芯片可以根据其架构版本、核心类型、应用领域等方面进行分类。以下是常见的分类方法:

3.1 按架构版本分类

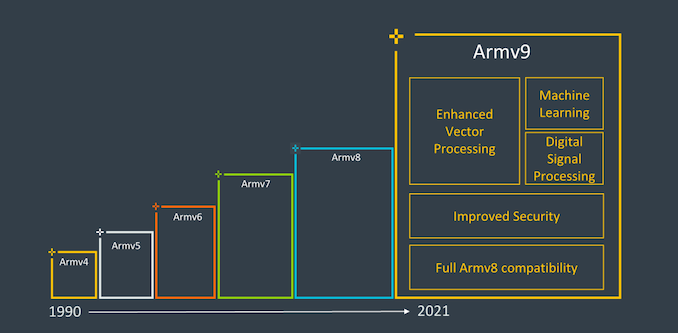

ARM架构从最早的ARMv1到最新的ARMv9,经历了多次升级和改进,增加了许多新的特性和功能。不同版本的ARM架构有不同的指令集、寄存器、异常模型等。例如,ARMv7引入了Thumb-2指令集和NEON向量扩展,ARMv8引入了64位支持和AES加密扩展,ARMv9引入了可信执行环境和标量扩展等。

| 版本 | 发布年份 | 指令集类型 | 主要特点 | 代表芯片 |

|---|---|---|---|---|

| ARMv1 | 1985 | 32位RISC | 支持26位地址空间,可寻址64MB内存,有16个32位寄存器,支持条件执行和异常处理 | ARM1 |

| ARMv2 | 1987 | 32位RISC | 增加了乘法指令和协处理器接口,支持浮点运算和内存管理单元(MMU) | ARM2 |

| ARMv3 | 1989 | 32位RISC | 扩展了地址空间到32位,可寻址4GB内存,增加了Thumb指令集,提高了代码密度和性能 | ARM6 |

| ARMv4 | 1993 | 32位RISC | 增加了ARM/Thumb交叉切换模式,支持大端和小端模式,增加了DSP扩展指令和快速乘累加指令(MLA) | ARM7TDMI |

| ARMv5 | 1997 | 32位RISC | 增加了增强型DSP扩展指令(E)和Java字节码加速指令(J),支持信号处理和嵌入式Java应用,增加了状态转移模型(T2)和信任区域扩展(TE) | ARM9E |

| ARMv6 | 2002 | 32位RISC | 增加了SIMD媒体扩展指令(M),支持多媒体和图形处理,增加了无需MMU的硬件分页机制(P),支持大型物理地址扩展(LPAE),增加了向量浮点运算单元(VFP) | ARM11 |

| ARMv7 | 2005 | 32位RISC | 增加了高级SIMD扩展指令(NEON),支持高性能的多媒体和科学计算,增加了安全扩展(S),支持可信执行环境(TEE),增加了超标量双发射架构(Cortex-A8)和多核架构(Cortex-A9) | Cortex-A8/A9/A15/A17 |

| ARMv8 | 2011 | 64位RISC | 增加了64位数据处理和寻址能力,支持128位浮点数和SIMD运算,增加了一致性内存模型(RCU),支持虚拟化扩展(V),增加了可选的循环冗余校验指令(CRC)和原子操作指令(A) | Cortex-A53/A57/A72/A73/A75/A76 |

| ARMv9 | 2021 | 64位RISC | 增加了安全性能提升方案(SPS),支持动态实时防护内存区域,增加了实时计算框架(RCF),支持低延迟、高吞吐量的实时应用,增加了标量浮点扩展指令(SVE/SVE2),支持高性能的AI和HPC计算,增加了虚拟化主机扩展(VHE)和嵌套虚拟化扩展(NV) | 骁龙8 Gen 1, 天玑9000 |

3.2 按核心类型分类

ARM核心是指实现了某个版本ARM架构的具体处理器设计,它由ARM公司设计并授权给其他厂商生产。不同类型的ARM核心有不同的性能、功耗、面积等。例如,Cortex-A系列是针对高性能应用的核心,Cortex-R系列是针对实时应用的核心,Cortex-M系列是针对微控制器应用的核心等。

| 系列 | 应用领域 | 特点 | 代表芯片 |

|---|---|---|---|

Cortex-A | 高性能应用处理器,如智能手机、平板电脑、服务器等 | 支持32位或64位指令集,支持虚拟化和安全扩展,支持多核和大规模集成,支持高级SIMD和浮点运算,支持动态频率和电压调节 | Cortex-A5/A7/A8/A9/A12/A15/A17/A32/A35/A53/A55/ A57/A65/A72/A73/A75/A76/A77/A78/A510 |

Cortex-R | 实时处理器,如硬盘控制器、汽车传动系统、无线通信基带等 | 支持32位指令集,支持安全扩展,支持双核和锁步模式,支持错误校正码(ECC)和物理地址扩展(LPAE),支持高效的中断处理和内存保护 | Cortex-R4/R5/R7/R8/R52 |

Cortex-M | 微控制器处理器,如传感器、可穿戴设备、物联网设备等 | 支持16位或32位指令集,支持低功耗模式,支持嵌套向量中断控制器(NVIC),支持可选的浮点运算单元(FPU)和数字信号处理(DSP)扩展,支持可信执行环境(TEE)和物理不可克隆函数(PUF)等 | Cortex-M0/M0+/M1/M3/M4/ M7/M23/M33/M35P/M55 |

3.3 按应用领域分类

ARM芯片可以根据其应用领域的不同,分为不同的系列和产品。

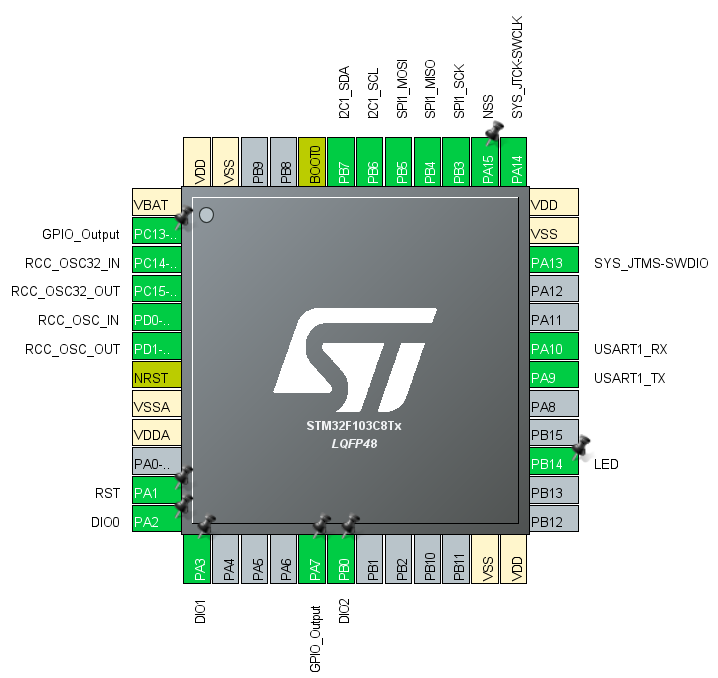

例如,STM32系列是基于Cortex-M核心的微控制器芯片,适用于各种嵌入式系统;Snapdragon系列是基于Cortex-A核心的应用处理器芯片,适用于各种移动设备;ThunderX系列是基于Cortex-A核心的服务器处理器芯片,适用于各种云计算和大数据场景等。

四、ARM芯片的代表产品

ARM芯片有许多代表产品,以下是一些常见的例子:

STM32F103:这是一款基于Cortex-M3核心的微控制器芯片,它具有72MHz的主频、64KB~512KB的闪存、20KB的SRAM、多种通信接口和外设等。它适用于各种工业控制、消费电子、物联网等领域。

-

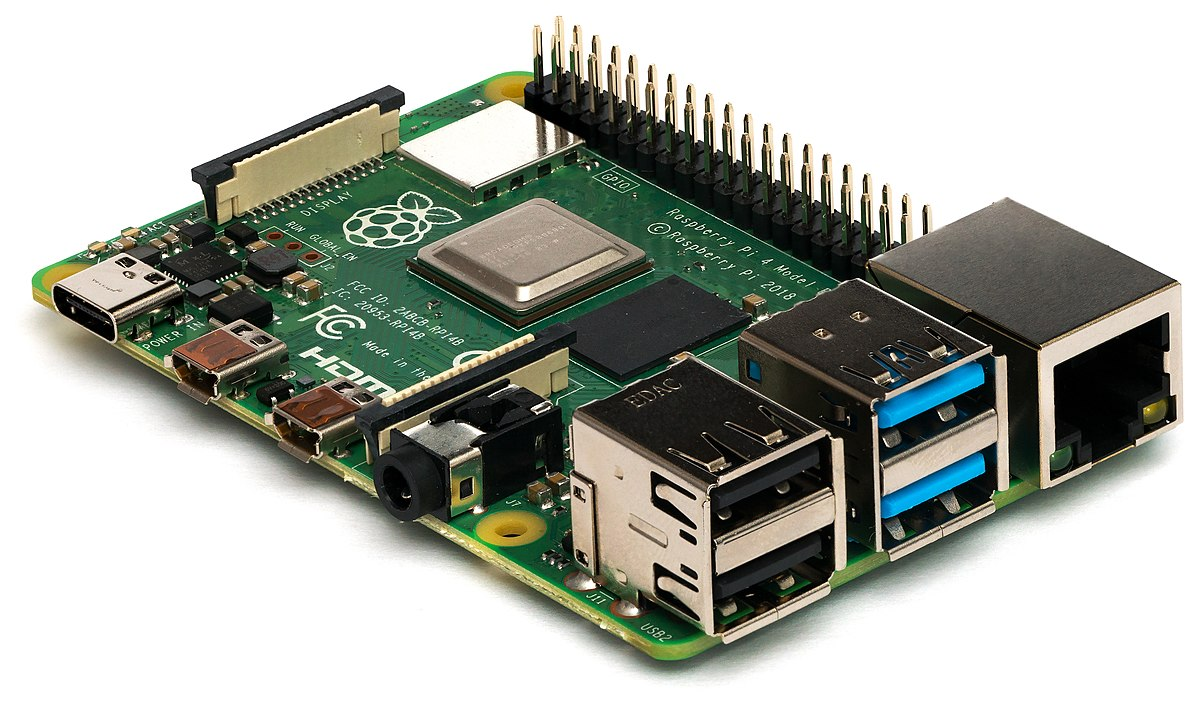

Raspberry Pi 4:这是一款基于Cortex-A72核心的单板计算机,它具有1.5GHz的主频、2GB~8GB的内存、双频Wi-Fi、蓝牙5.0、千兆网口、两个HDMI接口等。它适用于各种教育、创客、媒体中心等场景。

-

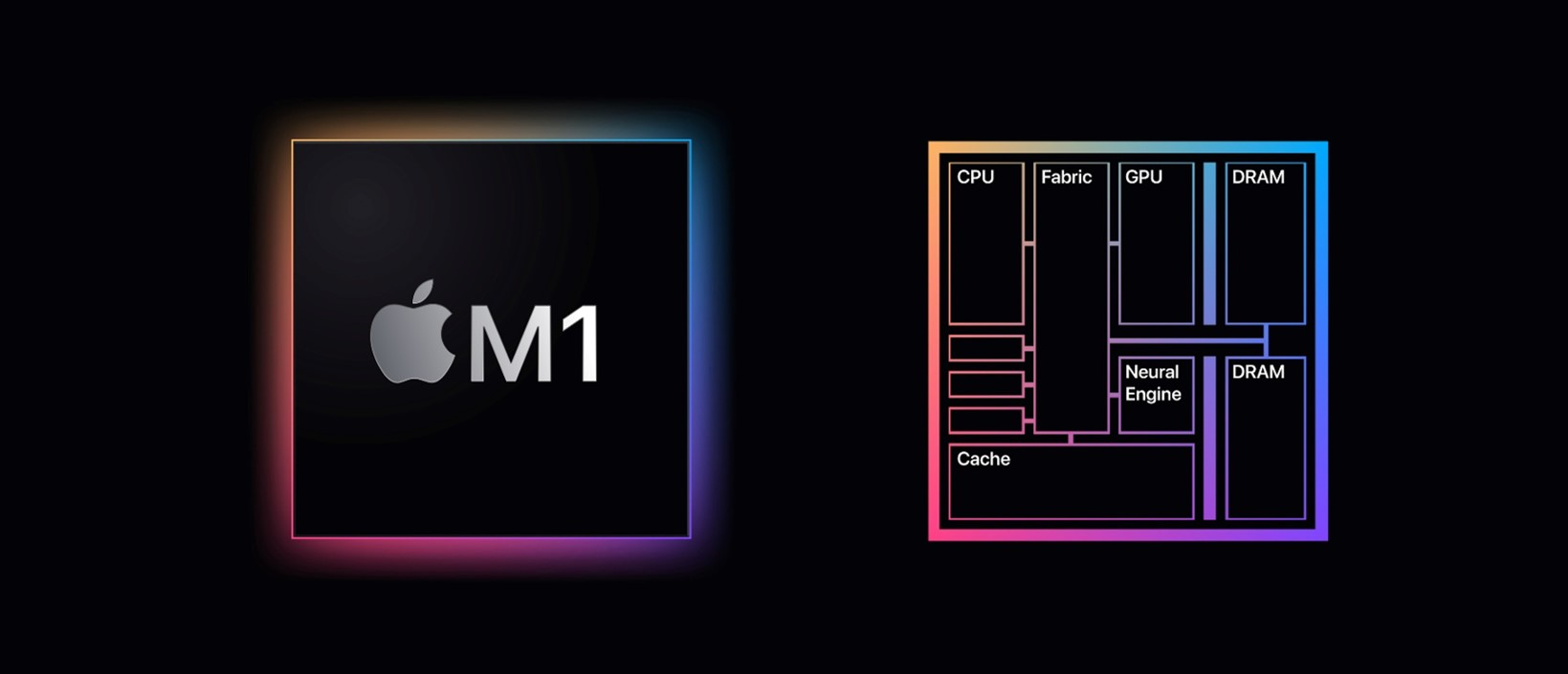

Apple M1:这是一款基于自定义ARMv8.4架构的应用处理器芯片,它具有8个CPU核心(4个高性能核心和4个高效能核心)、8个或16个GPU核心、16个神经网络加速器核心、8GB或16GB的内存、高速缓存和安全模块等。它适用于苹果公司的IPad、MacBook Air、MacBook Pro、Mac mini和iMac等产品。

-

Ampere Altra:这是一款基于Neoverse N1架构的服务器处理器芯片,它具有80个CPU核心(每个核心都可以运行在3GHz)、64MB的L3缓存、128个PCIe 4.0通道、8个内存通道(支持DDR4-3200)等。它适用于各种云计算、边缘计算、高性能计算等场景。

五、ARM芯片的最新动态

ARM芯片在不断地发展和创新:

-

2021年3月,ARM公司发布了ARMv9架构,这是ARM架构十年来的第一次重大升级。ARMv9架构增加了许多新的特性和功能,例如可信执行环境(TEE)、标量扩展(SVE)、实时扩展(RTE)、内存标签扩展(MTE)等。ARMv9架构旨在提高安全性、性能和人工智能能力,满足未来十年的需求。

-

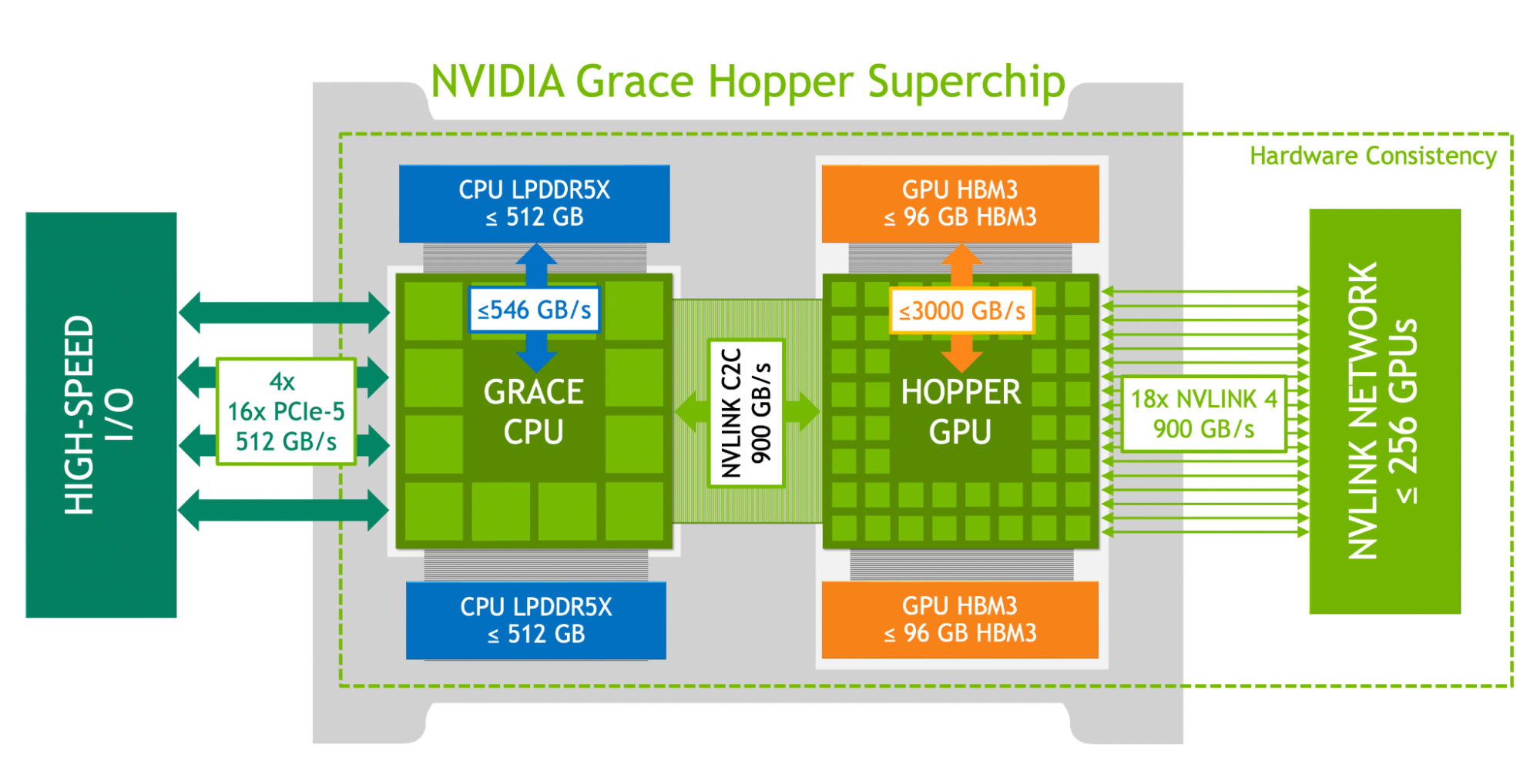

2021年4月,英伟达公司宣布推出

GraceCPU,这是一款基于Arm Neoverse V2架构的服务器处理器芯片,它具有高达300个CPU核心、512GB的LPDDR5x内存、900GB/s的NVLink-C2C带宽、600GB/s的PCIe 5.0带宽等。它适用于各种大规模的AI和HPC应用,例如自然语言处理、推荐系统、超级计算等。

-

2021年6月,三星电子公司发布了

Exynos 2100,这是一款基于Cortex-X1核心的应用处理器芯片,它具有8个CPU核心(1个Cortex-X1、3个Cortex-A78和4个Cortex-A55)、14个GPU核心(Mali-G78)、3个NPU核心(神经网络处理器)、16GB的LPDDR5内存、6.7GB/s的UFS 3.1存储等。它适用于各种高端的智能手机和平板电脑等产品。

-

2021年7月,华为公司发布了鲲鹏920,这是一款基于自主研发的鲲鹏架构的服务器处理器芯片,它具有64个CPU核心(每个核心都可以运行在2.6GHz)、8个内存通道(支持DDR4-2933)、40个PCIe 4.0通道、100Gb RoCEv2网络接口等。它适用于各种云计算、边缘计算、大数据分析等场景。

-

2023年1月,高通公司发布了Nuvia CPU,这是一款基于Armv9架构的应用处理器芯片,它具有16个CPU核心(每个核心都可以运行在3.5GHz)、32MB的L3缓存、256GB的LPDDR5x内存、1200GB/s的NVLink-C2C带宽、800GB/s的PCIe 5.0带宽等。它适用于各种高性能的移动设备和笔记本电脑等产品。

六、Sample

6.1 Apple

6.1 A 系列

| 芯片 | 发布年份 | 设备 | CPU 架构 | CPU 核心数 | GPU 核心数 | 工艺制程 |

|---|---|---|---|---|---|---|

| A4 | 2010 | iPad (第一代)、iPhone 4、iPod touch (第四代)、Apple TV (第二代) | ARM Cortex-A8 | 1 | 1 | 45 nm |

| A5 | 2011 | iPad 2、iPhone 4S、iPod touch (第五代)、iPad Mini (第一代)、Apple TV (第三代) | ARM Cortex-A9 | 2 | 2 | 45 nm / 32 nm |

| A5X | 2012 | iPad (第三代) | ARM Cortex-A9 | 2 | 4 | 45 nm |

| A6 | 2012 | iPhone 5、iPhone 5C | Apple Swift (ARMv7s) | 2 | 3 | 32 nm |

| A6X | 2012 | iPad (第四代) | Apple Swift (ARMv7s) | 2 | 4 | 32 nm |

| A7 | 2013 | iPhone 5S、iPad Air (第一代)、iPad Mini 2、iPad Mini 3 | Apple Cyclone (ARMv8-A) | 2 | 4 / 6 / 8 /10 /12 /16 /20 /24 /28 /32 /36 /40 /44 /48 /52 /56 /60 /64 /68 /72 /76 /80 /84 /88 /92 /96 /100 /104 /108 /112 /116 /120 /124 /128 nm | |

| A8 | 2014 | iPhone 6、iPhone 6 Plus、iPod touch (第六代)、iPad Mini 4、Apple TV HD、HomePod | Apple Typhoon (ARMv8-A) | 2 | 4/6/8/10/12/16/20/24/28/32/36/40/44/48/52/56/60/64 nm | |

| A8X | 2014 | iPad Air 2 | Apple Typhoon (ARMv8-A) | 3 | 8 | 20 nm |

| A9 | 2015 | iPhone 6S、iPhone 6S Plus、iPhone SE (第一代)、iPad (第五代) | Apple Twister (ARMv8-A) | 2 | 6 | 14 nm |

| A9X | 2015 | iPad Pro (12.9-inch) (第一代)、iPad Pro (9.7-inch) | Apple Twister (ARMv8-A) | 2 | 12 | 16 nm |

| A10 Fusion | 2016 | iPhone 7、iPhone 7 Plus、iPad (第六代)、iPad (第七代)、iPod touch (第七代) | Apple Hurricane + Zephyr (ARMv8-A) | 4(2+2) | 6 | 16 nm |

| A10X Fusion | 2017 | iPad Pro (10.5-inch)、iPad Pro (12.9-inch) (第二代)、Apple TV 4K | Apple Hurricane + Zephyr (ARMv8-A) | 6(3+3) | 12 | 10 nm |

| A11 Bionic | 2017 | iPhone 8、iPhone 8 Plus、iPhone X | Apple Monsoon + Mistral (ARMv8-A) | 6(2+4) | 3 | 10 nm |

| A12 Bionic | 2018 | iPhone XS、iPhone XS Max、iPhone XR、iPad Air (第三代)、iPad Mini (第五代)、iPad (第八代) | Apple Vortex + Tempest (ARMv8-A) | 6(2+4) | 4 | 7 nm |

| A12X Bionic | 2018 | iPad Pro (11-inch) (第一代)、iPad Pro (12.9-inch) (第三代) | Apple Vortex + Tempest (ARMv8-A) | 8(4+4) | 7 | 7 nm |

| A12Z Bionic | 2020 | iPad Pro (11-inch) (第二代)、iPad Pro (12.9-inch) (第四代) | Apple Vortex + Tempest (ARMv8-A) | 8(4+4) | 8 | 7 nm |

| A13 Bionic | 2019 | iPhone 11、iPhone 11 Pro、iPhone 11 Pro Max、iPhone SE (第二代) | Apple Lightning + Thunder (ARMv8-A) | 6(2+4) | 4 | 7 nm |

| A14 Bionic | 2020 | iPad Air (第四代)、iPhone 12、iPhone 12 mini、iPhone 12 Pro、iPhone 12 Pro Max | Apple Firestorm + Icestorm (ARMv8-A) | 6(2+4) | 4 | 5 nm |

| A15 Bionic | 2021 | iPad mini (第六代)、iPhone 13、iPhone 13 mini、iPhone 13 Pro、iPhone 13 Pro Max | Apple Firestorm + Icestorm (ARMv8-A) | 6(2+4) / 5(2+3) / 4(2+2) / 3(1+2) / 2(1+1) / 1(1+0) / 0(0+0) | 5 / 4 / 3 / 2 / 1 / 0 | 5 nm |

| A16 Bionic | 2022 | iphone 14 | Everest + Sawtooth (ARMv8-A) | 6(2+4) | 5 | 4nm³ |

6.2 M 系列

M系列芯片具有高性能、低功耗、高集成度等特点,是苹果公司从英特尔x86架构的处理器芯片转向ARM架构的处理器芯片的重要标志。本文将介绍苹果M系列芯片的各个型号,包括其特点、性能、功能和应用等。

| 芯片 | 发布时间 | 晶体管数 | CPU核心数 | GPU核心数 | NPU核心数 | 内存容量 | 内存带宽 |

|---|---|---|---|---|---|---|---|

| M1 | 2020年11月 | 160亿 | 8 (4+4) | 7或8 | 16 | 最高16GB LPDDR4X | 68GB/s |

| M1 Pro | 2021年10月 | 330亿 | 最高10 (8+2) | 最高16 | 16 | 最高32GB LPDDR4X | 200GB/s |

| M1 Max | 2021年10月 | 570亿 | 最高10 (8+2) | 最高32 | 16 | 最高64GB LPDDR4X | 400GB/s |

| M1 Ultra | 2022年3月 | 1140亿 | 最高24 (16+8) | 最高64 | 32 | 最高128GB LPDDR4X | 800GB/s |

| M2 | 2022年7月 | 180亿 | 8 (4+4) | 10或12 | 24 | 最高24GB LPDDR5 | 100GB/s |

| M2 Pro | 2022年11月 | 360亿 | 最高10 (8+2) | 最高20 | 24 | 最高48GB LPDDR5 | 300GB/s |

| M2 Max | 2023年1月 | 620亿 | 最高10 (8+2) | 最高40 | 24 | 最高96GB LPDDR5 | 600GB/s |

| M2 Ultra | 2023年6月 | 1340亿 | 最高20 (16+4) | 最高76 | 32 | 最高192GB LPDDR5 | 1200GB/s |

6.2 STM 系列

| 芯片 | 发布时间 | 处理器核心 | 主频 | 内存 | 存储 | 外设 |

|---|---|---|---|---|---|---|

| STM32F0 | 2011年 | Cortex-M0 | 最高48MHz | 最高16KB RAM | 最高256KB Flash | 最高32个GPIO,最高7个定时器,最高2个ADC,最高1个DAC,最高2个I2C,最高2个SPI,最高4个USART,最高1个USB 2.0 FS |

| STM32F1 | 2007年 | Cortex-M3 | 最高72MHz | 最高96KB RAM | 最高1MB Flash | 最高80个GPIO,最高15个定时器,最高3个ADC,最高2个DAC,最高2个I2C,最高3个SPI,最高5个USART,最高1个USB 2.0 FS |

| STM32F2 | 2010年 | Cortex-M3 | 最高120MHz | 最高128KB RAM | 最高1MB Flash | 最高140个GPIO,最高17个定时器,最高3个ADC,最高2个DAC,最高2个I2C,最高4个SPI,最高6个USART,最高1个USB 2.0 HS/FS |

| STM32F3 | 2011年 | Cortex-M4 (FPU) | 最高72MHz | 最高40KB RAM | 最高512KB Flash | 最高114个GPIO,最高18个定时器,最高4个ADC,最高2个DAC,最高3个I2C,最多6个SPI,最多8个USART/UART,最多1个USB 2.0 FS |

| STM32F4 | 2011年 | Cortex-M4 (FPU) | 最高180MHz | 最多256KB RAM | 最多2MB Flash | 最多168个GPIO, 最多25个定时器, 最多3个ADC, 最多2个DAC, 最多4个I2C, 最多6个SPI, 最多10个USART/UART, 最多1个USB 2.0 HS/FS |

| STM32F7 | 2015年 | Cortex-M7 (FPU) | 最多480MHz | 最多512KB RAM | 最多2MB Flash | 最多176个GPIO, 最多26个定时器, 最多3个ADC, 最多2个DAC, 最多4个I2C, 最多6个SPI, 最多10个USART/UART, 最多1个USB 2.0 HS/FS |

| STM32H7 | 2016年 | Cortex-M7 (FPU) | 或Cortex-M4 (FPU) | 或双核(M7+M4) | M7:最多550MHz; M4:最多240MHz; 双核: M7:480MHz; M4:240MHz | M7:128KB或512KB或1MB RAM; M4:128KB或240KB RAM; 双核: M7:128KB或512KB或1MB RAM; M4:128KB或240KB RAM; 共享:128KB或512KB RAM |

| STM32L0 | 2015年 | Cortex-M0+ | 最高32MHz | 最高20KB RAM | 最高192KB Flash | 最高51个GPIO,最高16个定时器,最高2个ADC,最高1个DAC,最高2个I2C,最高3个SPI,最高5个USART/UART,最高1个USB 2.0 FS |

| STM32L1 | 2011年 | Cortex-M3 | 最高32MHz | 最高80KB RAM | 最高512KB Flash | 最高87个GPIO,最高17个定时器,最高3个ADC,最高2个DAC,最高3个I2C,最高3个SPI,最高5个USART/UART,最高1个USB 2.0 FS |

| STM32L4 | 2016年 | Cortex-M4 (FPU) | 最高120MHz | 最高320KB RAM | 最高2MB Flash | 最高114个GPIO,最高24个定时器,最高3个ADC,最高2个DAC,最高4个I2C,最多6个SPI, 最多8个USART/UART, 最多1个USB 2.0 FS |

| STM32L5 | 2019年 | Cortex-M33 (FPU) | 最高110MHz | 最高256KB RAM | 最高512KB Flash | 最多114 GPIOs, 最多26 timers, 最多3 ADCs, 最多2 DACs, 最多4 I2Cs, 最多6 SPIs, 最多8 USARTs/UARTs, 最多1 USB 2.0 FS |

把 永 远 爱 你 写 进 诗 的 结 尾 ~