全部学习汇总: GreyZhang/g_TC275: happy hacking for TC275! (github.com)

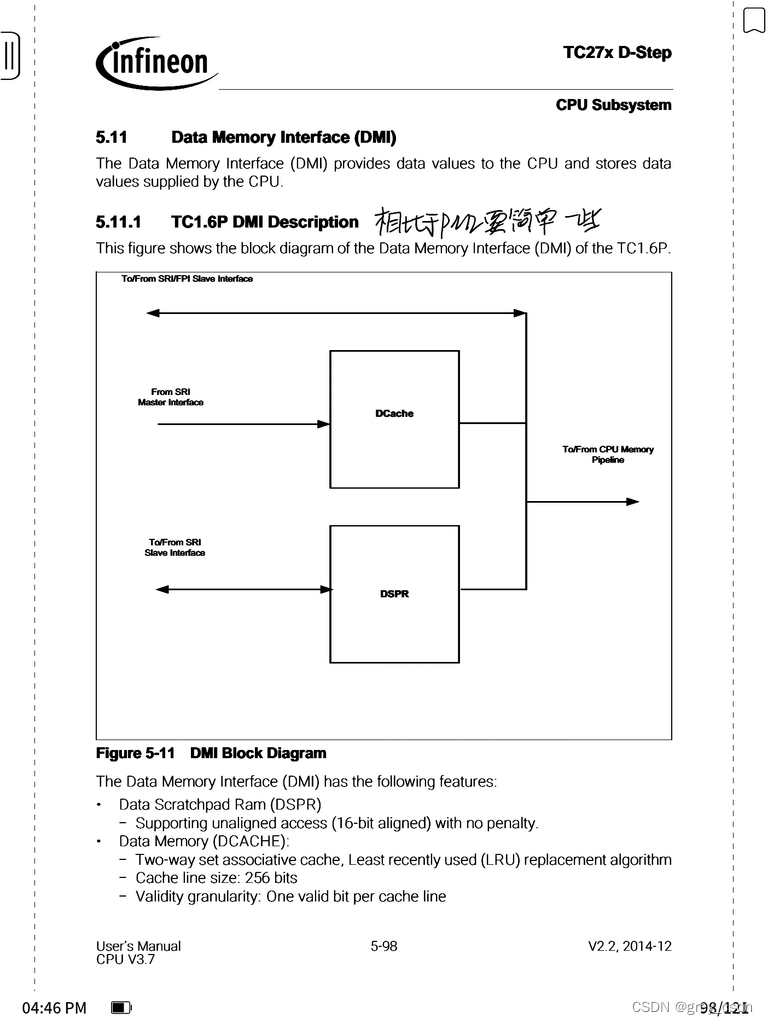

这个可以对比PMI来看一下,相比于PMI,DMI的结构简单很多。

1. 之前在看cache以及其对指令读取速度影响的时候,可能弄错了一个概念。如果cache不命中,可能CPU不会直接去从存储中直接获取数据而是请求cache的重新填充。

2. 如果数据的cache命中失败,在P核种会多等待一个时钟周期。

跟程序的PCache类似,其实DCache在默认情况下也是不开的。

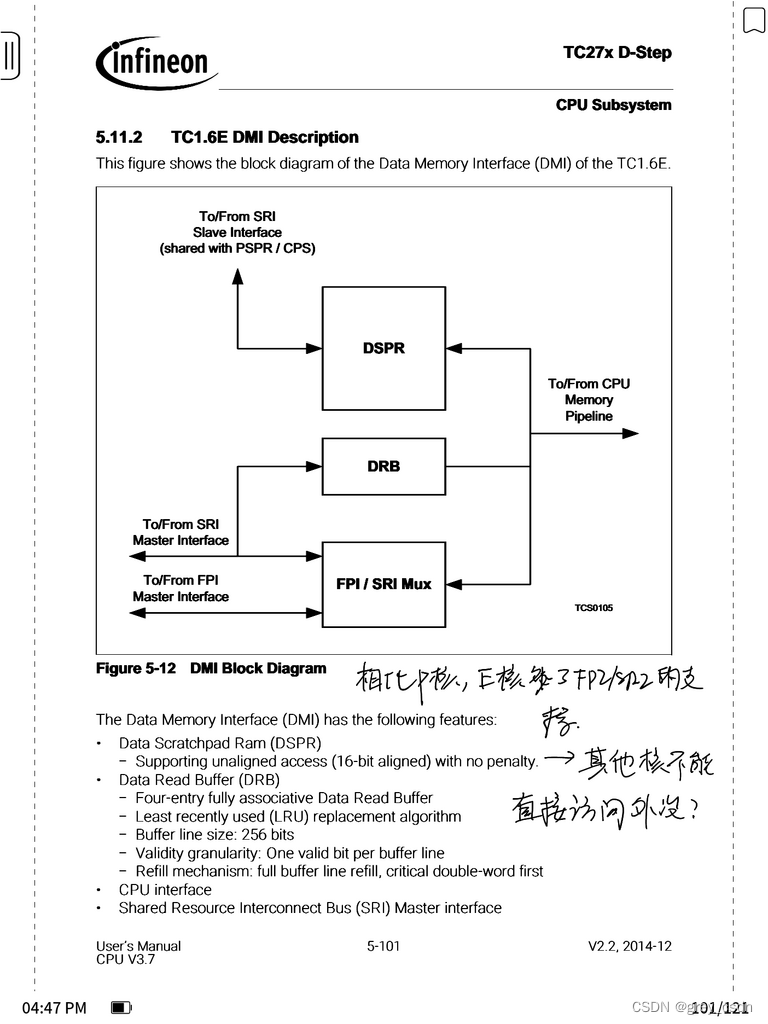

相比于P核,E核多了FPI以及SRI的支持。从这个角度看,难道所有的外设访问处理最终还都得路由到E核也就是CPU0来处理?

这部分的描述与P核相似,包括cache命中失败之后的等待时间都是一样的。

1. 这里出现了DES Trap的一些描述,介绍到了数据错误地址寄存器。这个在问题排查的时候是一个非常有帮助的信息。

2. 上下文切换范围异常额trap只有E核有支持。

在DAE Trap中,2个cache相关的错误信息只有P核是支持的。

这里是一个Cache开启以及关闭的寄存器信息,跟程序相关的是类似的。

以前以为锁步核实现的知识对于CPU计算信息的检查,先看来看其实涉及到的面还是很多的。SCU中带有一些子模块、数据存储、程序存储、程序Cache、程序Tag存储以及各个总线的行为。看起来,这个是一个系统级别的监控而不是简单的CPU的计算结果。

这样,CPU子系统的部分基本看完了,算是对内核相关的信息有了一点轮廓概念了。

![[附源码]JAVA毕业设计抗击新冠疫情专题宣传网站(系统+LW)](https://img-blog.csdnimg.cn/8626ba7453da4f43829805da6393379f.png)

![[附源码]Python计算机毕业设计Django楼盘销售管理系统](https://img-blog.csdnimg.cn/4cb2eca455744795b9250235afd1b553.png)