努力是为了不平庸~

学习的最大理由是想摆脱平庸,早一天就多一份人生的精彩;迟一天就多一天平庸的困扰。

急的同学请直接点击目录跳到下方解答处!!

目录

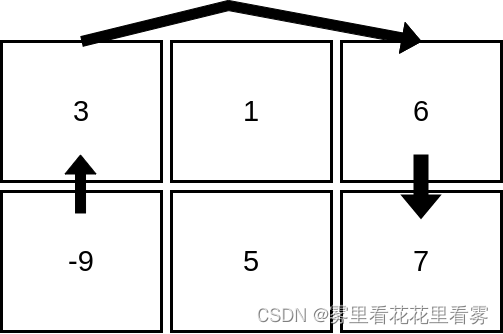

图解:编辑

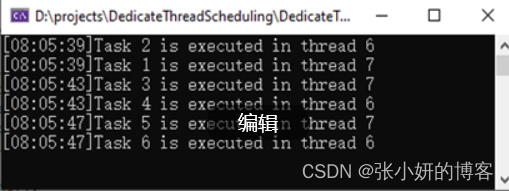

代码题解(免费):

实验目的

帮助学生掌握奇偶校验基本原理和特性,能在 Logisim 中实现偶校验编码电路,检错电路,理解校验码传输的原理。

实验内容

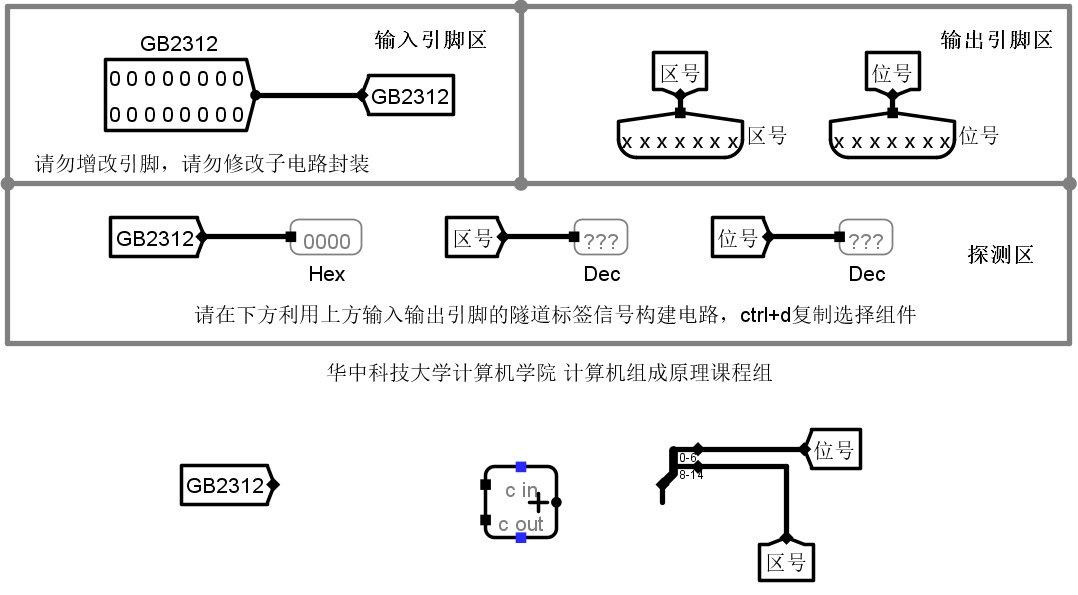

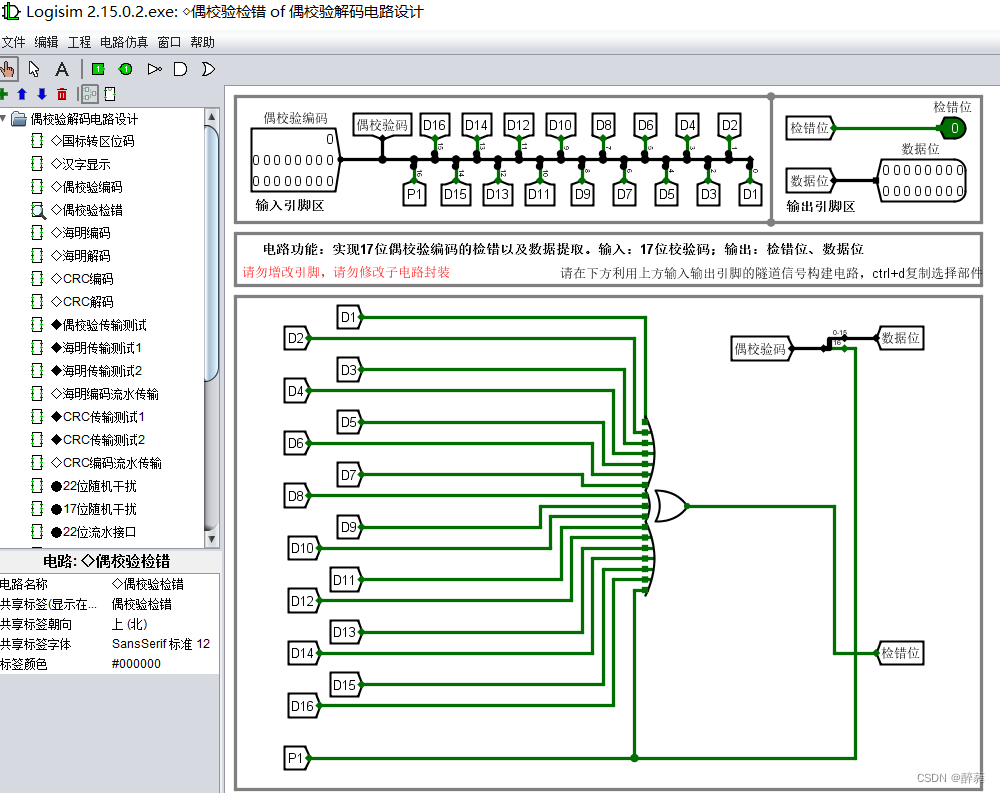

在logisim中打开实验资料包中的 data.circ 文件,在对应电路中完成偶校验检错电路。输入:17位校验码,校验位存放在最高位;输出:16位原始数据,1位检错位;实验电路输入输出引脚定义如图所示,注意17位校验码的每一位都通过分线器利用隧道标签引出,方便实验时使用。

电路框架

data.circ

电路引脚

| 信号 | 输入/输出 | 位宽 | 说明 |

|---|---|---|---|

| 校验码 | 输入 | 17 位 | 最高位为偶校验位的偶校验数据 |

| 检错位 | 输出 | 1 位 | 1 表示有错,0 表示无错 |

| 数据位 | 输出 | 16 位 | 无冗余信息的原始数据 |

电路测试

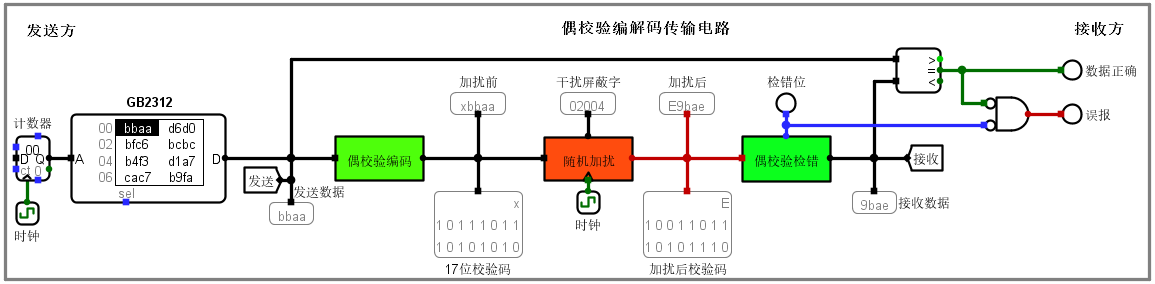

离线测试:电路框架提供了偶校验编码传输测试子电路,完成偶校验解码电路后可以进行测试,具体测试电路如下图所示:

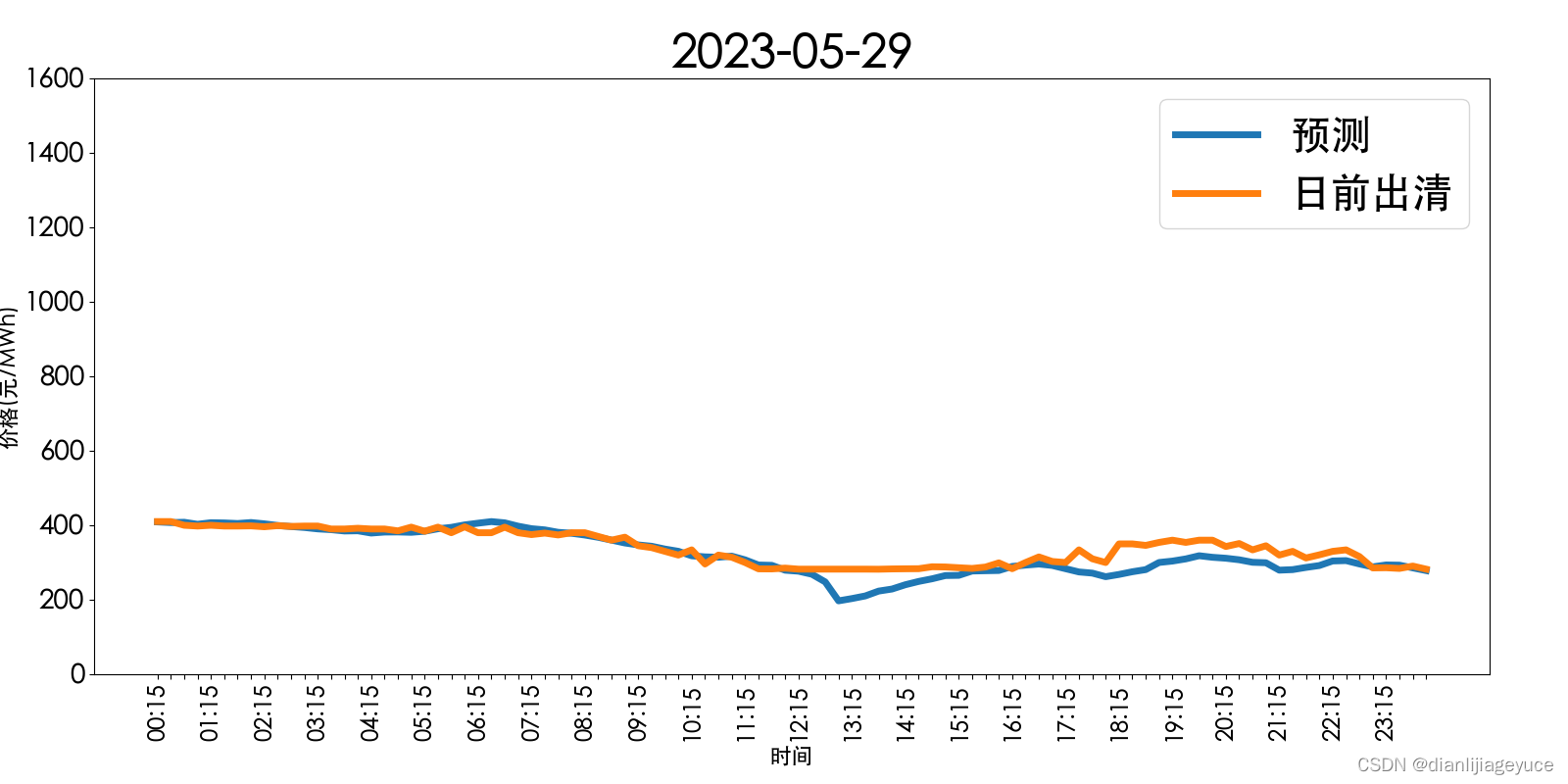

EduCoder 测试:完成实验后利用文本编辑工具打开 data.circ ,将所有文字信息复制粘贴到 Educoder 平台的 data.circ 文件中,再点击评测按钮即可进行本关测试,平台会对你设计的电路进行自动测试,为方便测试,请勿修改子电路封装,本关测试用例如下:

Cnt ParityD GB2312 Err00 0bbaa bbaa 001 16d01 6d01 102 1bfc6 bfc6 003 1cbcd cbcd 104 14f34 4f34 105 11a7e 1a7e 006 1cac7 cac7 007 19fa3 9fa3 108 1cd23 cd23 109 1dcc7 dcc7 10a 13fd3 3fd3 00b 1b2bf b2bf 00c 16b17 6b17 00d 1caf4 caf4 00e 1c497 c497 10f 08abe 8abe 1...

常见调试问题

1、为什么测评是系统提示找不到GB2312ROM.CIRC?

注意实验文件data.circ 与GB2312ROM.circ应该放在同一个目录下,前者调用了GB2312ROM.circ电路,有可能大家做实验的时候没有放在一起,然后找不到这个文件的时候大家指向了另外一个目录的GB2312ROM.circ,这样对应文件的路径就带到电路文件中去了,上传平台时测试这个路径的文件肯定是不存在的,所以就无法加载这个电路。 解决这个问题可以采用以下两种方法: (1)本地修改,直接将本地的data.circ,GB2312ROM.circ剪切移动到一个新目录中,注意一定是剪切,要保证再次打开data.circ的时候找不到原来的GB2312ROM.circ,当提示找不到该文件的时候就就点击同目录的GB2312ROM.circ,然后存盘退出就ok,再次提交测试。 (2)直接EduCoder平台修改,直接在代码框搜索该文件路径 去掉绝对路径,改成如下形式即可 2、Educoder平台实际输出XXXX是什么原因? 如果你本地测试是ok的,上传Educoder平台出现输出为悬浮态X,主要有两种可能的原因。 第一种可能是你上传错了代码,有可能上传的是别的目录的框架文件,根本没有实现电路,所以没有任何输出,要判断是否是这种情况只需要将平台的代码下载到本地打开看看就知道了; 另外一种可能是你电路的封装引脚可能因为增删改引脚发生了变化,系统测试时对应的输出引脚没有连接正确,所以需要仔细检查待测电路的封装,目前所有框架文件均提供了待测电路的封装测试子电路,仔细检查引脚是否和连线错位。

解答:

图解:

代码题解(免费):

自己做的,立志打破积分下载垄断!代码有点长,上传资源了

Logisim头歌偶校验解码电路设计图解及代码(计算机组成原理)免费自取!留个赞吧资源-CSDN文库