写在前面:

每一年的综合设计肯定都有改动,故肯定不能照搬照抄,大家可以借鉴思路,复现成果,但要注意不同之处,以免被0分处理。

模型设计的指导书我不放在这里了,因为那是课程组老师们的成果。

另外一定要夸奖课程组的凌老师!!!认真负责!!如果是她任教,那可真是运气太好啦!!

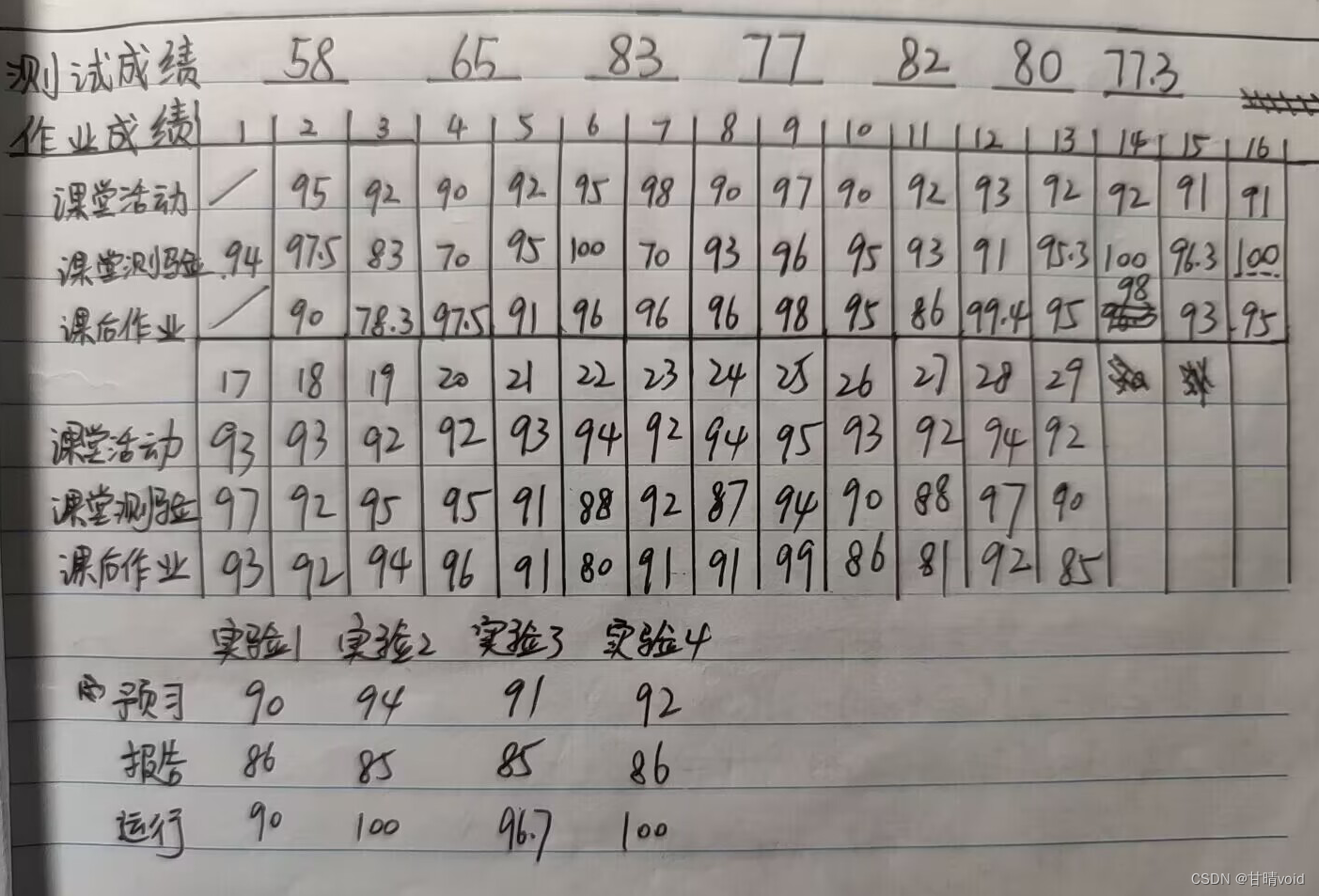

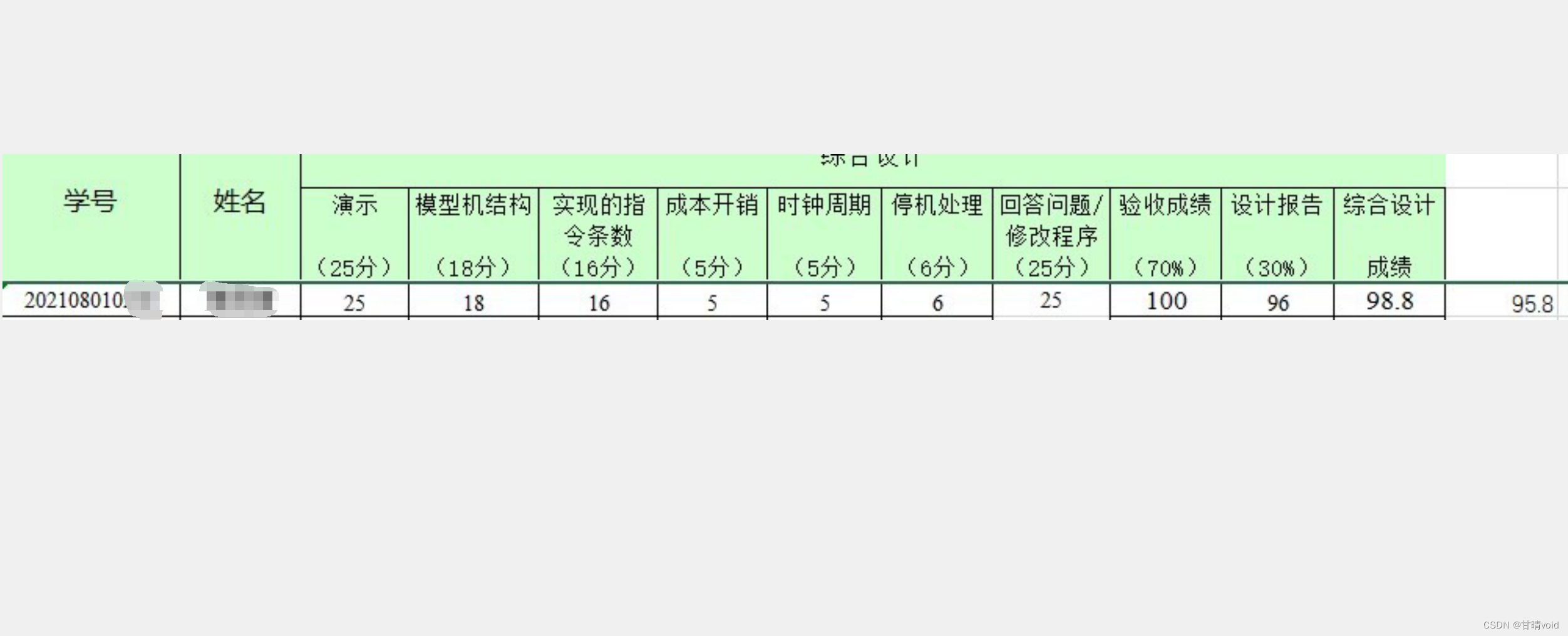

这是我综合设计最终的成绩(能拿的都拿了,剩下的是拿不到的)

(找老师将程序下载入电路板验证,可以得到验收成绩的高分)

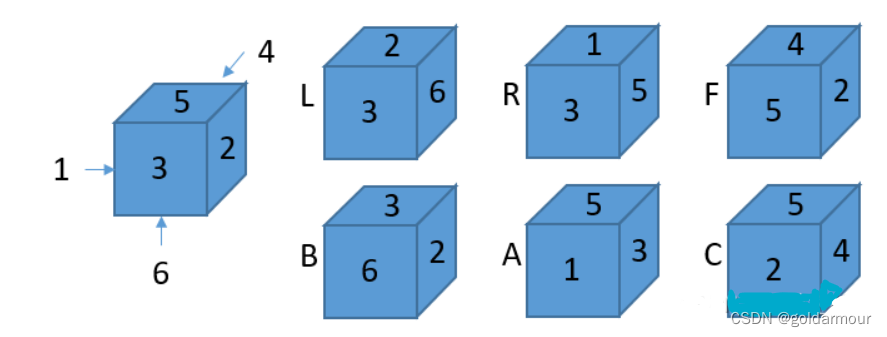

再放一幅封面

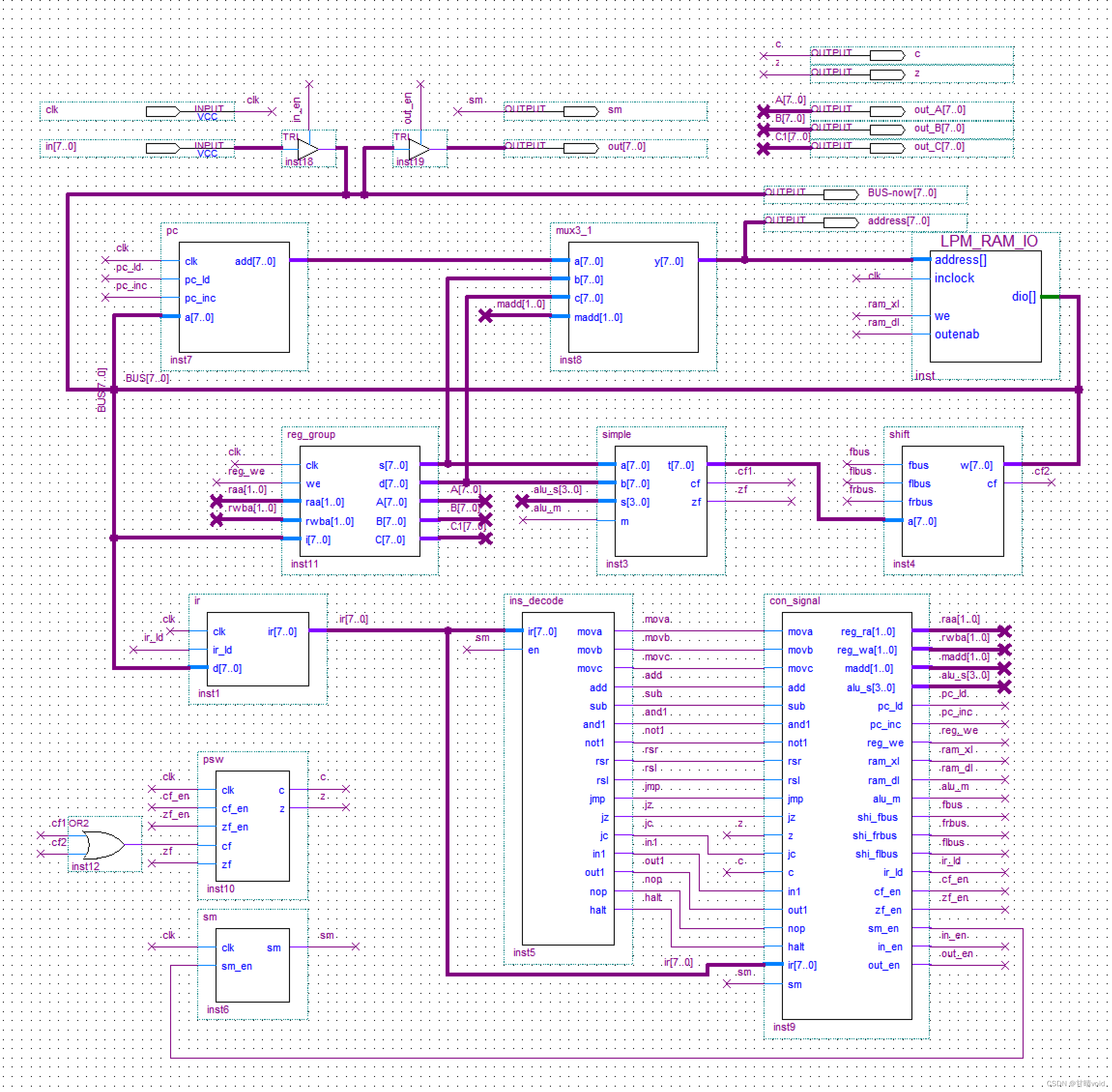

最终结果成图

这是最终的结果成图,这个是需要自己去连接的,还有一些中间的设计步骤,老师都会很详细地去讲解。我比较推荐使用迭代增量的方法去搞。就是连接几个模块,然后测试该模块是否成立,确认正确的情况下再继续下去。这样不容易最终对着一堆问题手足无措。

老师有详细的讲解,还录制了视频。但由于这是凌老师精心准备的,我不能未经她允许就放在这里公开(虽然她会同意)。故如果HNUer有需要可以私下找我要。

下面是我最终提交的设计报告

模型机设计报告

班级 计科210X 姓名 wolf 学号 202108010XXX

一、设计目的

完整、连贯地运用《电路与电子学》所学到的电路、模电和数电知识,熟练掌握现代 EDA

工具基本使用方法,为后续课程学习和今后从事相关工作打下良好的基础或做下一些铺垫。

二、设计内容

① 设计一个由传感器(电桥)、放大器、滤波器、模数转换器构成的模拟通道;

② 按照给定的数据通路、数据格式和指令系统,使用 EDA 工具设计一台用硬连线逻辑控制的简易计算机;

③ 用所设计的计算机控制模拟通道对外界模拟输入信号进行采样、离散和处理,并显

示在数码显示管上;

三、详细设计

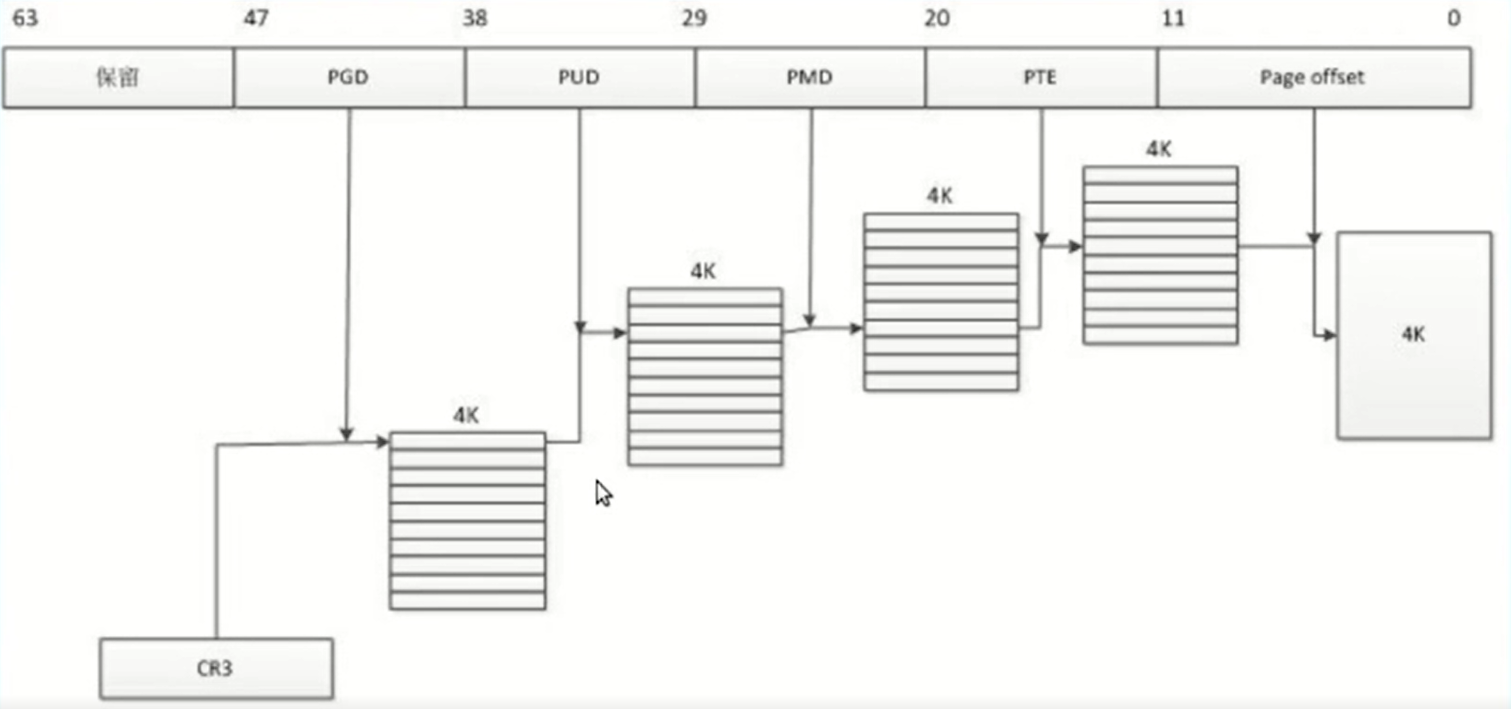

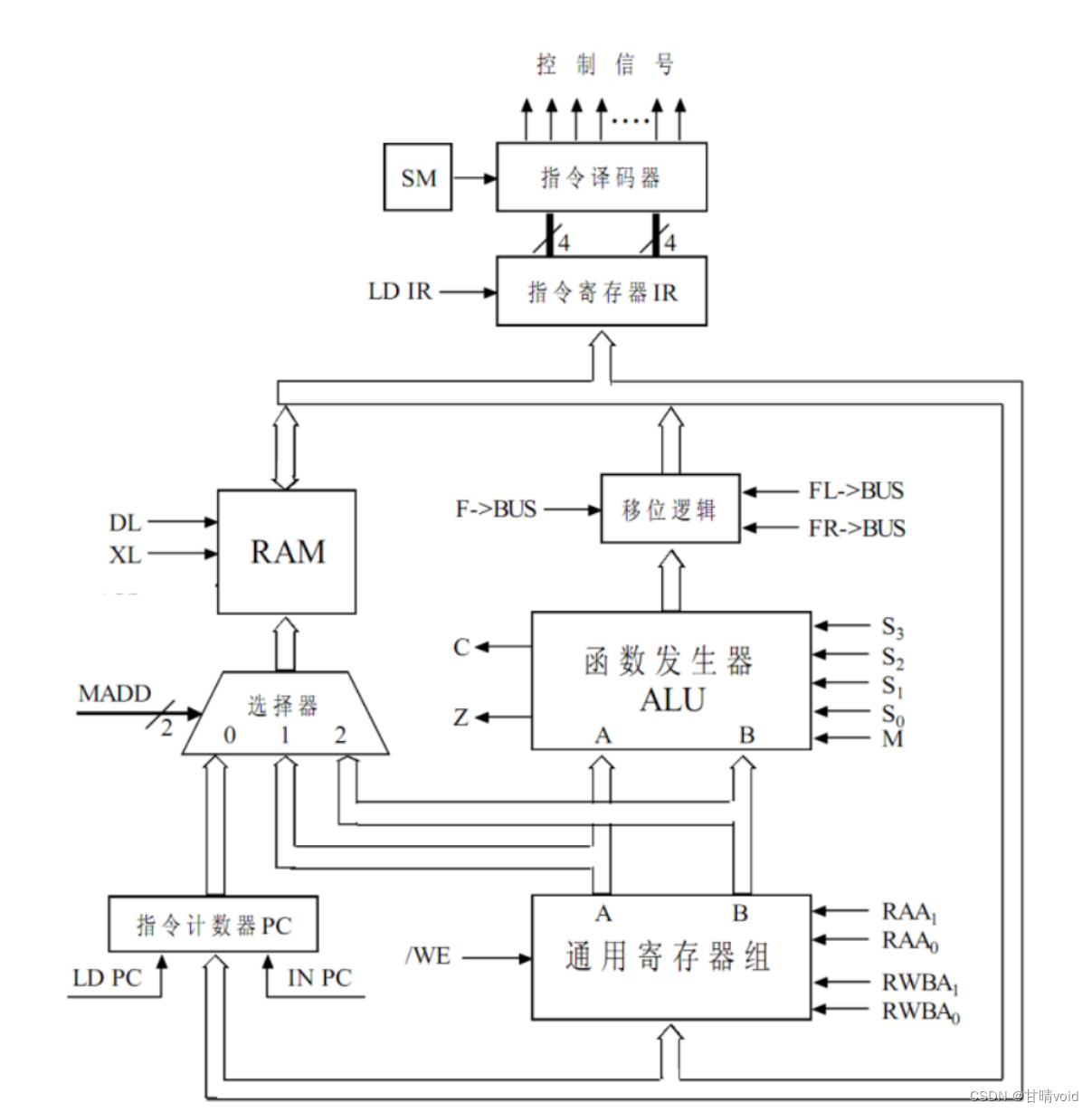

3.1设计的整体架构

3.2各模块的具体实现

(此部分必须有模块的接口设计,功能实现,功能的仿真验证等内容。)

3.2.1指令译码器

(1)接口设计:

input [7:0] ir;

input en;

output mova,movb,movc,add,sub,and1,not1,rsr,rsl,jmp,jz,jc,in1,out1,nop,halt;

(2)功能实现:

判定是哪条指令,则对应指令的输出为 1,否则输出为 0。

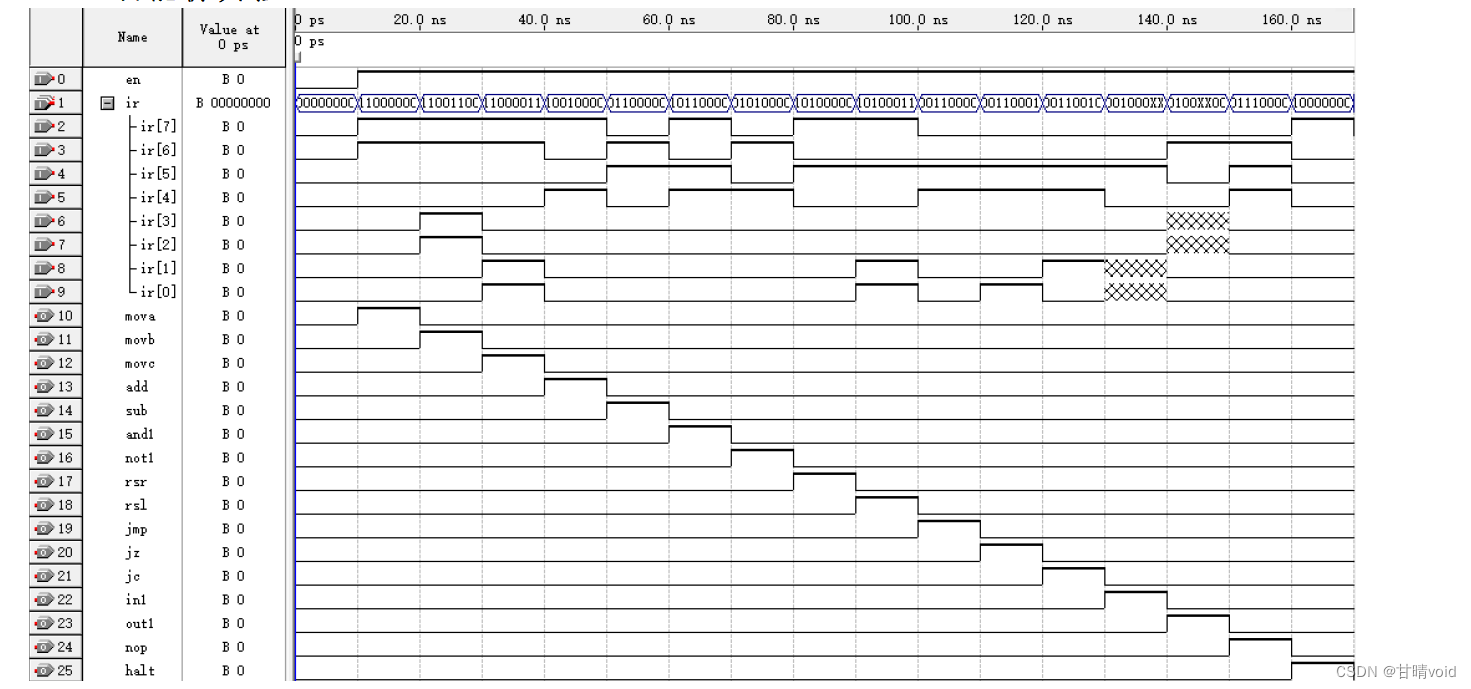

(3)功能仿真验证:

结果分析及结论:

分析:功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验

证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路

设计的真值表的结果相对应。

当 en 为 0 时,不管 ir 为何值,16 个输出全为 0

当 en 为 1 时:

当 ir=11000000 时,mova 输出为 1;

当 ir=11001100 时,movb 输出为 1;

当 ir=11000011 时,movc 输出为 1;

当 ir=10010000 时,add 输出为 1;

当 ir=01100000 时,sub 输出为 1;

当 ir=10110000 时,and1 输出为 1;

当 ir=01010000 时,not1 输出为 1;

当 ir=10100000 时,rsr 输出为 1;

当 ir=10100011 时,rsl 输出为 1;

当 ir=00110000 时,jmp 输出为 1;

当 ir=00110001 时,jz 输出为 1;

当 ir=00110010 时,jc 输出为 1;

当 ir=00100000 时,in1 输出为 1;

当 ir=01000000 时,out1 输出为 1;

当 ir=01110000 时,nop 输出为 1;

当 ir=10000000 时,halt 输出为 1;

结论:功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结

果有一定误差。

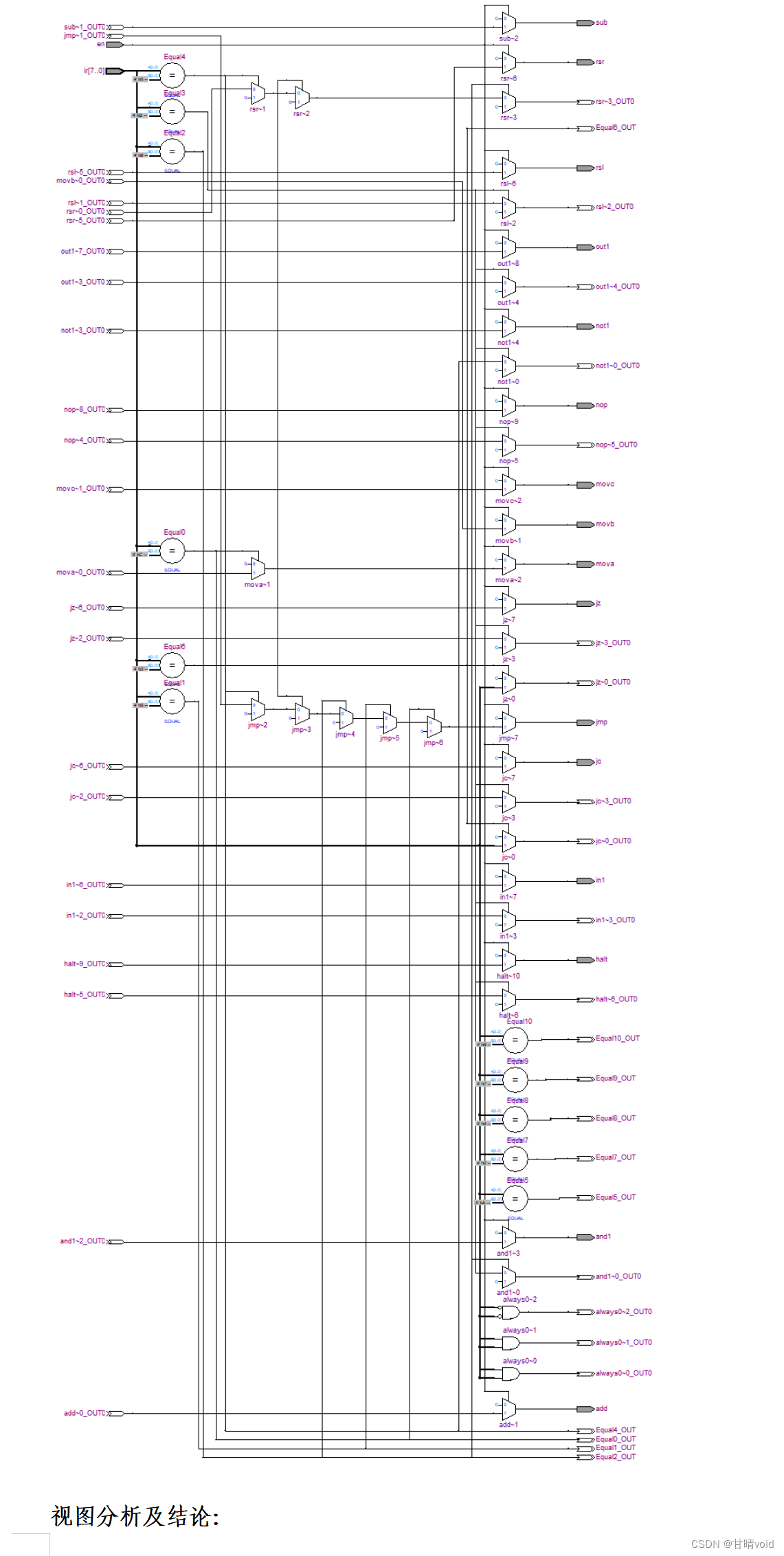

(4)RTL视图

视图分析及结论:

分析:

- 由视图可得,视图左边为输入,右边为输出。

- 其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;

- 还有许多 2-1 选择器,当控制信号为 0 时,输出第一位,控制信号为 1 时,输出第二位。图中输入信号为 ir 和 en,输出信号包 括 add 等 16 种情况。各个输出端口之间通过导线相连。

结论:一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

(5) 时序仿真验证

结果分析及结论:

分析:

- 时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器件和布线的延时信息。

- 由波形可得,当输入状态发生改变时,输出结果并未同时改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

- 时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。

- 时序仿真不仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

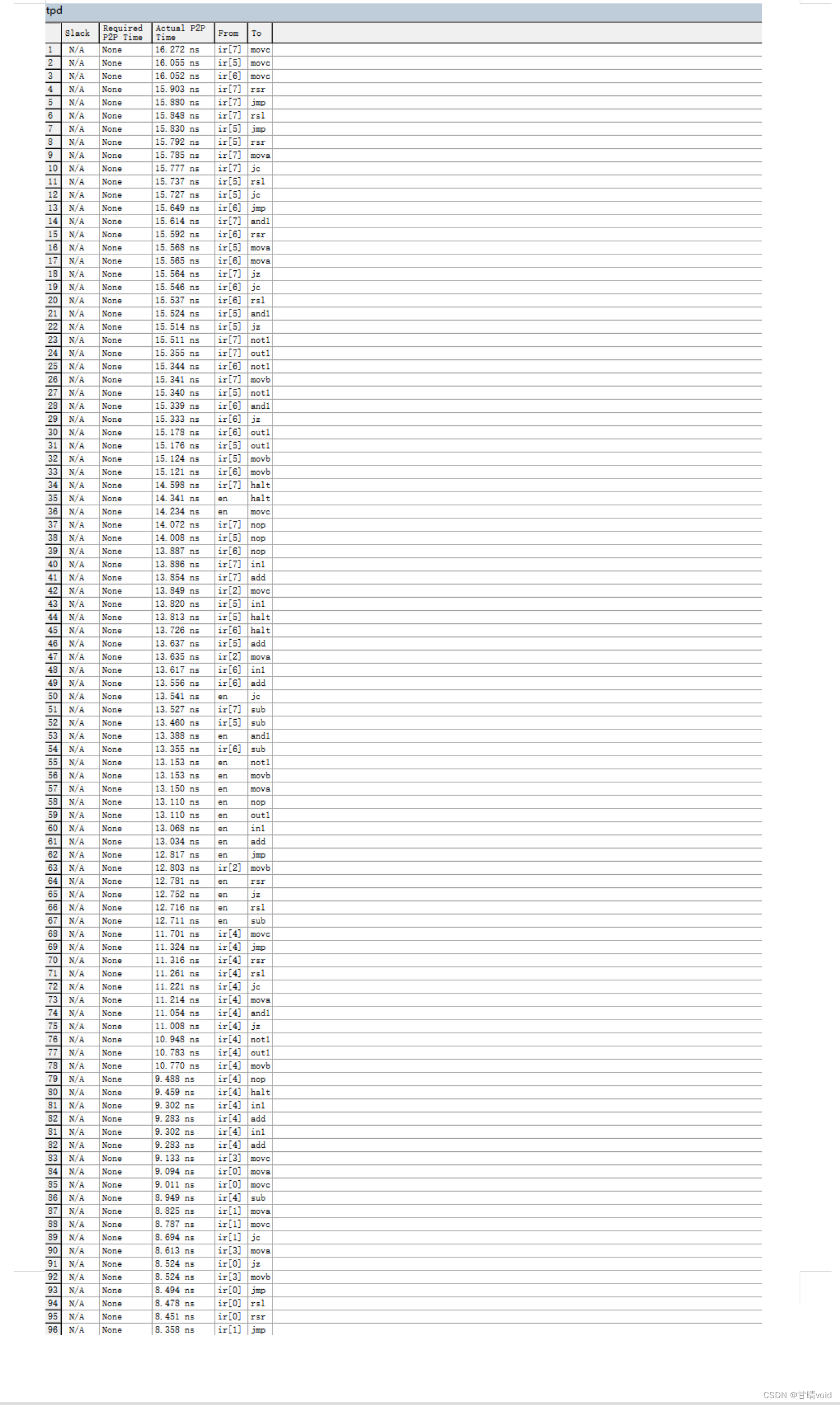

(6) 时序分析

结果分析及结论:

由图可得,Timing Analyzer Summmary总结所有经典定时分析的结果,并报告每个 定时特性的最坏情况定时。比如从 ir[3]到jmp的最坏定时情况的 tpd 为 11.720ns。下面的tpd 报告表则给出了源节点和目标节点之间的tpd延迟时间,比如第二行中 ir[5]到 add 的tpd 为 11.699ns。实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延

迟也不相同。

3.2.2ALU

(1)接口设计

input [7:0] a;

input [7:0] b;

input m;

input [3:0] s;

output cf,zf;

output [7:0] t;

(2)功能实现

算术逻辑运算类指令:

ADD R1, R2 SUB R1, R2 AND R1, R2 NOT R1

这类指令的执行过程为:

由 R2 的编码通过 RAA1、RAA0 从通用寄存器组 A 口读出 R2 的内容,由 R1的编码通过 RWBA1、RWBA0 从通用寄存器组 B 口读出 R1 的内容,在 S3~S0和 M 的控制下,实现运算,经移位逻辑送入总线 BUS;由/WE 控制和 R1 的编码选择 RWBA1、RWBA0,将 BUS 上的数据写入通用寄存器 R1。其中 ADD 和 SUB 指令影响状态位 Cf 和 Zf。

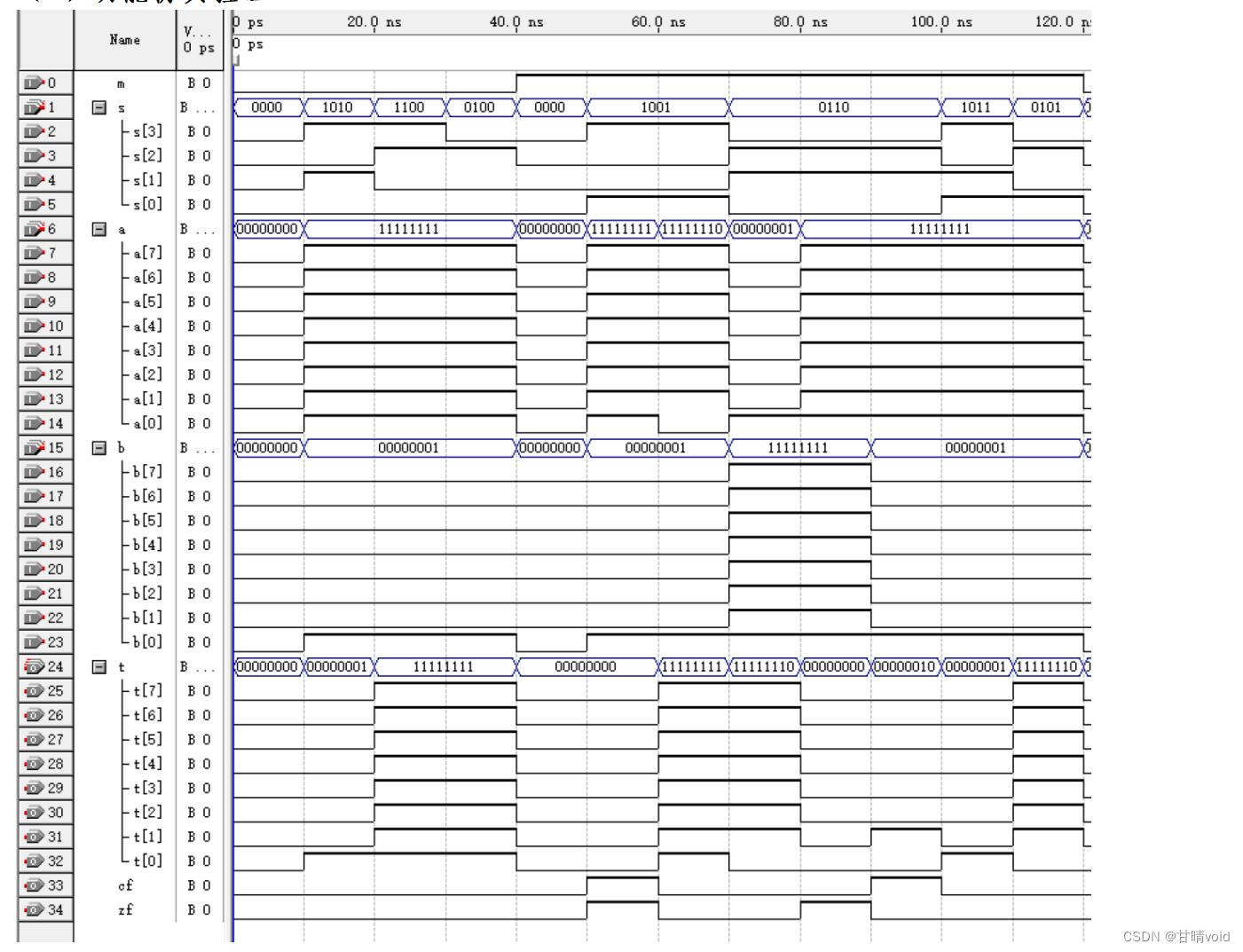

(3)功能仿真验证

结果分析及结论:

分析:功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验

证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路

设计的真值表的结果相对应。

当控制信号 m 为 1,s 为 1001 时,执行 t=a+b

当控制信号 m 为 1,s 为 0110 时,执行 t=b-a

当控制信号 m 为 1,s 为 1011 时,执行 t=a&b

当控制信号 m 为 1,s 为 0101 时,执行 t=~b

当控制信号 m 为 1,s 为 1010 时,执行 t=b

当控制信号 m 为 0,s 为 1100 时,执行 t=a

有进位和借位时 cf 为 1,否则为 0;

和为 0 或差为 0 时 zf 为 1,否则为 0;

结论:功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结

果有一定误差。

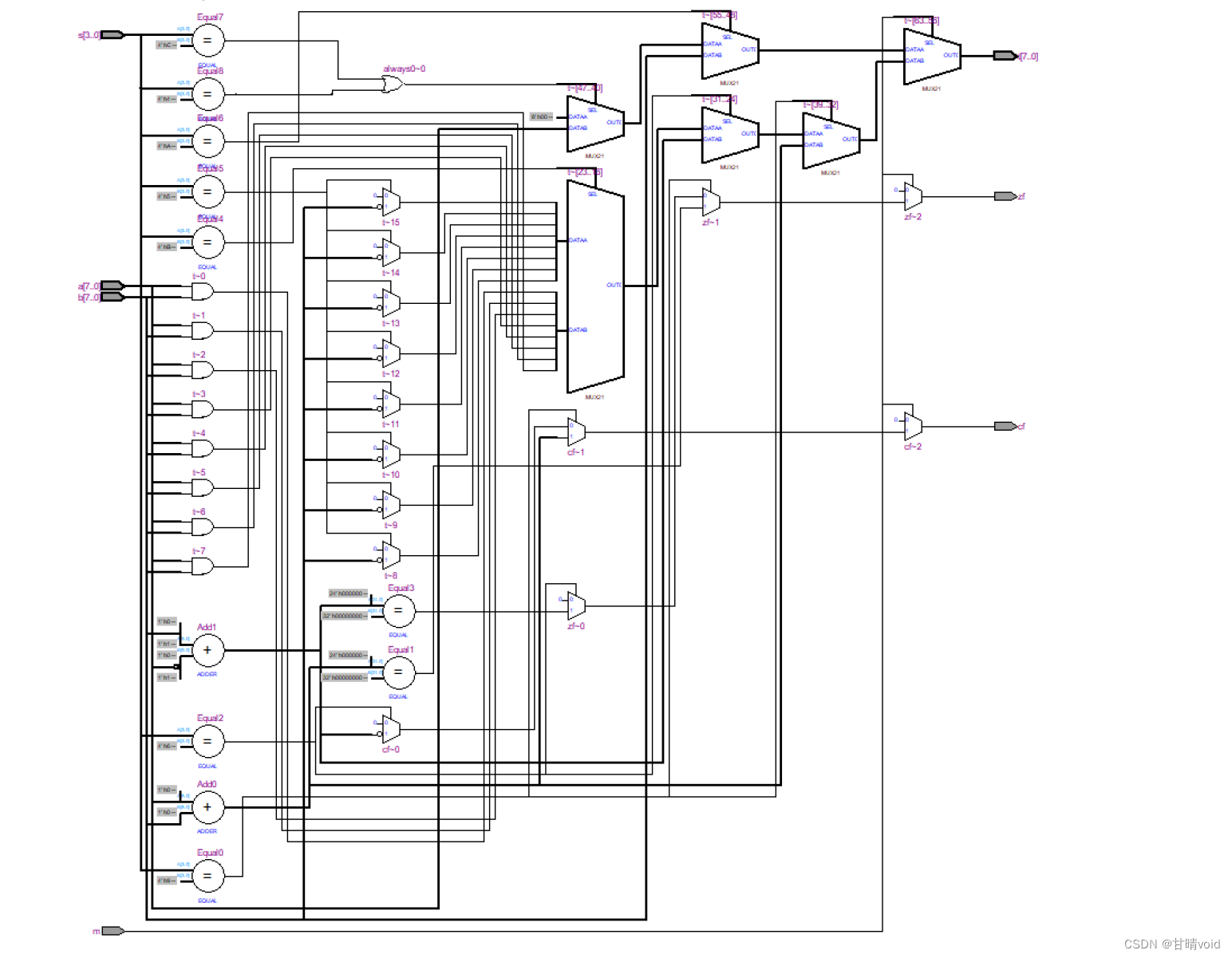

(4)RTL视图

结果分析及结论:

分析:

1、由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较

器:当输入相等时输出 1,不相等时输出 0;

2、同时存在大量的 2-1 选择器,当控制信号为0 时,输出第一位,控制信号为1时,输出第二位。图中输入信号为 m,s,a,b,输出信号 为 t,cf,zf。各个输出端口之间通过导线相连。

结论:一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

(5)时序仿真验证

结果分析及结论:

分析:

- 时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,又包含了器件和布线的延时信息。

- 由波形可得,当输入状态发生改变时,输出结果并未同时改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:

1、时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。

2、时序仿真不 仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

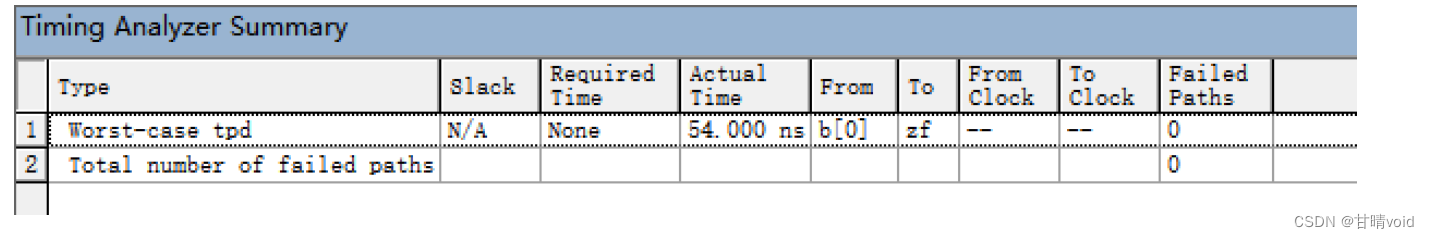

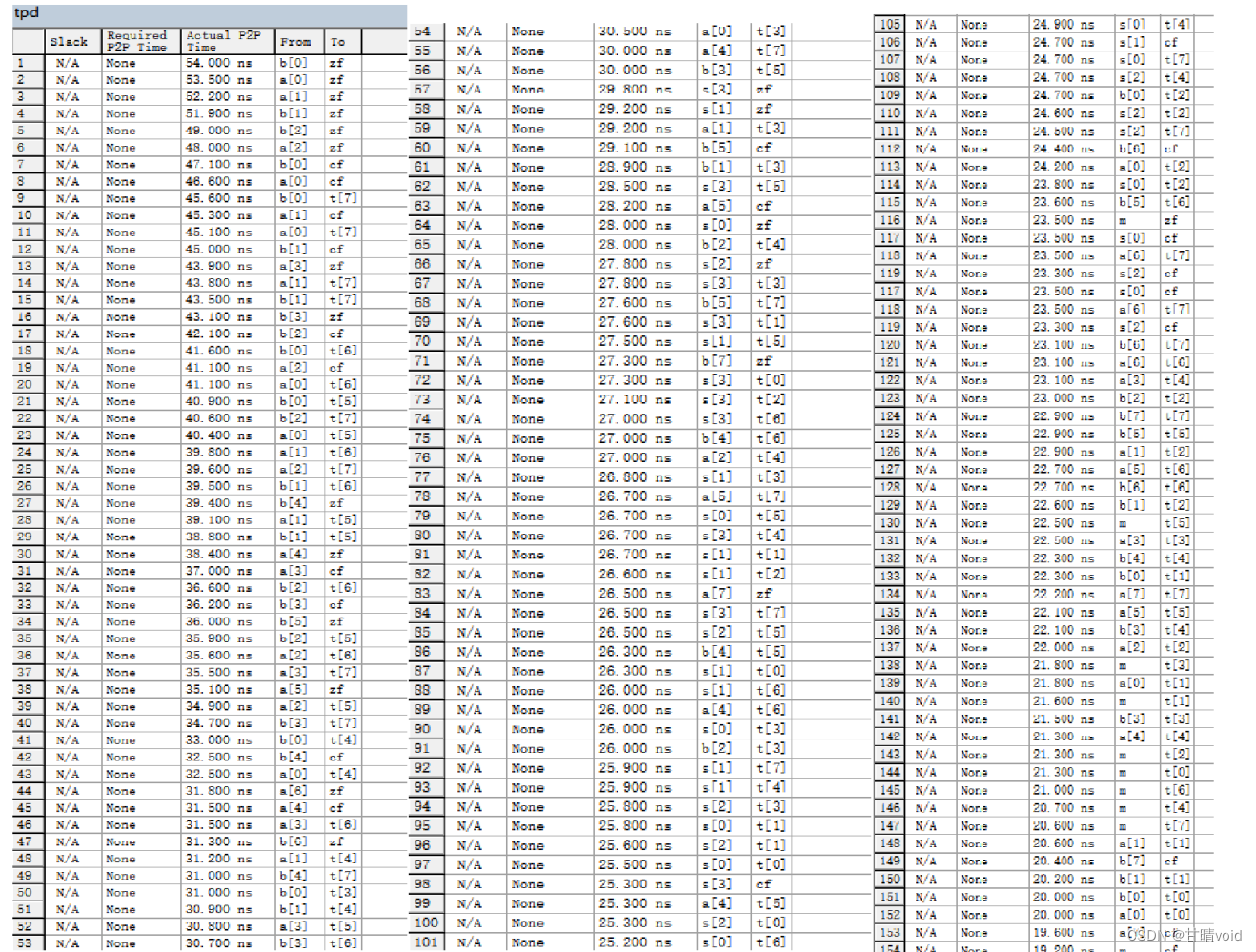

(6)时序分析

结果分析及结论:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个 定时特性的最坏情况定时。比如从 a[0]到 zf 的最坏定时情况的 tpd 为 38.50ns。下面的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第二行中 s[0]到 t[0]的 tpd 为 29.6ns。

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不同。

3.2.3 8 重 3-1 多路复用器

(1)接口设计

input [7:0] a;

input [7:0] b;

input [7:0] c;

input [1:0] madd;

output [7:0] y;

(2)功能实现

多路复用器是一个组合电路,它可以从多个输入中选择一个输入,并将信息直接传输到输出。选择哪一条输入线由一组输入变量控制,它们被称为选择输入。通常,2^n条输入线要 n 个选择输入,选择输入的位组合决定选择哪个输入线。

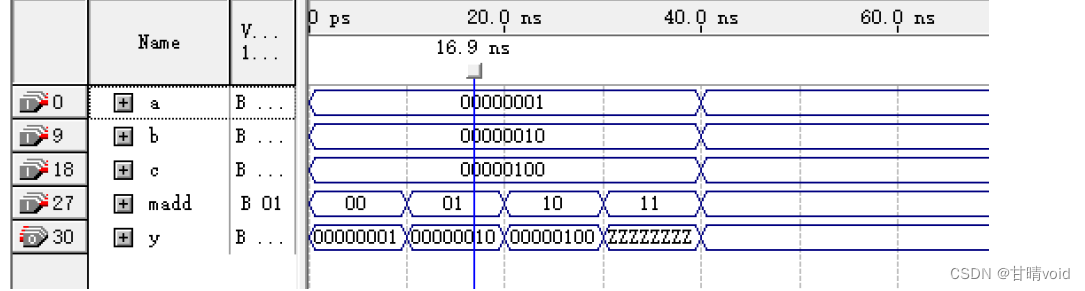

(3)功能仿真验证

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

madd=00 时,控制输出 y 等于 a,正确

madd=01 时,控制输出 y 等于 b,正确

Madd=10 时,控制输出 y 等于 c,正确

Madd=11 时,控制输出高阻态,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

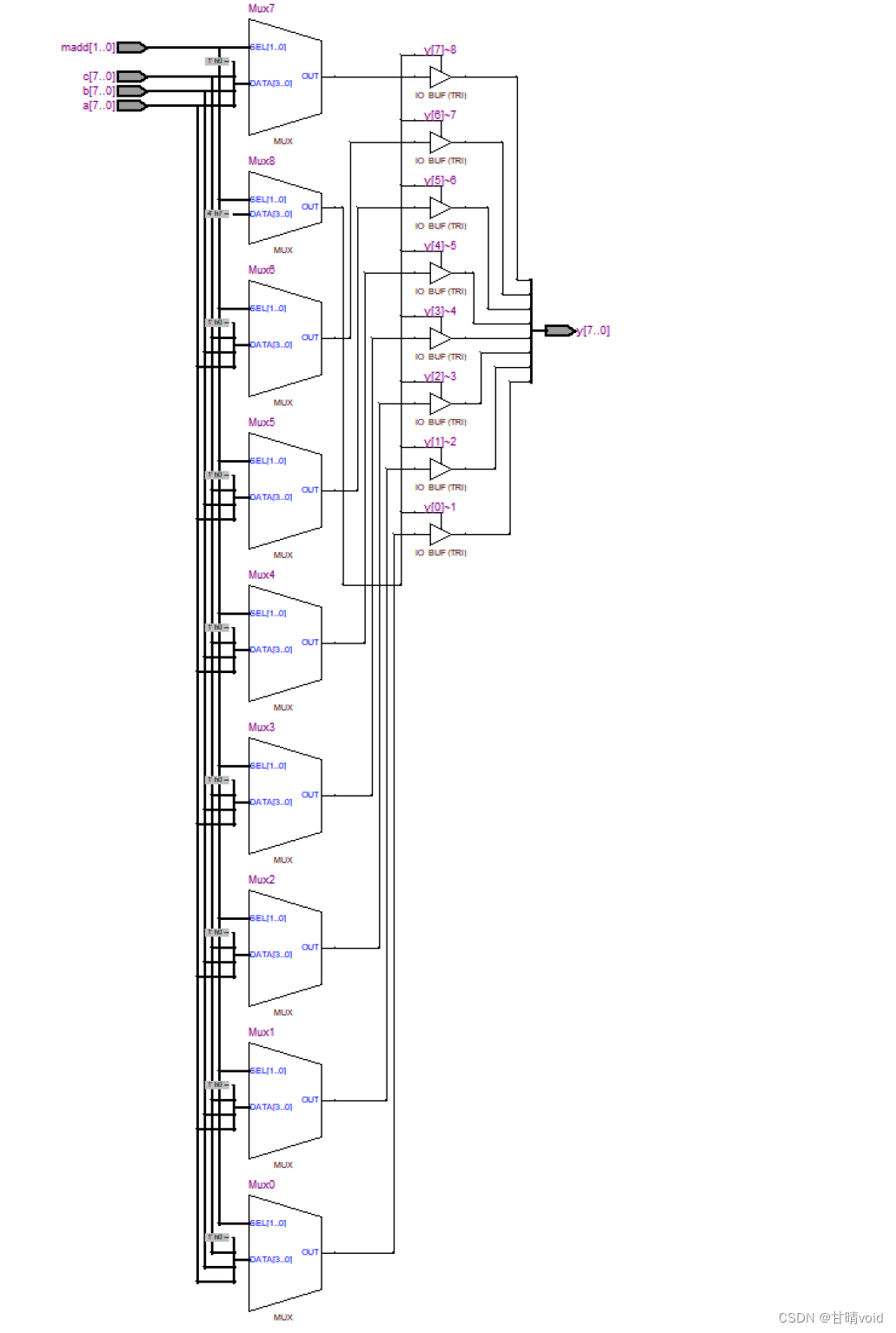

(4)RTL视图

视图分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的 2-1 选择器构成,当控制信号为 0 时,输出第一位,控制信号为 1 时,输出第二位。图中输入信号为 madd和 a,b,c,输出信号为 y。各个输出端口之间通过导线相连。

结论:一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

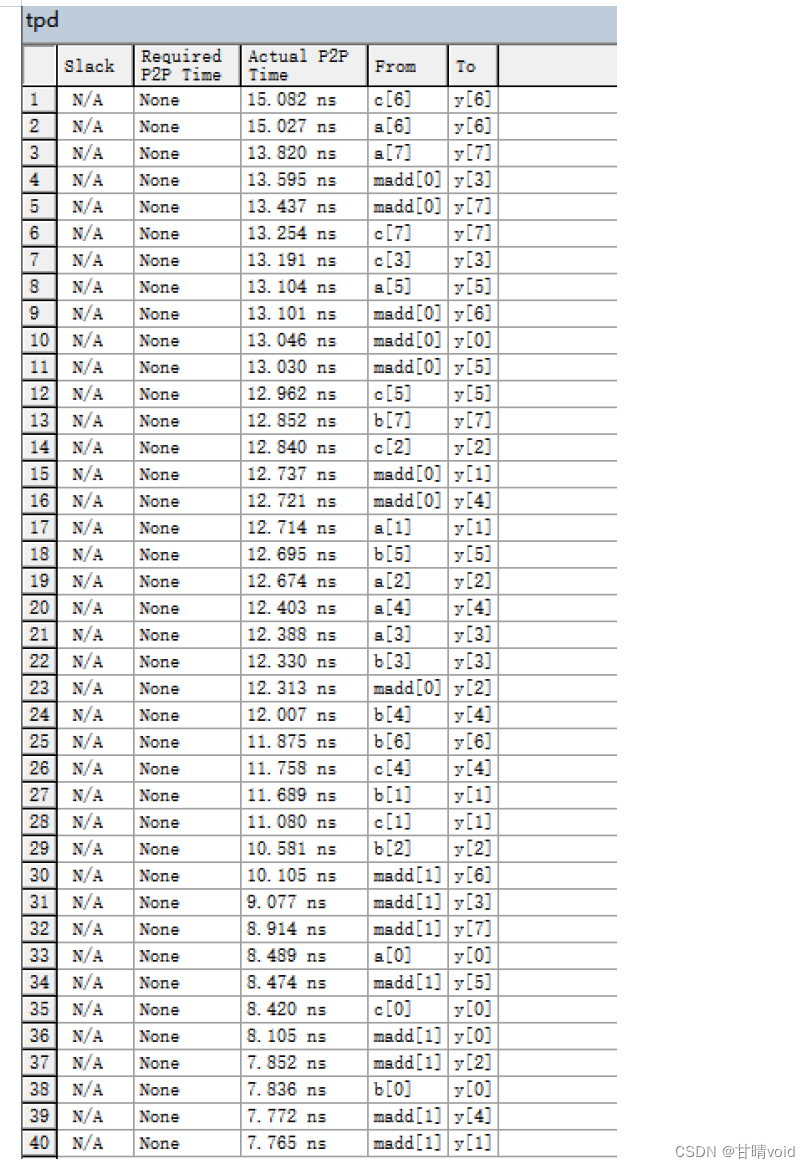

(5)时序仿真验证

结果分析及结论:

分析:功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

madd=00 时,控制输出 y 等于 a,正确

madd=01 时,控制输出 y 等于 b,正确

Madd=10 时,控制输出 y 等于 c,正确

Madd=11 时,控制输出高阻态,正确

结论:功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

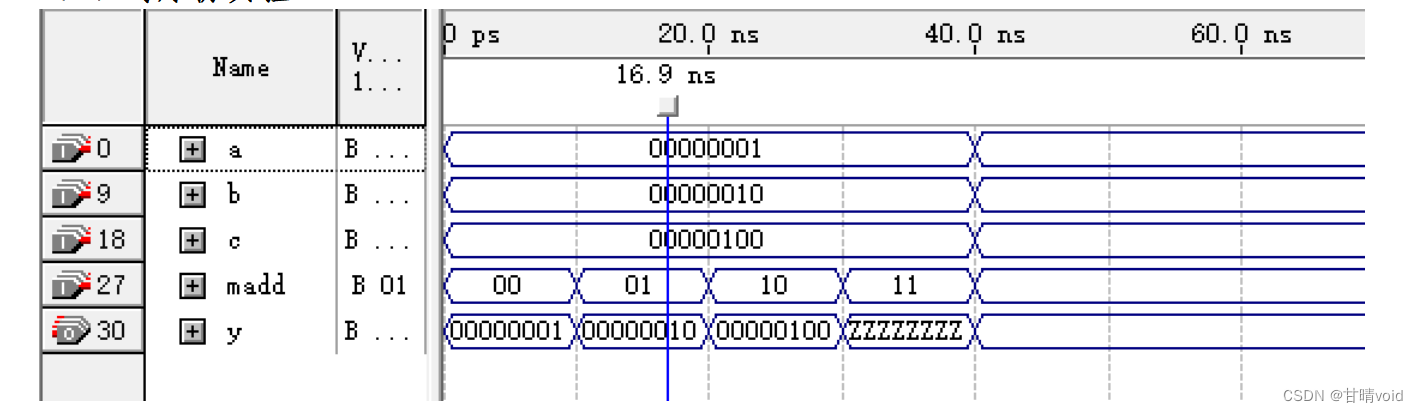

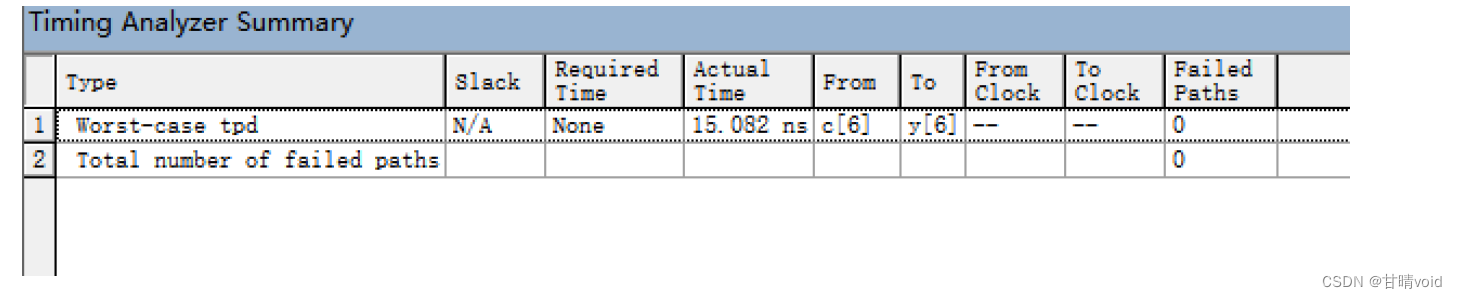

(6)时序分析

结果分析及结论:

分析:

由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 b[7]到 y[7]的最坏定时情况的 tpd 为 12.852ns。下面的tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟间,比如第二行中 a[7]到 y[7] 的tpd 为 13.820ns。

结论:

实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

3.2.4移位逻辑

(1)接口设计

input fbus,flbus,frbus;

input [7:0] a;

output [7:0] w;

output cf;

(2)功能实现

移位指令:

RSR R1

RSL R1

这类指令的执行过程为:

由R1的编码通过RWBA1、RWBA0从通用寄存器组B口读出R1的内容,在 S3~S0和M的控制下通过ALU,经移位逻辑循环右移或循环左移后送入总线BUS; 再由/WE控制和R1的编码选择RWBA1、RWBA0,将BUS上的数据写入通用寄存器R1。

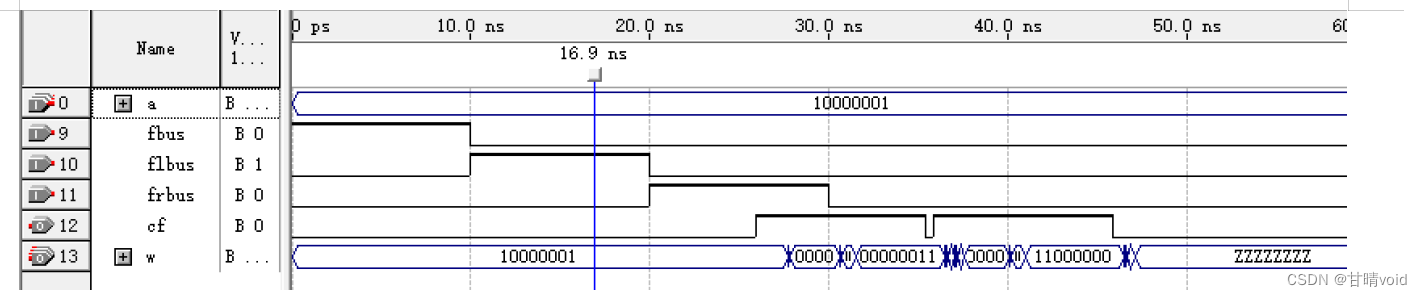

(3)功能仿真验证

结果分析及结论:

分析:

功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路设计的真值表的结果相对应。

当fbus=1,frbus=0,flbus=0,不执行移位操作,输出等于输入,cf 不改变

当fbus=0,frbus=1,flbus=0,执行右移,输出等于输入右移移位,有进位的话cf为1

当fbus=0,frbus=0,flbus=1,执行左移,输出等于输入左移一位,cf 不改变

当控制信号全为 0 时,输出为高阻态,正确

结论:

功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结果有一定误差。

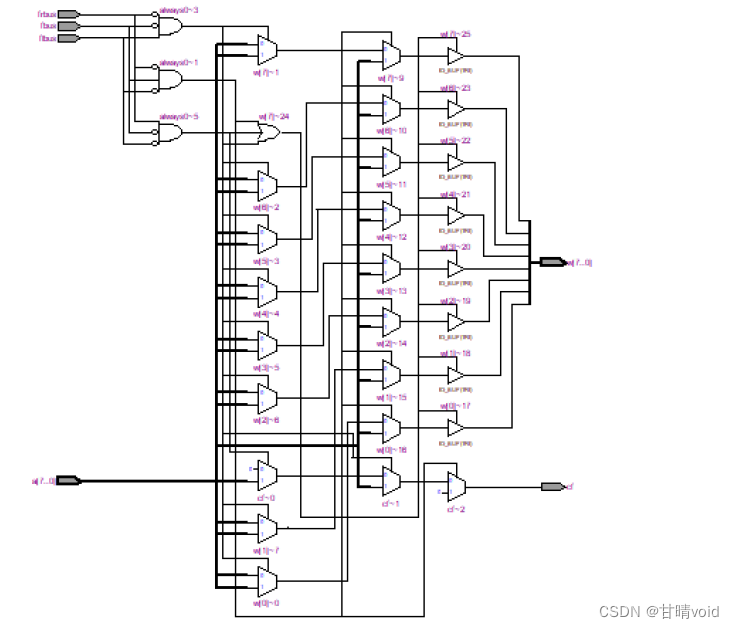

(4)RTL视图

结果分析:

分析:由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的 2-1 选择器构成,当控制信号为0 时,输出第一位,控制信号为 1 时,输出第二位。图中输入信号为 fbus,frbus,flbus 和 a,输出信号为 w。各个输出端口之间通过导线相连。

结论:一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

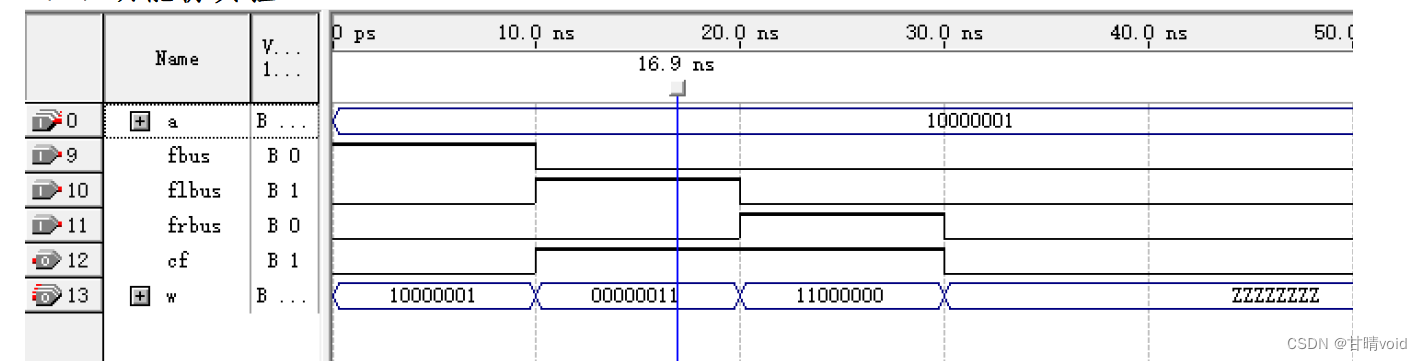

(5)时序仿真验证

结果分析及结论:

分析:时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关, 又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时 改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果并未与预期结果相同。

结论:时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

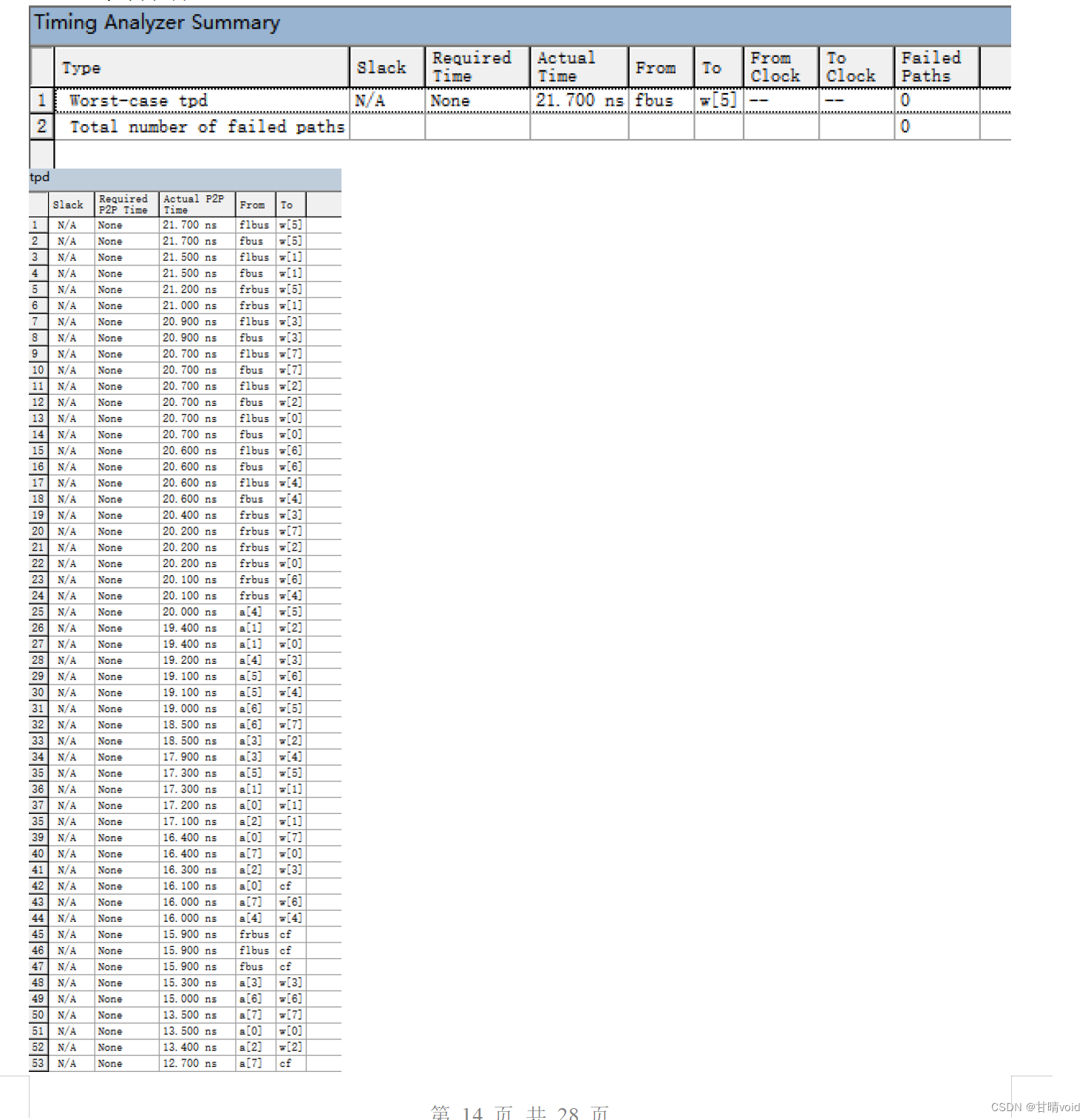

(6)时序分析

结果分析及结论:

分析:由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个定时特性的最坏情况定时。比如从 fbus 到 w[0] 的最坏定时情况的 tpd 为 20.700ns。下面的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第二行中 fbus 到 w[7] 的tpd 为 20.700ns。

结论:实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延迟也不相同。

3.2.5控制信号产生逻辑

(1)接口设计

input [7:0]ir;

input mova,movb,movc,add,sub,and1,not1,rsr,rsl,jmp,jz,z,jc,c,in1,out1,nop,halt,sm;

output reg [1:0] reg_ra;

output reg [1:0]reg_wa;

output reg [1:0]madd;

output reg [3:0]alu_s;

output reg pc_ld,pc_inc,reg_we,ram_xl,ram_dl,alu_m,shi_fbus,shi_frbus,shi_flbus,ir_ld,cf_en,zf_en,sm_en,in_en,out_en;

(2)功能实现

控制信号产生逻辑接收指令译码器的输出,在 SM、IR[7..0]以及状态位 Cf

和 Zf 的配合下产生每个模块所需要的控制信号。

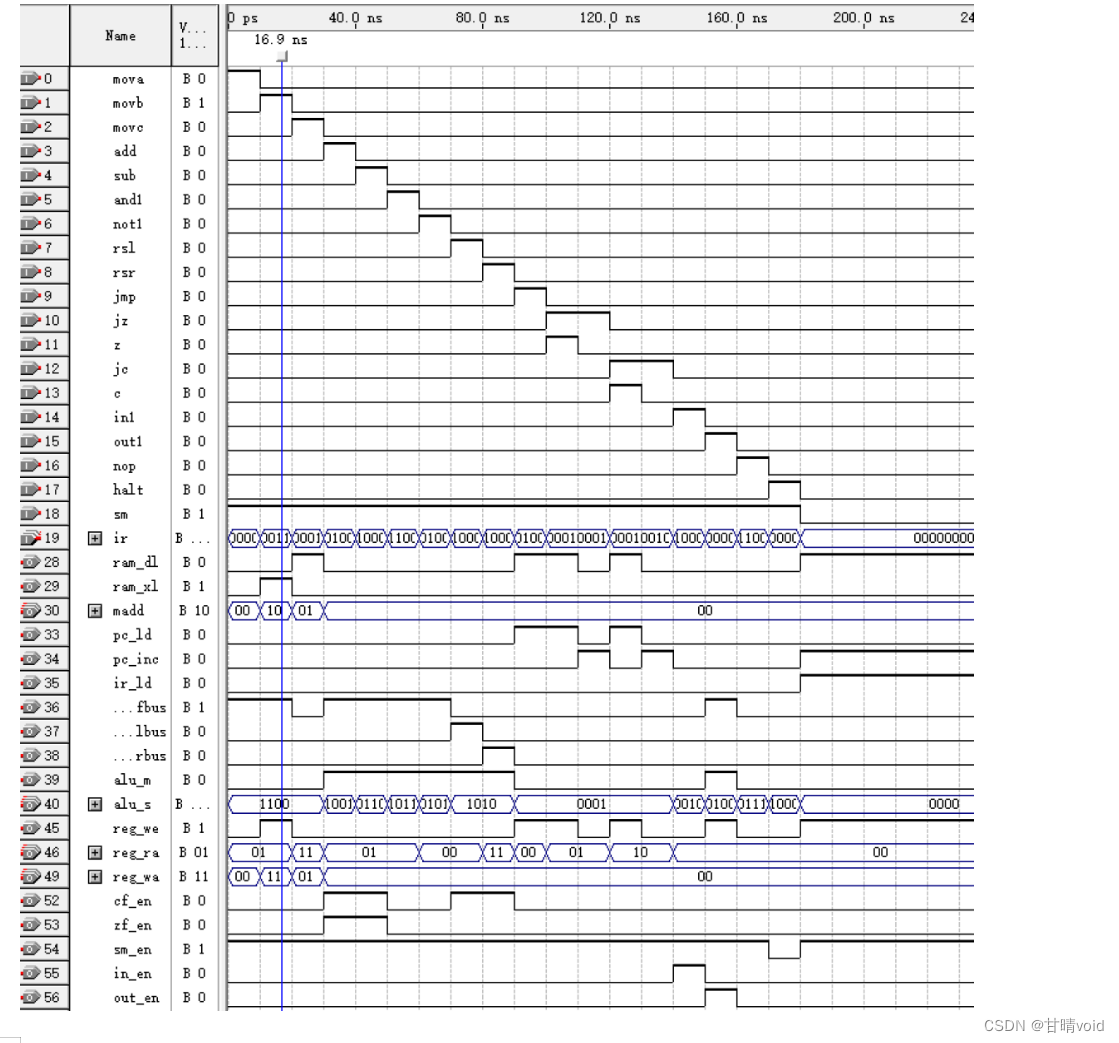

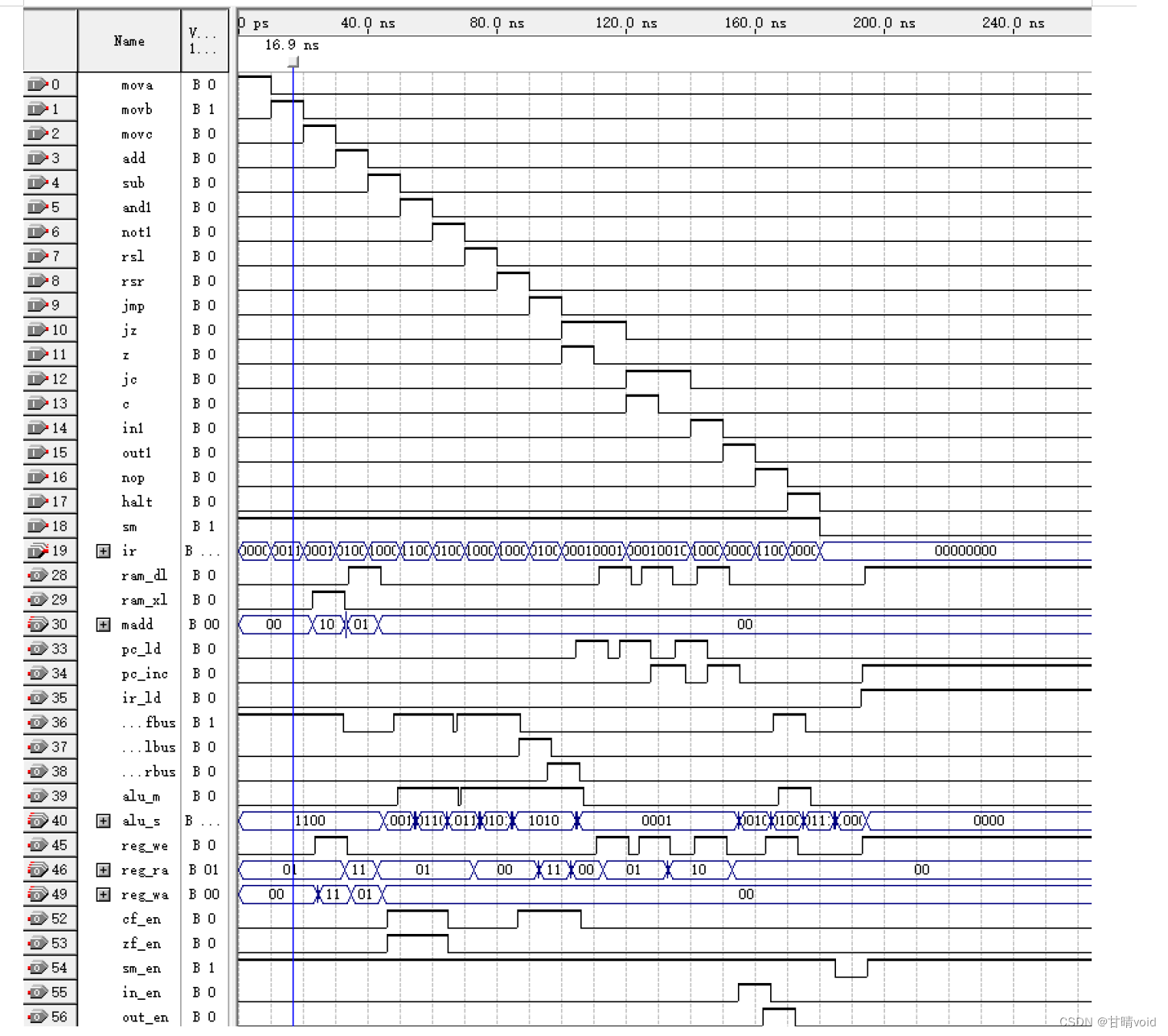

(3)功能仿真验证

结果分析及结论:

分析:功能仿真是指不考虑器件延时和布线延时的理想情况下对源代码进行逻辑功能的验

证。由仿真波形可得,对于输入状态的变化,输出结果实时变化,没有延迟,其结果与电路

设计的真值表的结果相对应。

(1)当 mova 指令执行时,shi_fbus 和 sm_en 输出 1,其他输出为 0,madd 输出 00,

alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 00,正确

(2)当 movb 指令执行时,ram_xl 和 shi_fbus 和 reg_we 和 sm_en 输出为 1,其他输出

为 0,madd 输出为 10,alu_s 输出为 1100,reg_ra 输出 01,reg_wa 输出 11,正确

(3)当 movc 指令执行时,ram_dl 和 sm_en 输出为 1,其他输出为 0,madd 输出 01,

alu_s 输出 1100,reg_ra 输出 11,reg_wa 输出 01,正确

(4)当 add 指令执行时,shi_fbus,alu_en,cf_en,zf_en,sm_en 输出为 1,其他输出

为 0,alu_s 为 1001,reg_ra 输出 01,reg_wa 输出 00,正确

(5)当 sub 指令执行时,shi_fbus 和 alu_m,cf_en,zf_en 和 sm_en 输出为 1,其他输

出为 0,alu_s 输出 0110,reg_ra 输出 01,reg_wa 输出 00,正确

(6)当 and1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s 输出

1011,reg_ra 输出 01,reg_wa 输出 00,正确

(7)not1 指令执行时,shi_fbus 和 alu_m 和 sm_en 输出 1,其他输出 0,alu_s 输出 0101,

reg_ra 输出 00,reg_wa 输出 00,正确

(8)rsl 指令执行时,shi_flbus 和 alu_m 和 cf_en 和 sm_en 输出 0,其他输出 0,alu_s

输出 1010,reg_ra 和 reg_wa 输出 00,正确

(9)rsr 指令执行时,shi_frbus 和 alu_m 和 cf_en 和 sm_en 输出 1,其他输出 0,alu_s

输出 10110,reg_ra 输出 11,reg_wa 输出 00,正确

(10)jmp 指令执行时,ram_dl,pc_ld,reg_we 和 sm_en 输出 1,其他输出 0,alu_s

输出 0001,reg_ra 和 reg_wa 输出 00,正确

(11)jz 指令为 1 和 jc 指令为 1 时,若 z 和 c 为 1 时,ram_dl 和 pc_ld 和 reg_we 和 sm_en输出为 1,其他输出为 0,正确

若 z 和 c 为 0 时,pc_inc 和 reg_we 和 sm_en 输出 1,其他输出 0,正确

(12)in1 指令执行时,sm_en 和 in_en 输出 1,其他输出 0,正确

(13)out1 指令执行时,sm_en 和 out_en 输出 1,其他输出 0,正确

(14)nop 指令执行时,sm_en 输出 1,其他输出 0,正确

(15)halt 指令执行时,输出全为 0,正确

结论:功能仿真操作简单,能体现和验证实验的功能,但忽略延迟的影响会使结果与实际结

果有一定误差。0,reg_ra 输出 11,reg_wa 输出 00,正确

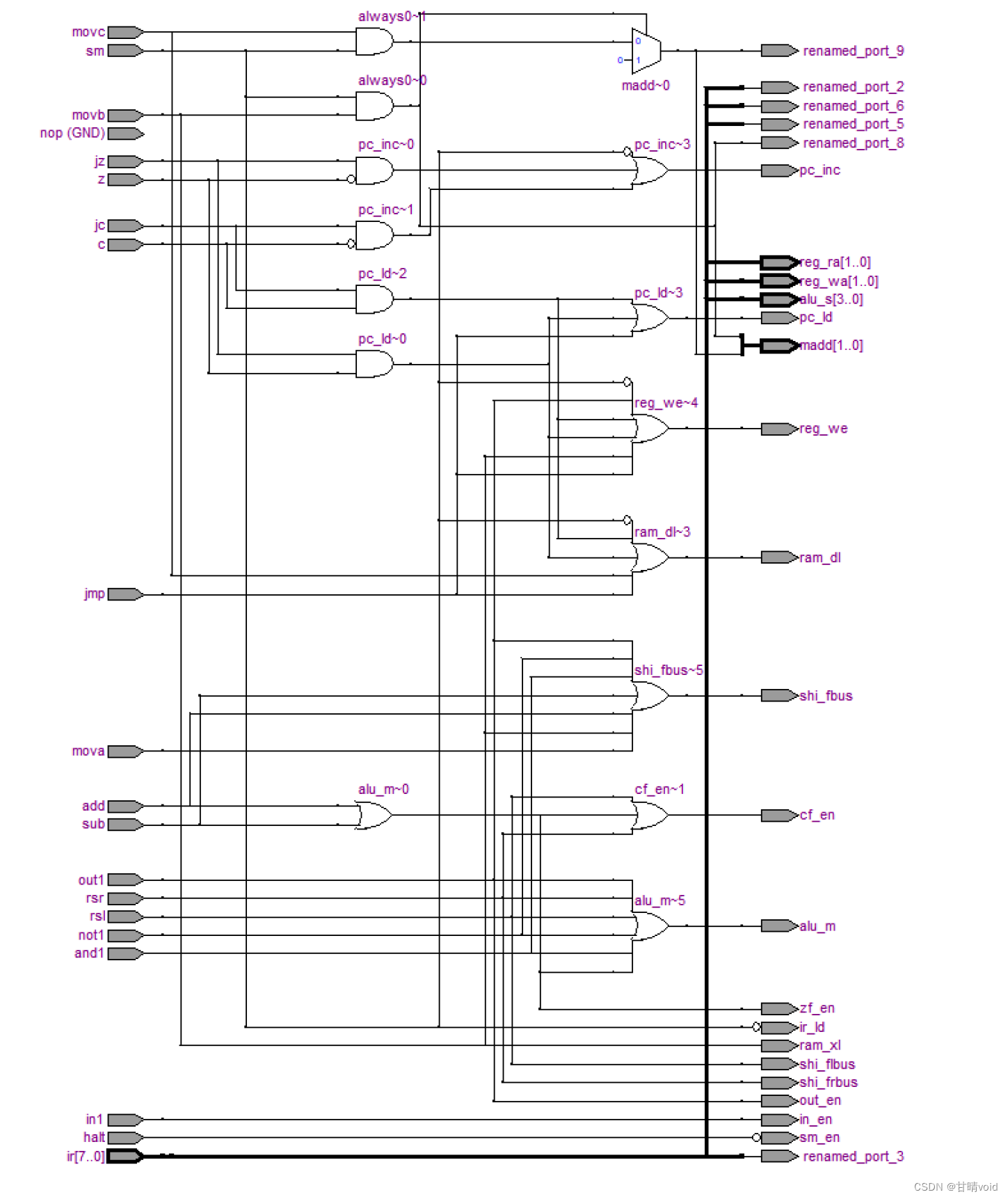

(4)RTL视图

结果分析:

由视图可得,视图左边为输入,右边为输出。其中连接有一系列的元器件。比如比较器:当输入相等时输出 1,不相等时输出 0;还有大部分的与或门。图中输入信号为 sm 等20 个,输出信号包括 reg_ra 等 19 种情况。各个输出端口之间通过导线相连。

结论:

一个功能的实现需要经过多重门的处理后才能实现,一个元件的内部原理结构图十分复杂。

(5)时序仿真验证

分析:

时序仿真是指在布线后进行,是最接近真实器件运行的仿真,它与特定的器件有关,

又包含了器件和布线的延时信息。由波形可得,当输入状态发生改变时,输出结果并未同时

改变,而是有一定延迟,同时由于输入状态的改变,导致电路出现“冒险”,导致输出结果

并未与预期结果相同。

结论:

时序仿真可以用来验证程序在目标器件中的时序关系。同时考虑了器件的延迟后,其

输出结果跟接近实际情况,但是考虑的情况过多,不容易操作,容易产生错误。时序仿真不

仅反应出输出和输入的逻辑关系,同时还计算了时间的延时信息,是与实际系统更接近的一

种仿真结果。不过,要注意的是,这个时间延时是仿真软件“估算”出来的。

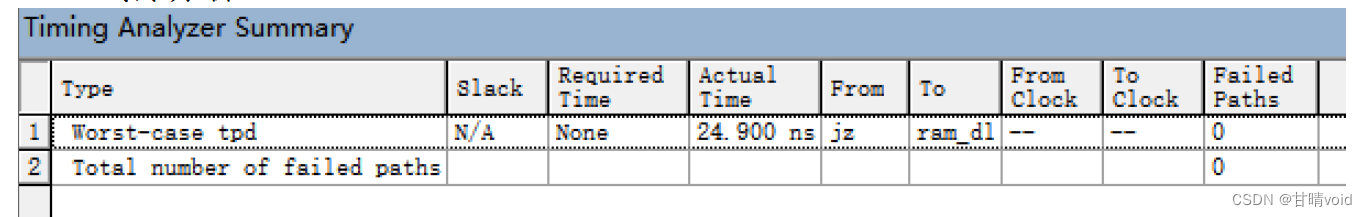

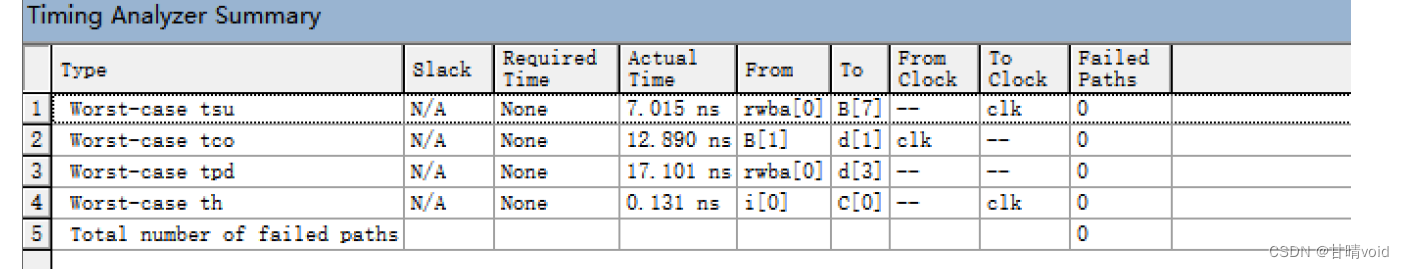

(6)时序分析

结果分析及结论:

分析:由图可得,Timing Analyzer Summmary 总结所有经典定时分析的结果,并报告每个

定时特性的最坏情况定时。比如从 sub 到 reg_we 的最坏定时情况的 tpd 为 26.600ns。下面 的 tpd 报告表则给出了源节点和目标节点之间的 tpd 延迟时间,比如第二行中 and1 到

reg_we 的 tpd 为 26.300ns。

结论:实际连接图中个元器件连接之间是存在时间延迟的,而且不同的元器件之间的时间延

迟也不相同。

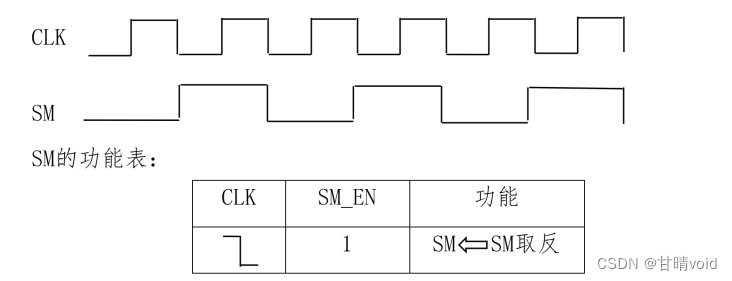

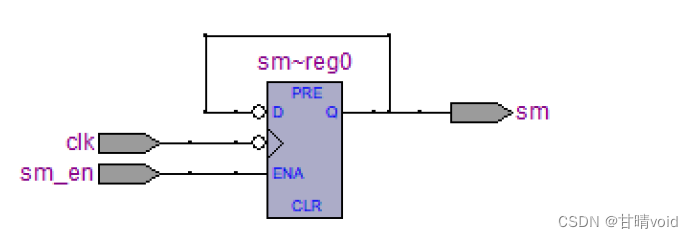

3.2.6 SM

(1)接口设计

input clk,sm_en;

output reg sm;

(2)功能实现

模型机中所有指令都要求两个周期完成,其中一个周期取指令,一个周期执行指令。如何区分当前周期是取指令还是执行指令呢?这就需要SM配合。SM为0是取指令周期;SM为1是执行指令周期。SM的功能及封装如下:

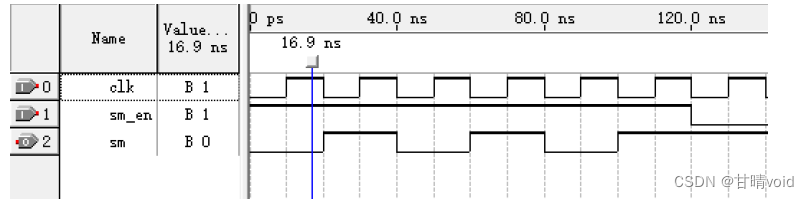

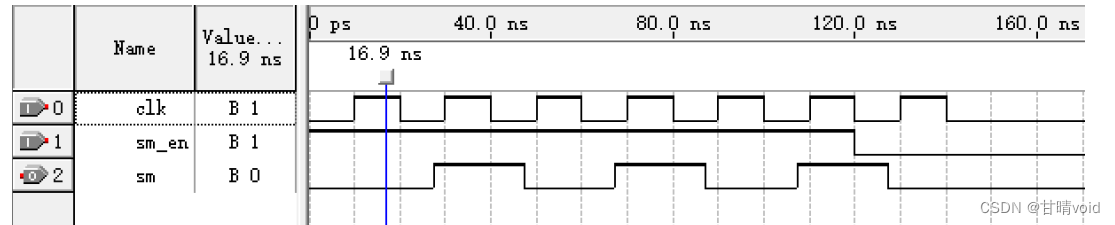

(3)功能仿真验证

分析:对于功能仿真,可以看到当 sm_en 信号为 1 有效时,输出 sm 在时钟的下降沿发生翻转, 符号功能设计。当 sm_en 信号为 0 时,输出信号 sm 保持不变,正确。

(4)RTL视图

(5)时序仿真验证

对于时序仿真,其输出结果和功能仿真类似,但存在 7ns 左右的延迟

结论:元件设计符合设计要求,元件内部存在 7ns 左右的延迟

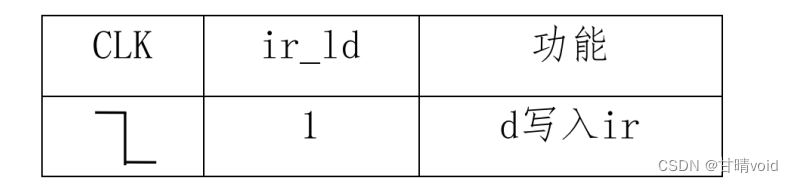

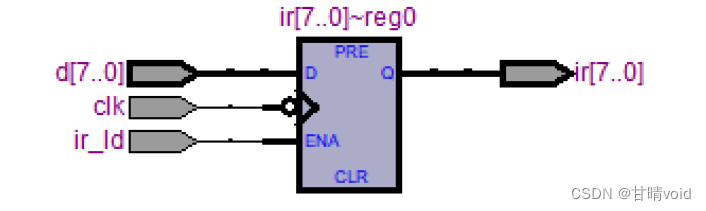

3.2.7指令寄存器 IR

(1)接口设计

input clk,ir_ld;

input [7:0] d;

output reg [7:0] ir;

(2)功能实现

指令寄存器(IR,Instruction Register)用于暂存当前正在执行的指令。

指令寄存器将总线送来的指令存入8位寄存器中,但并不是每次总线上的数据都需要寄存,因为数据总线上有时传输指令,有时传输数据。当控制信号IR_LD为1时,指令寄存器在时钟信号CLK的下降沿将总线传输的指令写入寄存器。

指令寄存器IR是一个8位寄存器。其功能及封装如下:

(3)功能仿真验证

分析:对于功能仿真,可以看到当 sm_en 信号为 1 有效时,输出 sm 在时钟的下降沿发生翻转, 符号功能设计。当 sm_en 信号为 0 时,输出信号 sm 保持不变,正确。

(4)RTL视图

(5)时序仿真验证

对于时序仿真,其输出结果和功能仿真类似,但存在 7ns 左右的延迟

结论:元件设计符合设计要求,元件内部存在 7ns 左右的延迟

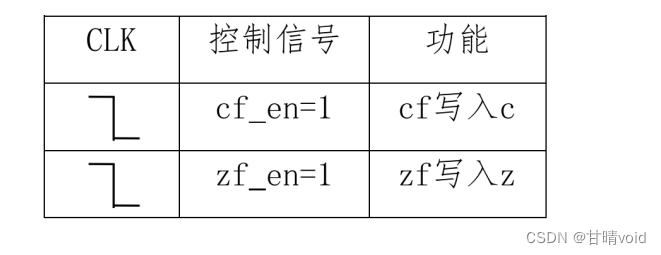

3.2.8状态寄存器 PSW

(1)接口设计

input clk,cf_en,zf_en,cf,zf;

output reg c,z;

(2)功能实现

状态寄存器PSW是计算机系统的核心部件——运算器的扩展部分。本模型机

PSW用来存放ADD、SUB、RSR、RSL指令执行结果的状态标志,如有无借位进位(C)、 结果是否为零(Z)。有些机器也将PSW称为标志寄存器FR(Flag Register)。 本模型机PSW是一个2位寄存器。其功能及封装如下:

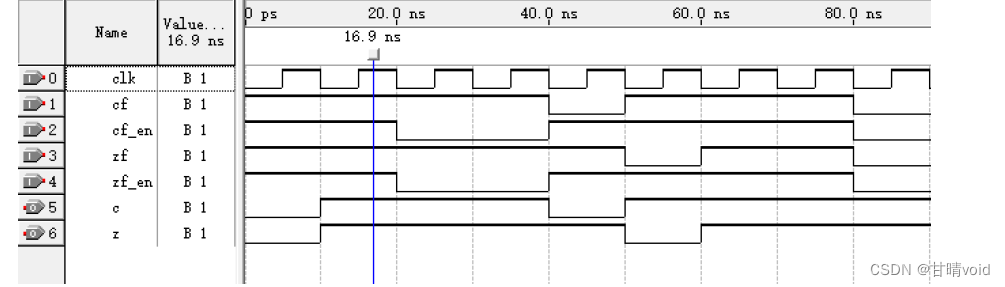

(3)功能仿真验证

分析:对于功能仿真,0-20ns,cf_en 和 zf_en 为 1,在时钟下降沿,将 cf 和 zf 的值写入输出 c,z 中,20-40ns,cf_en 和 zf_en 为 0,输出 c 和 z 保持不变,正确

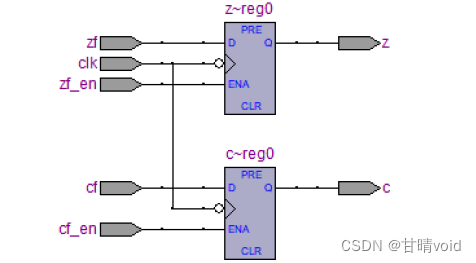

(4)RTL视图

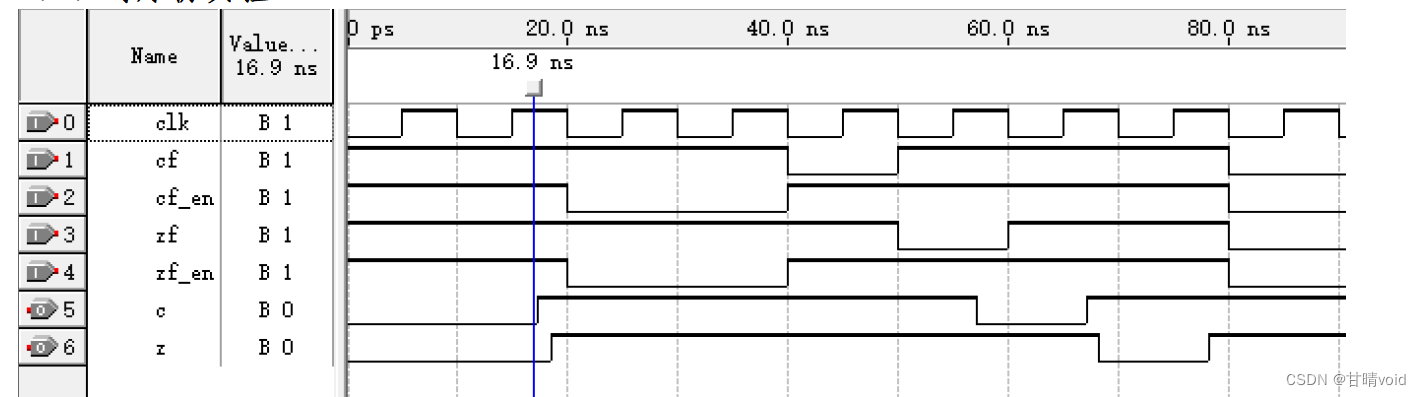

(5)时序仿真验证

对于时序仿真,其中输出c有7ns 左右延迟z有 8ns 左右延迟,其输出变化与功能仿真大致相同。结论:元件设计符合要求,输出c有 7ns 延迟,输出z有8ns 延迟。

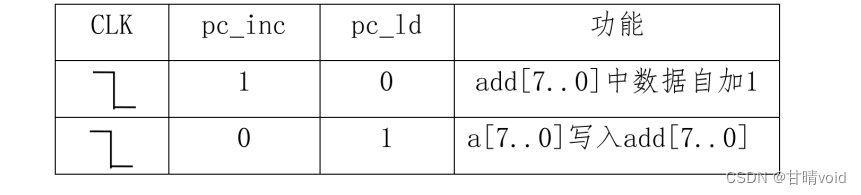

3.2.9指令计数器 PC

(1)接口设计

input clk,pc_ld,pc_inc;

input [7:0] a;

output reg [7:0] add;

(2)功能实现

指令计数器PC存储当前指令在RAM中存放的地址。 CPU执行一条指令,根据PC中存放的指令地址,将指令从RAM读出写入指令寄存器IR中,此过程称为“取指令”。在每条指令读取后,指令计数器PC中的地址 自动加1,指向下一条指令在RAM中的存放地址。跳转指令如JMP、JZ、JC让程序跳转至指定地址去执行,这时PC需要装载跳转地址。

模型机的指令计数器PC是一个8位计数器,其的功能及封装如下:

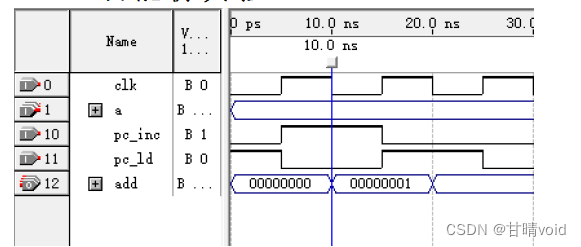

(3)功能仿真验证

分析:对于功能仿真,5-15ns,pc_inc 为 1,pc_ld 为 0,执行地址加 1 操作,15ns-25ns,pc_inc 为 0,pc_ld 为 1,执行写入操作,将输入写入到输出中,25-40ns,pc_inc 为 0,pc_ld 为

数据保持不变,正确。

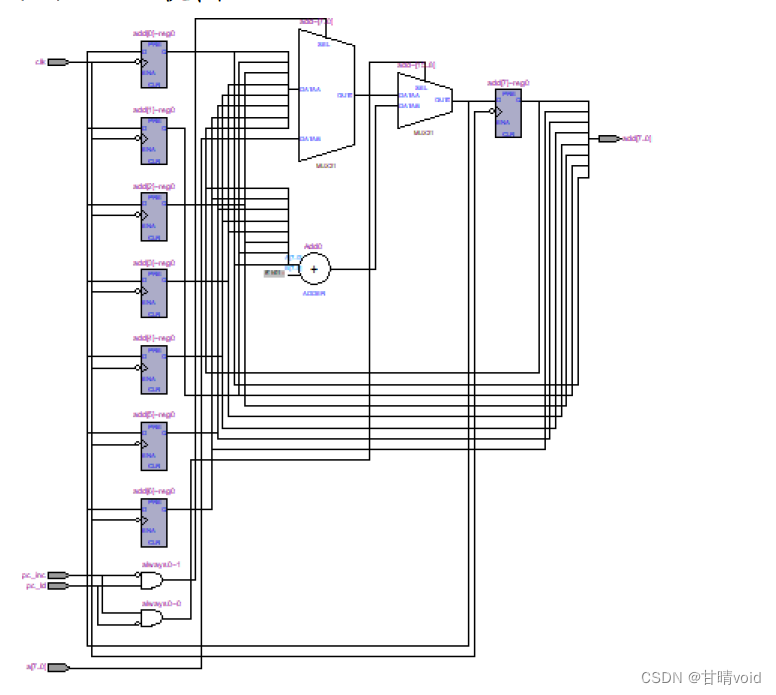

(4)RTL视图

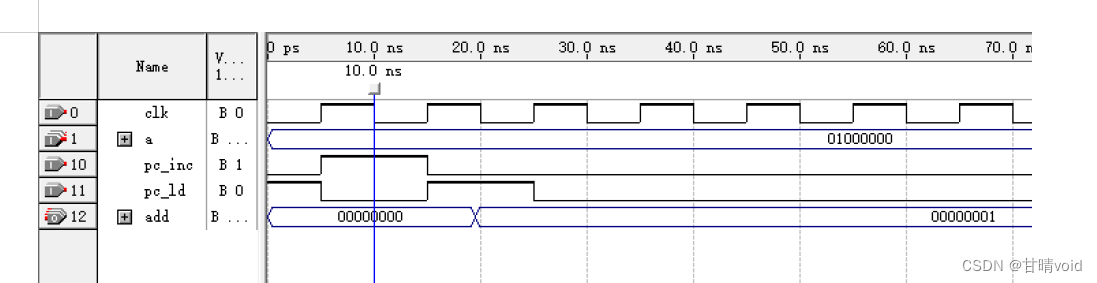

(5)时序仿真验证

对于时序仿真,存在 9ns 左右的延迟,输出结果大致与功能仿真相同

结论:元件设计符合要求,元件存在 9ns 左右的延迟

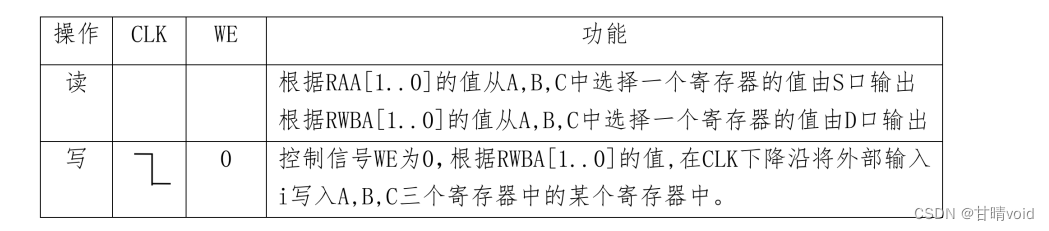

3.2.10寄存器组

(1)接口设计

input clk,we;

input [1:0] raa,rwba;

input [7:0] i;

output reg [7:0] s,d;

output reg [7:0] A,B,C;

(2)功能实现

寄存器主要用来保存操作数和运算结果等信息,从而节省从RAM中读取操作

数所需占用总线和访问存储器的时间。

模型机的通用寄存器组包含3个8位寄存器A、B、C,可对这3个寄存器进行读

写操作。其功能及封装如下:

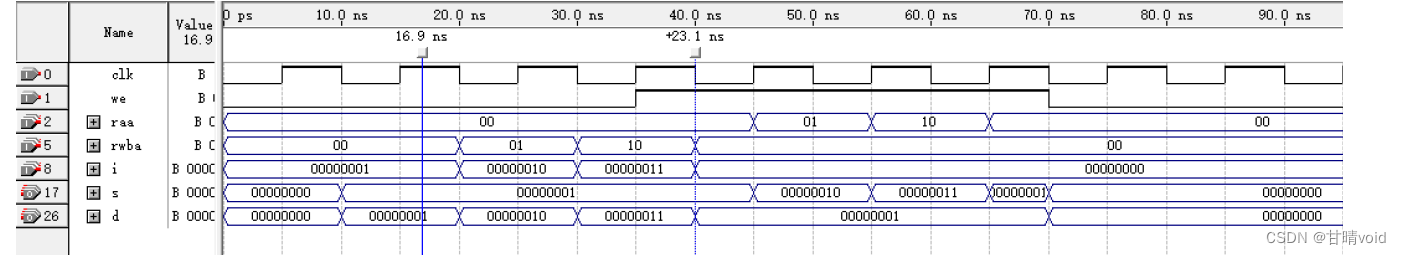

(3)功能仿真验证

对于功能仿真,在 0-35ns,we 为 0,进行写入操作,在每个下降沿,当 rwba=00,01,10

时,将输入 i 分别写入寄存器 A,B,C 中,而在 35-65ns,we 为 1,进行读取操作,在每个下降沿,根据 raa 和 rwba 的值 s,d 输出对应寄存器的值,当 raa=00,s 输出 A 的值,raa=01,s 输出 B 的值,raa=10,s 输出 C 的值,正确

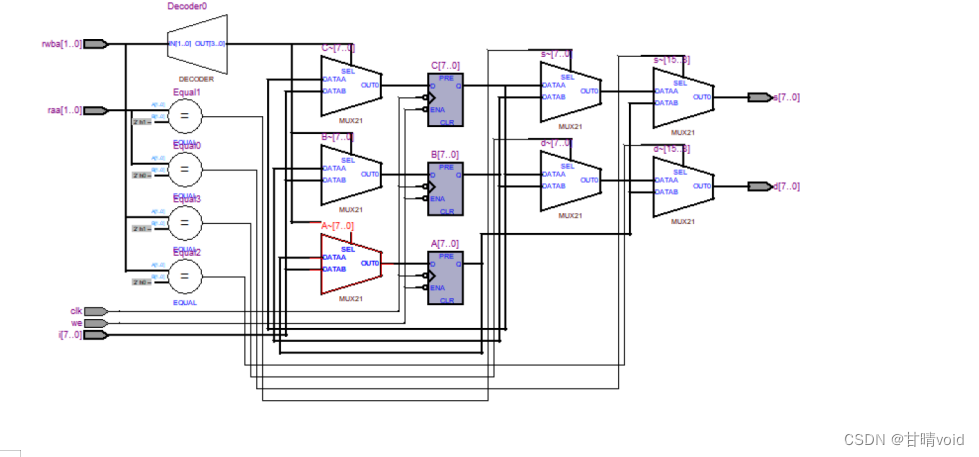

(4)RTL视图

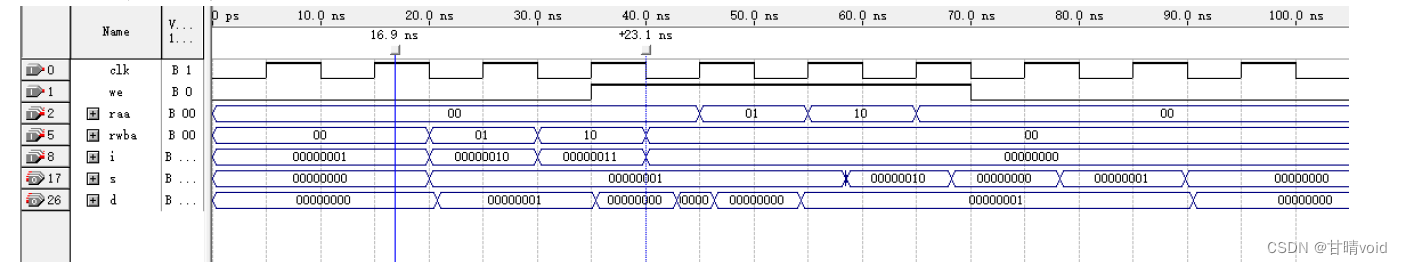

(5)时序仿真验证

对于时序仿真,输出 s 存在 9ns 左右的延迟,输出 d 存在 10ns 左右延迟,其余输出结果大致与功能仿真相同。

(6)时序分析

对于时序分析,可以得到时钟输出延迟 tco 为 13.487ns,建立时间 tsu 为 7.110ns,保持时间 th 为 0.479ns,电路延迟时间 tpd 为 16.353ns

结论:元件设计符合要求,输出 s 存在 9ns 左右的延迟,输出 d 存在 10ns 左右延迟

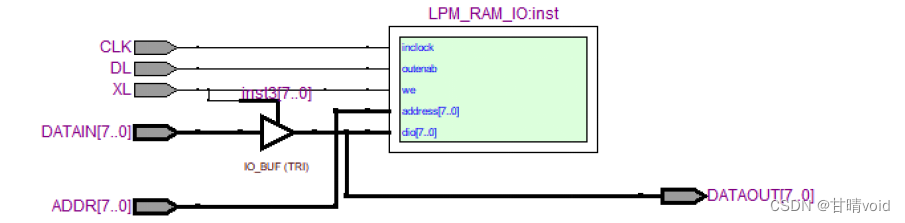

3.2.11 RAM

(1)接口设计

输入:address[7..0]、inclock、we、outenab

输出:dio[7..0]

(2)功能实现

半导体存储器的种类很多,从功能上可以分为只读存储器ROM和随机存储RAM两大类。随机存储器RAM是与CPU直接交换数据的内部存储器,也叫主存(内存)。它可以随时读写,而且速度很快,通常作为操作系统或其他正在运行中的程序的临

时数据存储媒介。

存储元是构成存储器的存储介质,它可存储一个二进制位。由若干个存储元组成一个存储单元,然后再由许多存储单元组成一个存储器。一个存储器包含许多存储单元,每个存储单元可存放一个字节。每个存储单元的位置都有一个编号,即地址,一般用十六进制表示。一个存储器中所有存储单元可存放数据的总和称为它的存储容量。比如,一个存储器的地址码由8位二进制数(即2位十六进制数)

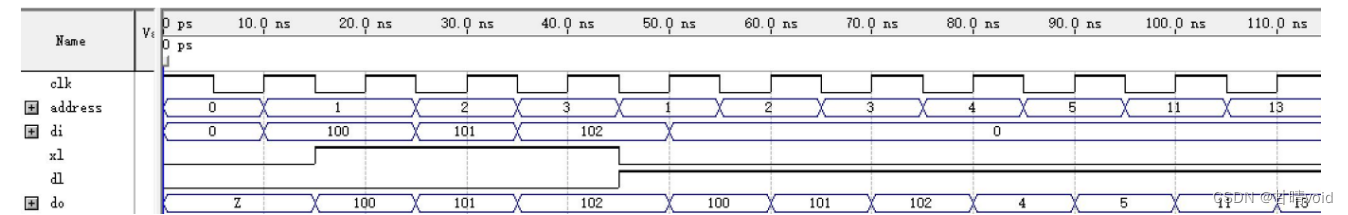

(3)功能仿真验证

对功能仿真,0-15ns,xl 和 dl 都为 0,输出为高阻态。15-45ns,xl 为 1,dl 为 0,

进行写入操作,对于三个上升沿,分别将输入信号 100,101,102 分别写入地址 1,2,3 中。

45-115ns,xl 为 0,dl 为 1,进行读操作,对于每个上升沿,分别将 1,2,3,4,5,11,13 地址

中的指令读出并输出,其中 4,5,11,13 地址中的指令已提前存入对应的 mif 文件中,仿真正确。

(4)RTL视图

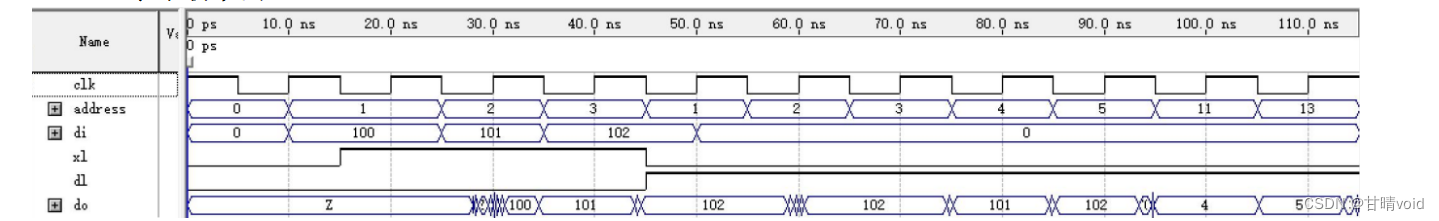

(5)时序仿真验证

对于时序仿真,输出存在 11ns 左右的延迟,同时由于输入的改变导致某些位置出现冒险。

四、系统测试

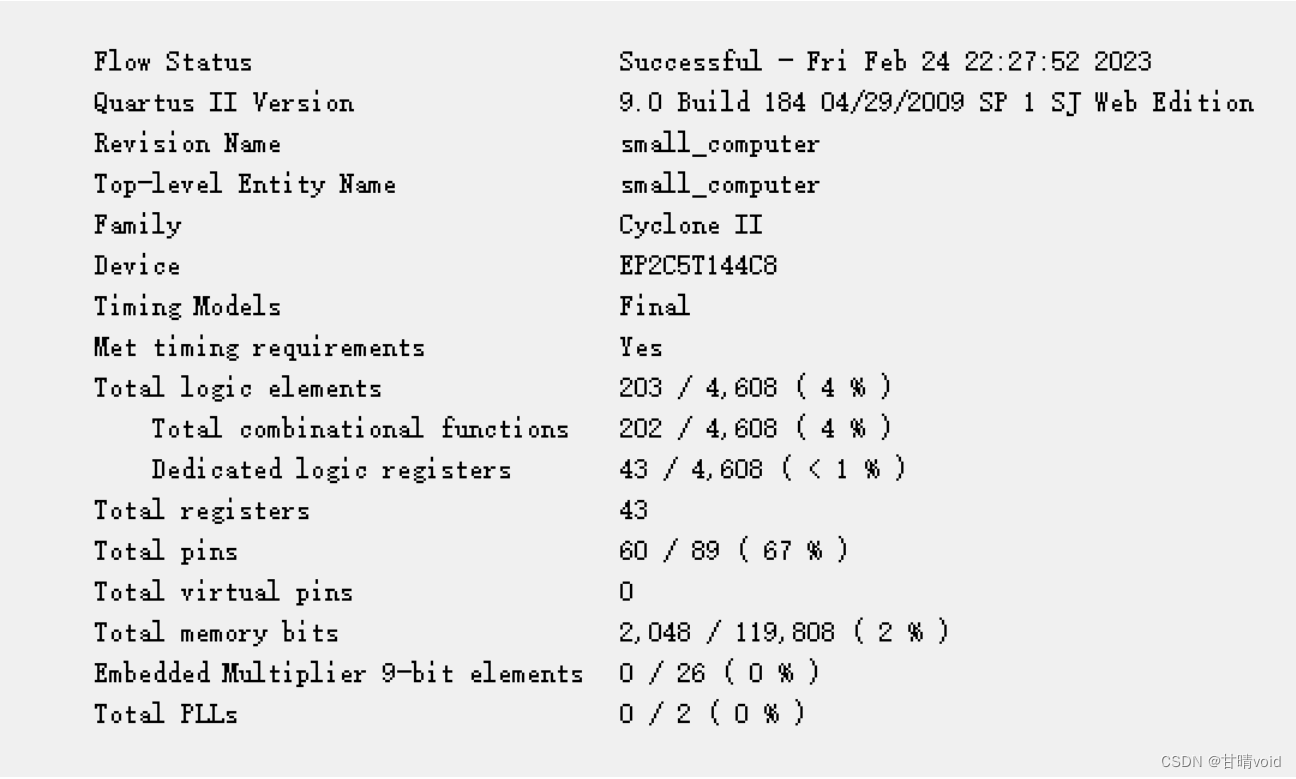

4.1 测试环境

Quartus II 9.0sp1 Web Edition

Cyclone II:EP2C5T144C8

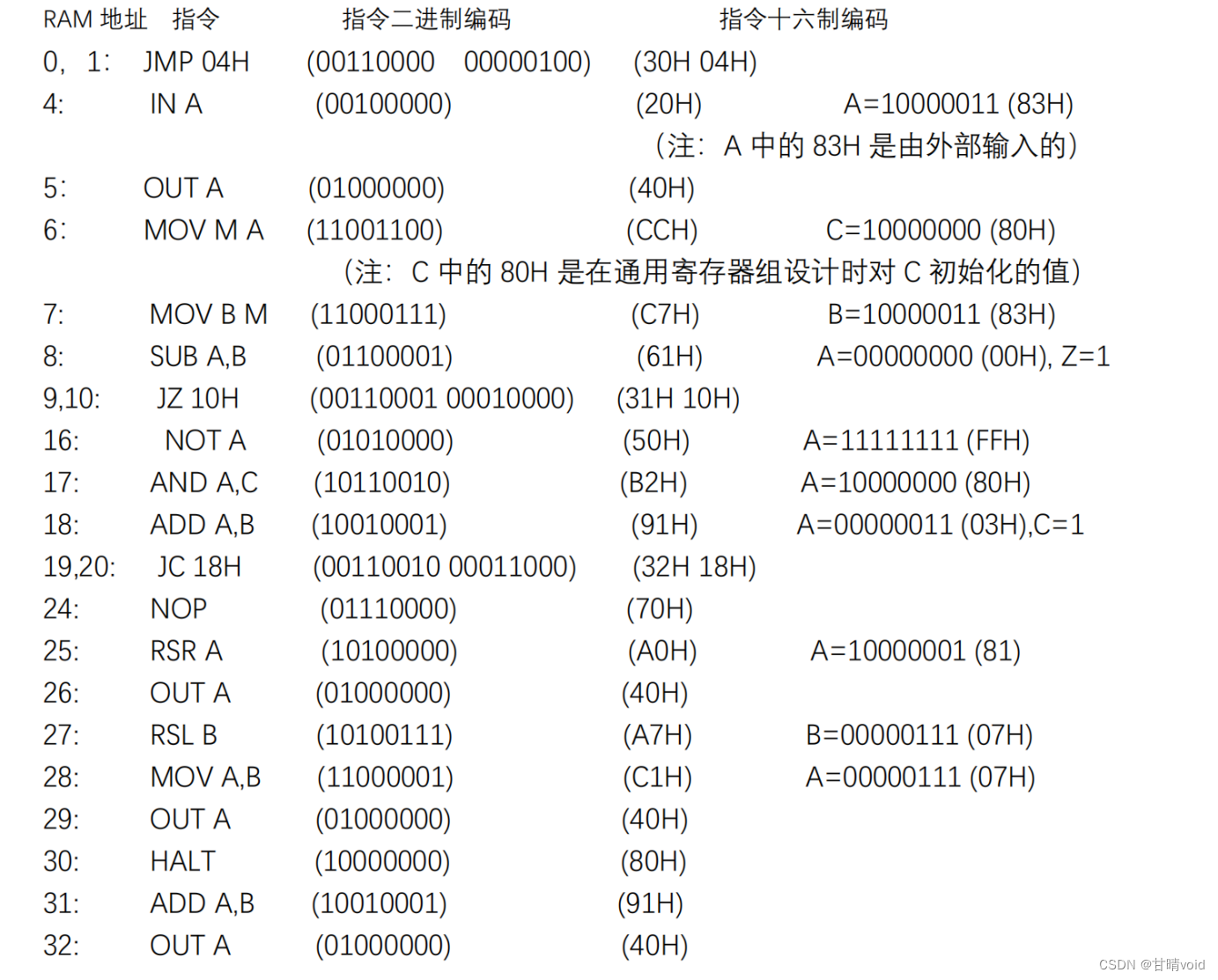

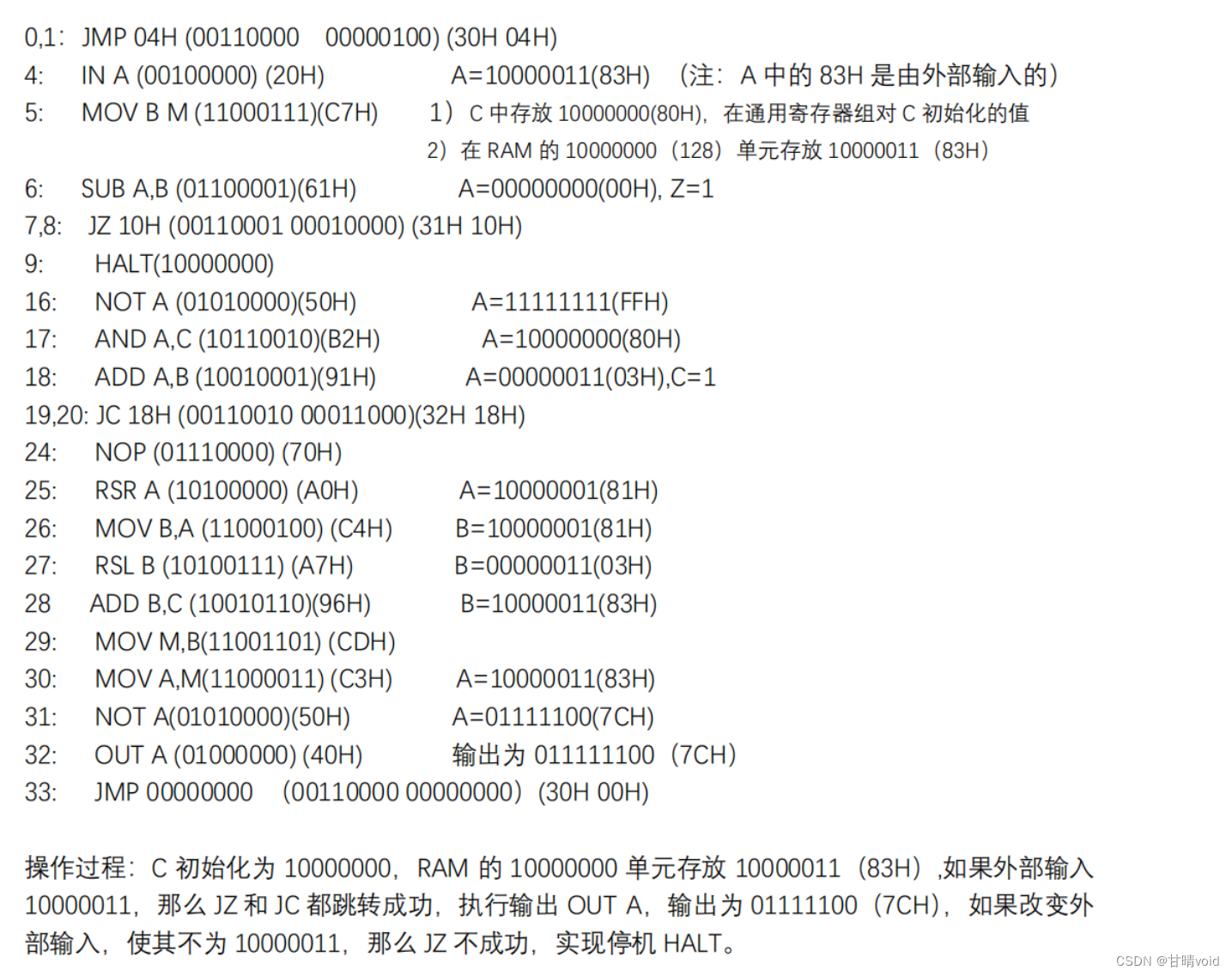

4.2 测试代码

(使用模型机实现的指令编写一至两个程序测试模型机的正确性。)

测试代码1:

测试代码2:

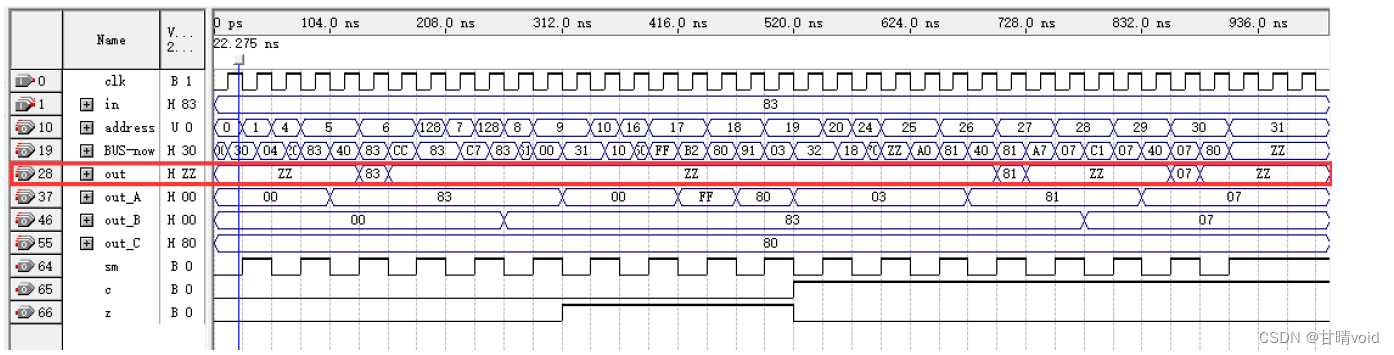

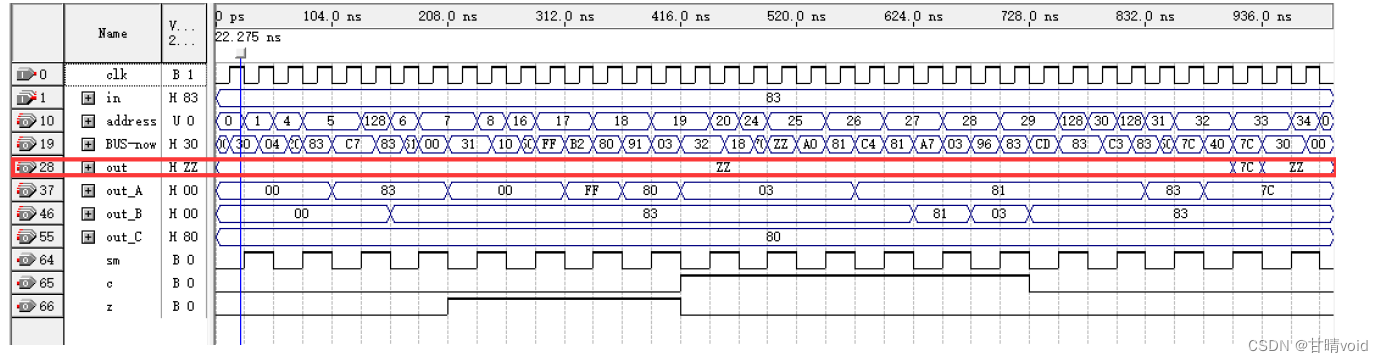

4.3测试结果

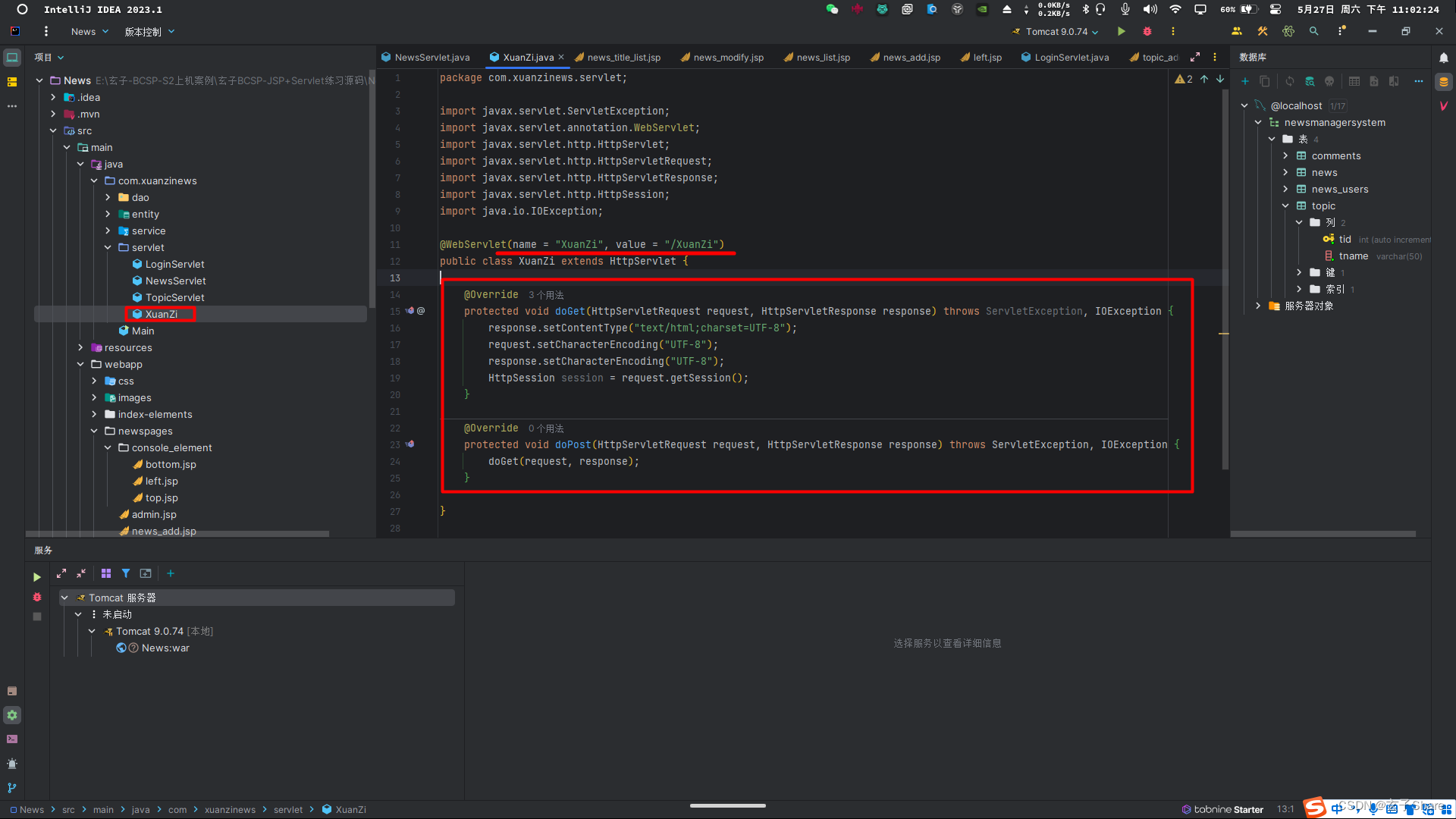

(为了测试方便与监控变量变化,我输出了多个中间变量,红框处为输出值)

测试结果1:

测试结果2:

4.4 模型机性能分析

五、实验总结、必得体会及建议

5.1 从需要掌握的理论、遇到的困难、解决的办法以及经验教训等方面进行总结。

(1)需要掌握的理论:基本了解了简易模型机的内部结构和工作原理。同时熟悉了指令寄存器、状态寄存器、指令计数器、寄存器的工作原理。学会使用 Verilog 语言编写电路。

(2)遇到的困难:主要是对于不同模块的整合不够熟练,由于是第一次接触到这个技能,显得很生疏。特别是如果一次搭建完整,会遇到无法确定错误位置的情况。

(3)解决方法:使用迭代增量的方法进行搭建,也就是说我先搭建其中的一部分,然后用几个输入引脚确认一下看看输出是否符合预期,这样就可以及时发现错误的位置并且作出改变。其他的问题还可以通过上网查询相关资料和询问同学后得以解决问题,并通过分析报告发现电路中的问题。有不理解的还请教了老师,不仅收获了方法还掌握了技巧。

(4)经验教训:对于电子电路的学习一定要肯动手,光是看是学不会的,一定要落到实处,多自己使用软件进行仿真,才能加深对于这门课程的理解。

5.2 对本实验内容、过程和方法的改进建议(可选项)。

对于RTL视图的研究十分重要,可以引导同学做到自己能看懂RTL视图,否则需要更改并简化写法。一定要形成能够通过RTL视图理顺思路、发现问题并解决问题的能力。