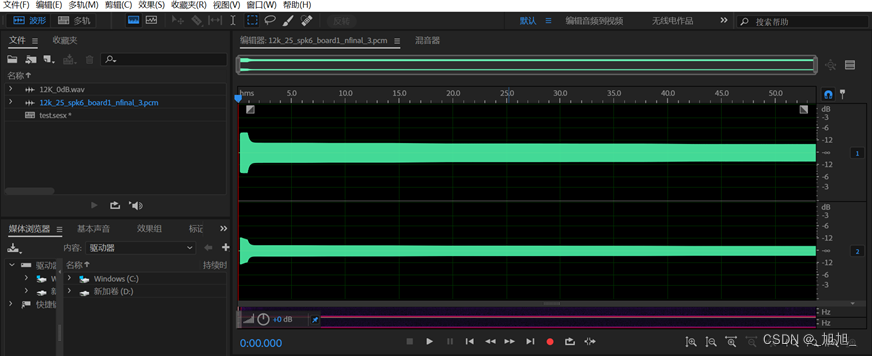

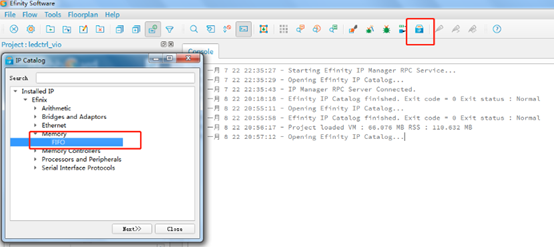

一、软件设置界面

FIFO(First In First Out,即先入先出),是一种数据缓冲器,用来实现数据先入先出的读写。与 ROM 或 RAM 的按地址读写方式不同, FIFO 的读写遵循“先进先出”的原则,即数据按顺序写入 FIFO,先被写入的数据同样在读取的时候先被读出,所以 FIFO存储器没有地址线。FIFO 有一个写端口和一个读端口外部无需使用者控制地址,使用方便。

FIFO 存储器主要是作用为缓存,应用在同步时钟系统和异步时钟系统中,在很多的设计中都会使用如:多比特数据做跨时钟域的转换、前后带宽不同步等都用到了异步FIFO,示意图如下。 FIFO 根据读写时钟是否相同,分为 SCFIFO(同步 FIFO)和 DCFIFO(异步FIFO),SCFIFO 的读写为同一时钟,应用在同步时钟系统中; DCFIFO 的读写时钟不同,应用在异步时钟系统中。

易灵思fpga的FIFO使用没有什么特殊需要注意的事项,也是可视化界面,根据界面的定义即可正常设置,生成FIFO.

下面详细介绍FIFO生成的步骤。

打开任意工程,在IPM菜单栏里面,双击FIFO IP ;

生成IP ,需要在module name 处 命名,

在配置界面根据需要,使能某些指示信号;

右下角点击generate生成。

二.

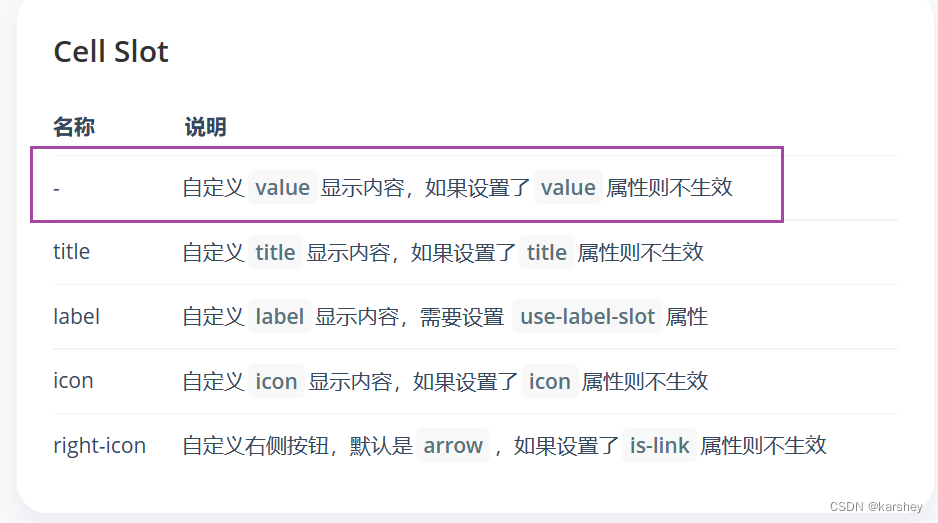

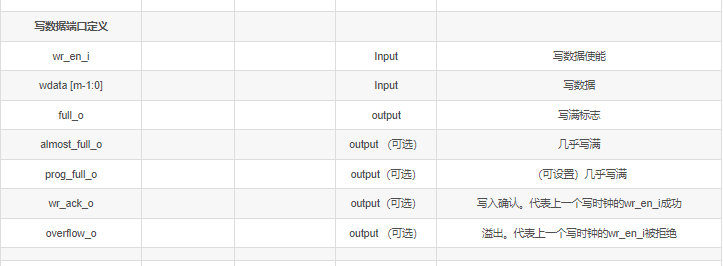

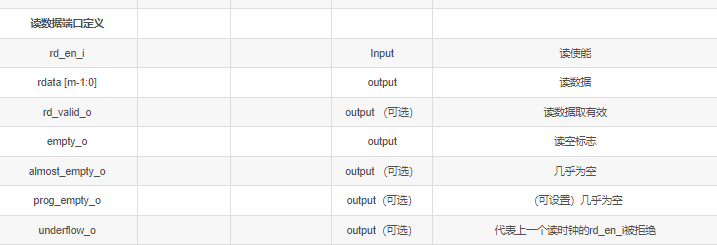

FIFO端口定义

三.

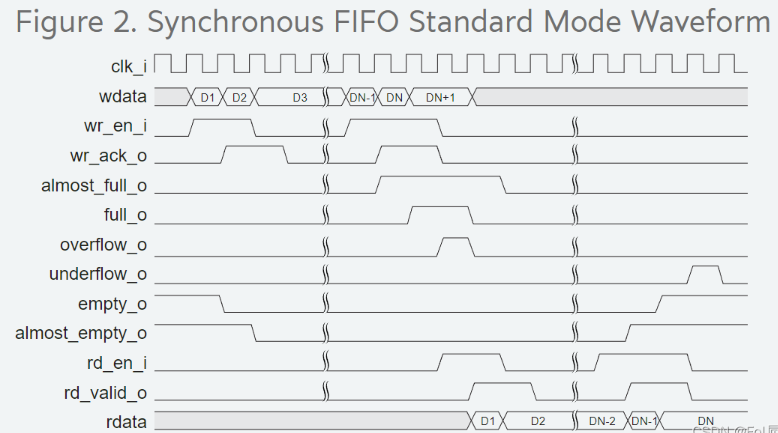

FIFO时序

同步FIFO标准模式

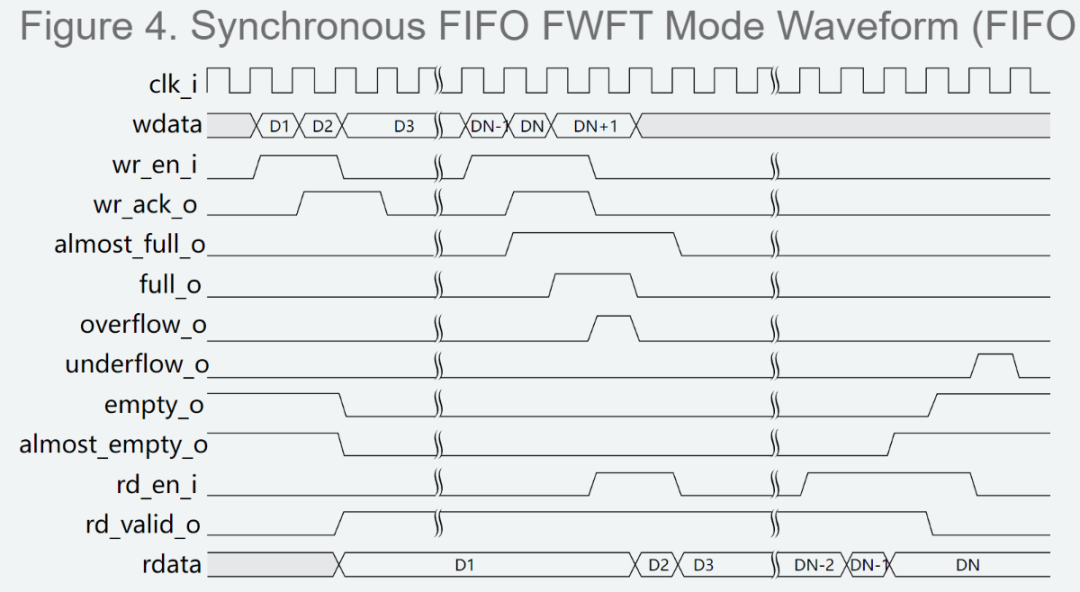

同步FIFO FWFT模式

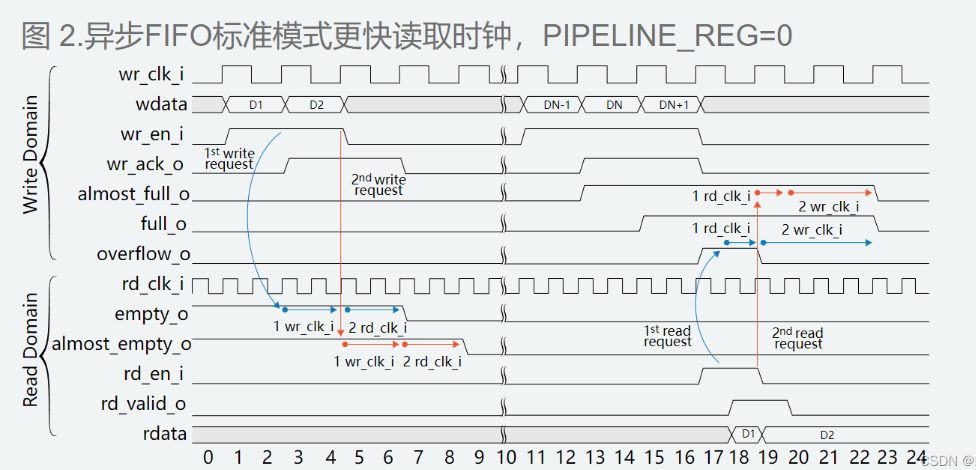

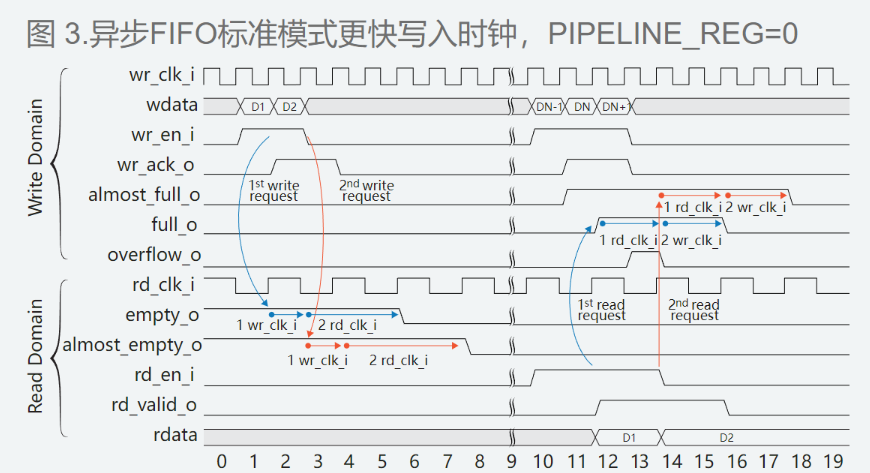

异步FIFO标准模式

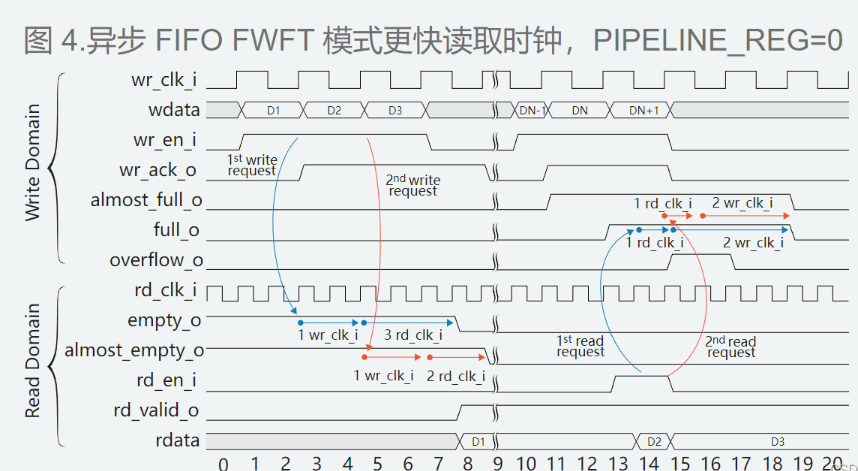

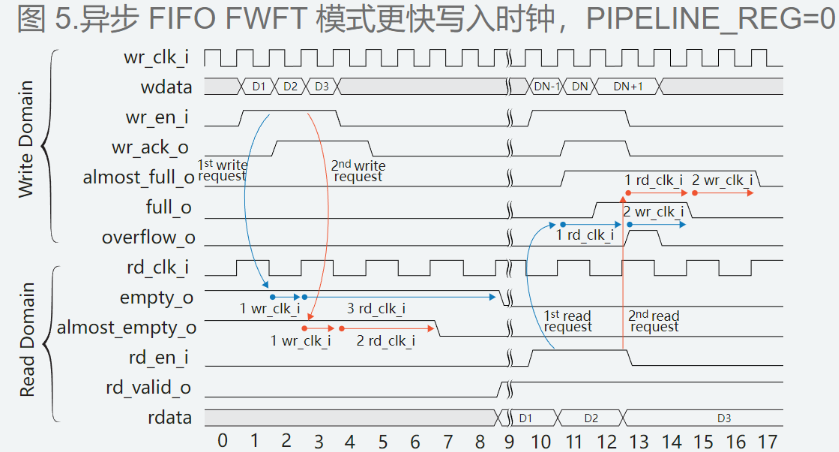

异步FIFO FWFT模式

更多关于易灵思FPGA的应用详见下面链接:

新品上线--易灵思(EFINIX)FPGA 编程器

易灵思FPGA之---国产化替代选型策略

国产易灵思FPGA的PLL用法集锦

国产FPGA应用专题--易灵思Efinity软件使用心得

好消息!纯国产化易灵思T20核心板隆重发售!