HLS入门实践

文章目录

- HLS入门实践

- 1.HLS基本知识简述

- 1.1 HLS简介

- 1.2 HLS相关知识概念

- 2. HLS技术认识

- 2.1 与VHDL/Verilog关系

- 2.2 关键技术问题

- 2.3 存在的技术局限性

- 3. HLS 完成 led 灯闪烁

- 3.1. 新建一个 HLS 工程

- 3.2 添加源文件

- 3.2.1 led.h

- 3.2.2 led.cpp

- 3.2.3 添加 C 仿真文件

- 3.2.4 进行 C 仿真与 C 综合

- 3.2.5 联合仿真

- 3.3 导出IP 核

- 3.4 创建 Vivado 工程

- 4.总结

- 参考文章

1.HLS基本知识简述

1.1 HLS简介

HLS(High-Level Synthesis)高层综合,就是将 C/C++的功能用 RTL 来实现,将 FPGA 的组件在一个软件环境中来开发,这个模块的功能验证在软件环境中来实现,无缝的将硬件仿真环境集合在一起,使用软件为中心的工具、报告以及优化设计,很容易的在 FPGA 传统的设计工具中生成 IP。

传统的 FPGA 开发,首先写 HDL 代码,然后做行为仿真,最后做综合、时序分析等,最后生成可执行文件下载到 FPGA 使用,开发周期比较漫长。

使用 HLS,用高级语言开发可以提高效率。

因为在软件中调试比硬件快很多,在软件中可以很容易的实现指定的功能,而且做 RTL仿真比软件需要的时间多上千倍。

1.2 HLS相关知识概念

HLS是高层综合(High level Synthesis),是将C或者c++语言编译为FPGA能够读懂和运行的RTL级别的语言。

HLS包含下面这些阶段

- scheduling:确定每个时钟周期中执行哪些步骤

- Binding:确定哪些硬件资源会被用到

- 控制逻辑提取:提取控制逻辑,创建一个有限状态机(FSM:Finite state machine)来进行RTL的设计。

HLS需要对相应的c代码进行下面的综合

- Area:用到的LUT,寄存器,BRAM和DSP48的数量

- 时延:函数算出所有输出用的时钟周期

- II(Initiation interval):函数可以接受新的输入数据需要的时钟周期

- 循环迭代时延:运行一次循环需要的时钟周期

- 循环间隔时延:新运行一次循环需要的时钟周期

- 循环时延:运行循环需要的所有时钟周期

vivado HLS需要进行的步骤

- 编译、执行(仿真)、调试相应的c语言代码

- 把c算法综合为RTL实现,在这个过程中可以使用优化指令

- 生成综合分析报告并分析设计

- 验证RTL的实现

- 打包RTL进入IP块

vivado HLS软件需要的输入信息

- c函数用c/c++、SystemC、OpenCL API或者C kernel写成

- Constrains:资源限制,例如时钟周期、时钟不确定性、与FPGA目标板

- Directives:可选的过程,来实现特定的优化

- c测试台(c test bench)与相关文档

- HLS用c测试台来仿真c代码并且验证相应用c/RTL联合仿真得到的RTL输出

vivado HLS软件输出的信息

- RTL实现文件,用HDL(hardware description language)语言写成,这是最重要的输出,有两种模式,VHDL语言和Verilog语言。这种实现文件会被作为IP块,并且可以被其他xilinx的设计工具所使用。

- 报告文档:综合、c/RTL协同仿真、IP封装的输出结果。

Synthesis,optimization,analysis

- 创建工程,初始solution

- 验证相应的c没有错误

- 运行synthesis获得一系列结果

- 分析结果

在HLS中有下面这些优化方法

- pipeline,在上个进程运行结束前开始下个进程

- 给函数、循环、区域指定时延

- 针对具体的操作指令同时运行

- 选择相应的I/O协议确保硬件可以与其他的设施相连接

2. HLS技术认识

2.1 与VHDL/Verilog关系

在 FPGA 硬件开发上,VHDL/Verilog 与 HLS 相比,就好比是几十年前的汇编语言与现在的 C 语言。RTL(寄存器传输级别,基于 VHDL/Verilog 语言)逐步发展,但 VLSI 系统的复杂性呈指数级增长,使 RTL 设计和验证过程成为生产力的瓶颈。

HLS(高级综合)通过提高抽象级别, 可以减少最初的设计工作量,设计人员可以集中精力描述系统的行为,而不必花费时间来实现微体系结构的细节,且验证被加速、设计空间探索(DSE)更快、定位新平台非常简单、软件工程师可以访问 HLS 等这些好处加在一起,减少了设计和验证时间,降低了开发成本,并降低了进行硬件项目的门槛,因此缩短了产品上市时间,并且在异构系统上使用硬件加速已成为更具吸引力的选择。但是在结果质量(QoR)上,HLS 工具还落后于 RTL,但 HLS 的开发时间少、生产率高这些优点还是当前用于快速原型设计和较短上市时间的可行选择。

2.2 关键技术问题

字长分析和优化

FPGA 的一个最主要特点就是可以使用任意字长的数据通路和运算。因此,FPGA 的 HLS 工具不需要拘泥于某种固定长度(如常见的 32 位或 64 位)的表达方式,而可以对设计进行全局或局部的字长优化,从而达到性能提升和面积缩减的双重效果。

循环优化

循环优化一直是 HLS 优化方法的研究重点和热点,因为这是将原本顺序执行的高层软件循环有效映射到并行执行的硬件架构的重点环节。

一个流行的循环优化方法,就是所谓的多面体模型,即 Polyhedral Model。多面体模型的应用非常广泛,在 HLS 里主要被用来将循环语句以空间多面体表示,然后根据边界约束和依赖关系,通过几何操作进行语句调度,从而实现循环的变换。需要指出的是,多面体模型在 FPGA HLS 里已经取得了相当的成功,很多研究均证明多面体模型可以帮助实现性能和面积的优化,同时也能帮助提升 FPGA 片上内存的使用效率。

对软件并行性的支持

C/C++与 RTL 相比,一个主要的区别是,前者编写的程序被设计用来在处理器上顺序执行,而后者可以通过直接例化多个运算单元,实现任务的并行处理。

随着处理器对并行性的逐步支持,以及如 GPU 等非处理器芯片的兴起,C/C++ 开始逐渐引入对并行性的支持。例如,出现了 pthreads 和 OpenMP 等多线程并行编程方法,以及 OpenCL 等针对 GPU 等异构系统进行并行编程的 C 语言扩展。

因此作为 HLS 工具,势必要增加对这些软件并行性的支持。例如,LegUp 就整合了度 pthreads 和 OpenMP 的支持,从而可以实现任务和数据层面的并行性。

2.3 存在的技术局限性

- 字长分析和优化需要 HLS 的使用者对待综合的算法和数据集有深入的了解,这也是限制这种优化方式广泛使用的主要因素之一。

- HLS 工具的结果质量(QoR)往往落后于手动寄存器传输级别(RTL)流程的质量。

- 在性能和执行时间上,HLS 设计的平均水平明显较差,但在延迟和最大频率方面,与 RTL 差异不那么明显,且 HLS 方法还会浪费基本资源,平均而言,HLS 使用的基本 FPGA 资源比 RTL 多 41%,在以千位为单位的 BRAM 使用情况的论文中,RTL 更胜一筹。

3. HLS 完成 led 灯闪烁

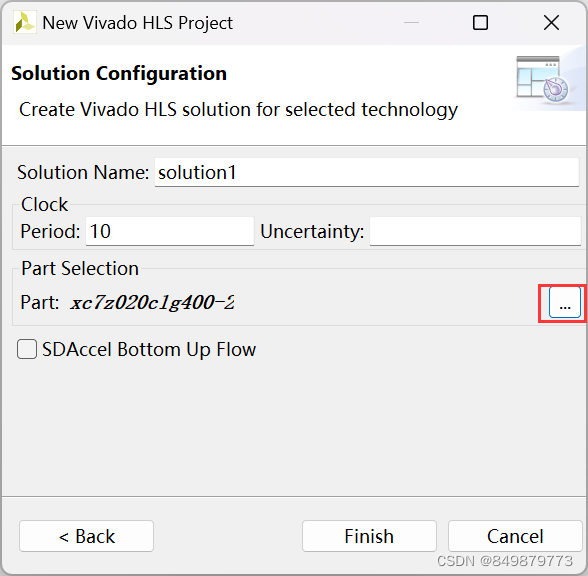

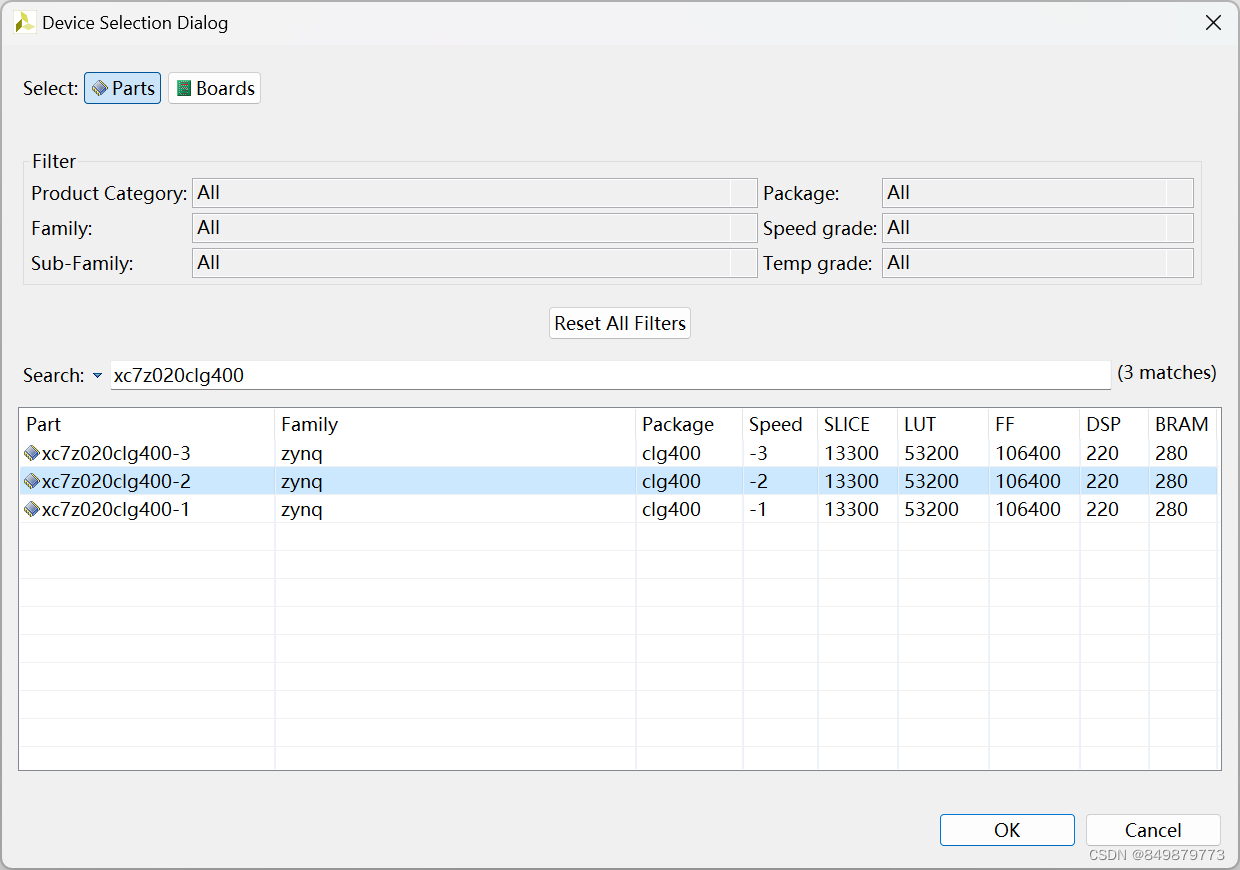

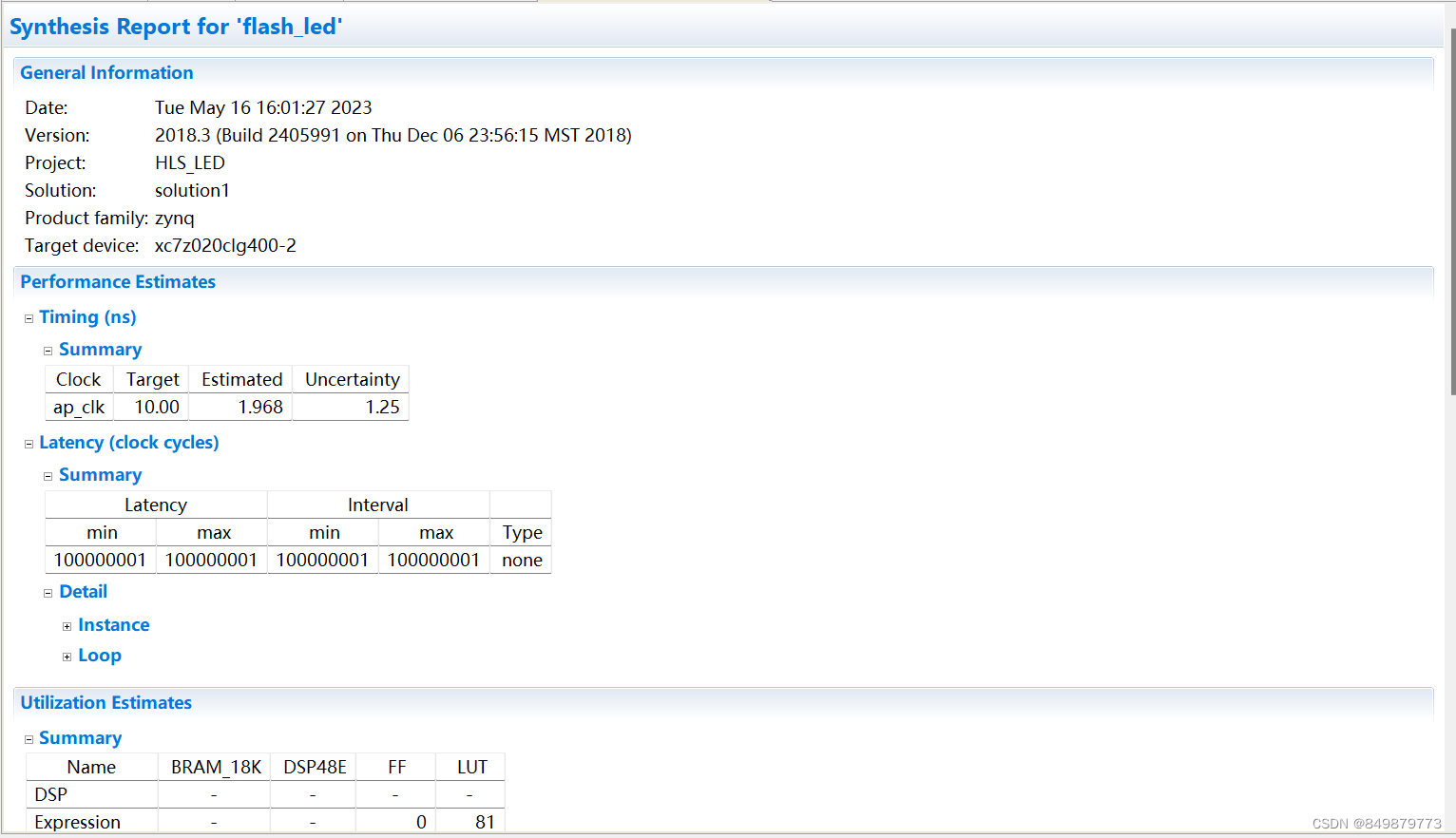

本次实验使用的是Z7-Lite7020,芯片为Xilinx的 xc7z020clg400- 2

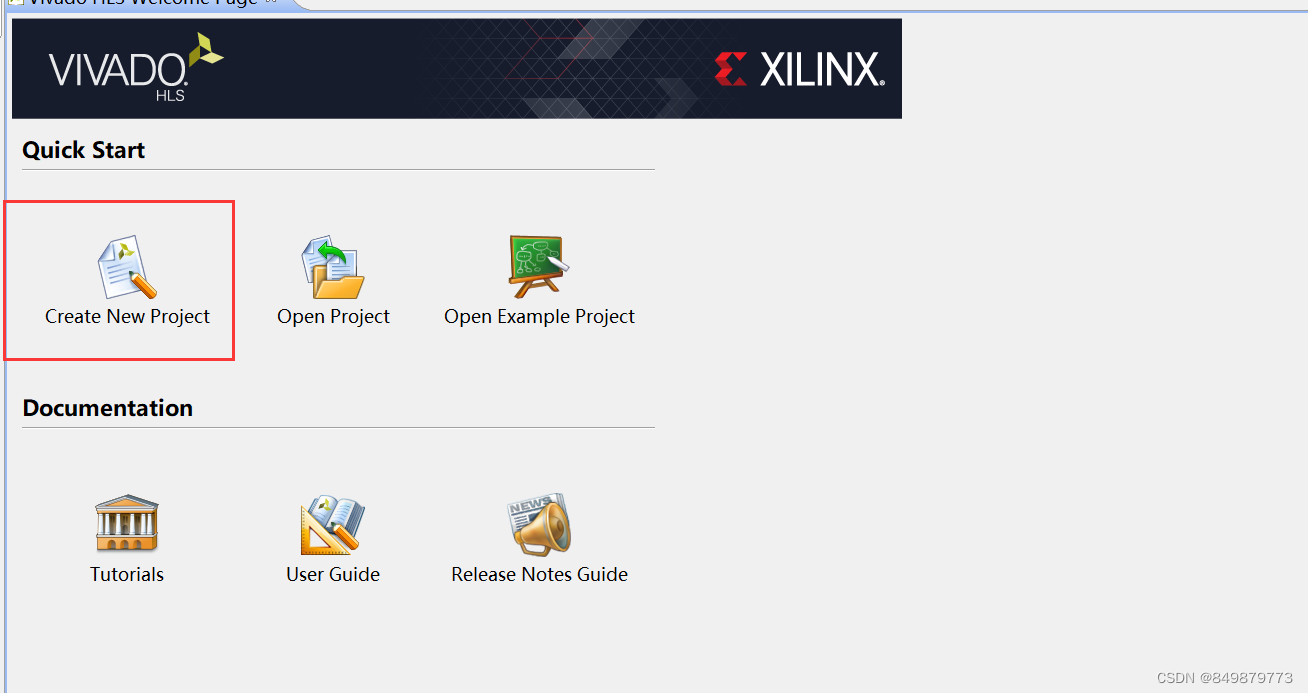

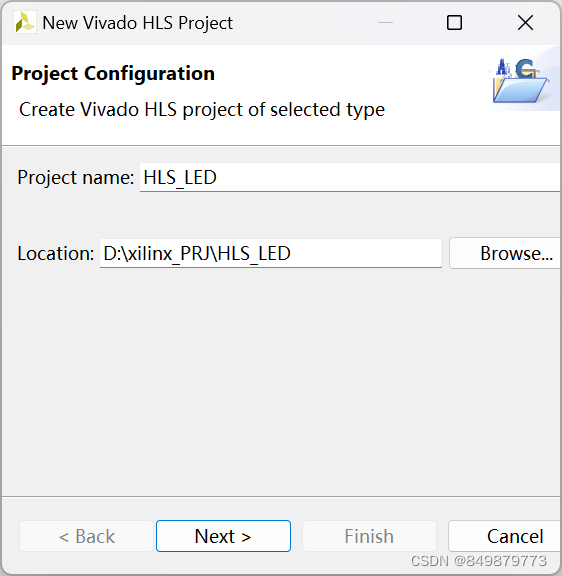

3.1. 新建一个 HLS 工程

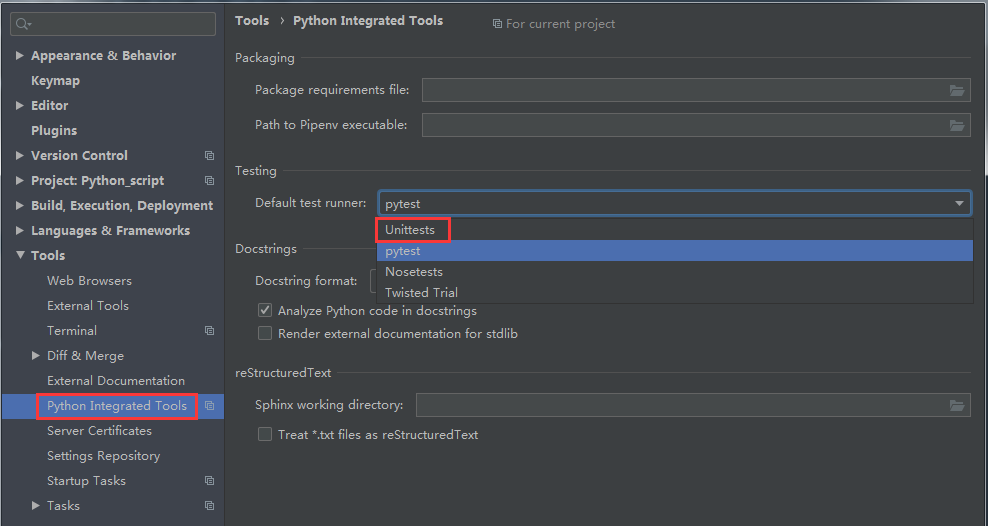

安装好 Vivado 套件后,已经自动安装好了 HLS,我们只需打开 Vivado HLS 即 可

打开 HLS 后如下图所示,点击 Create New Project,创建一个新的工程

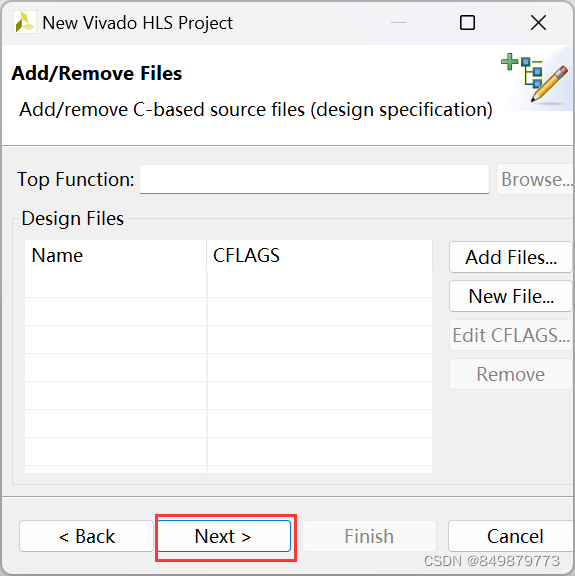

接下来选择定成函数,我们在这里暂不不添加,直接点击 Next

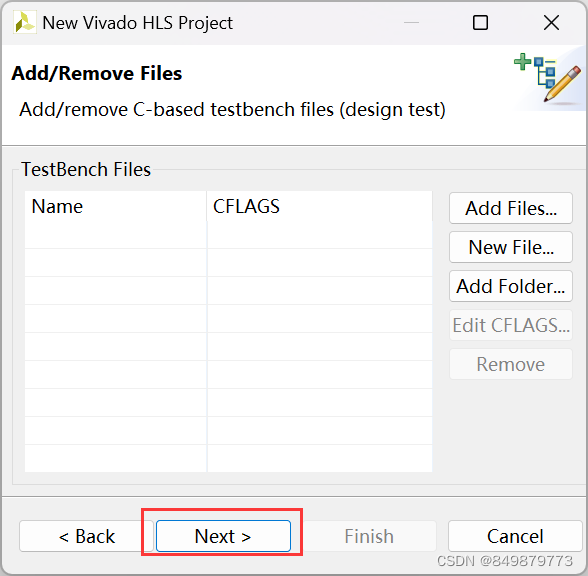

接下来是添加 C 仿真文件,我们同样先不添加,点击 Next

接下来进行器件的选择,在首先我们点击图中所示位置选择元器件

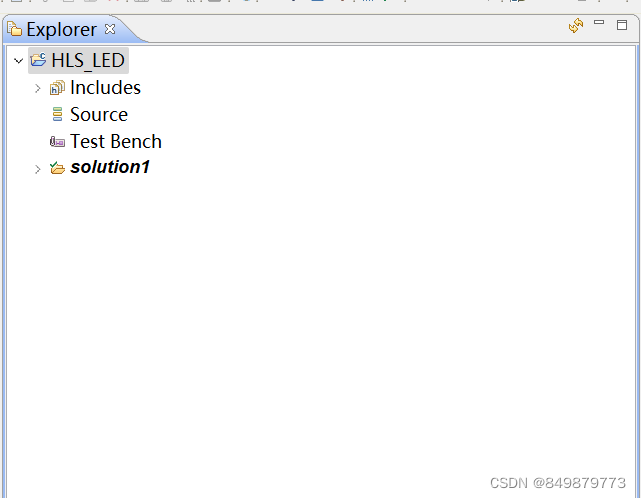

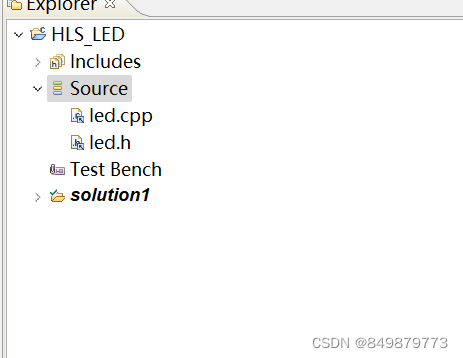

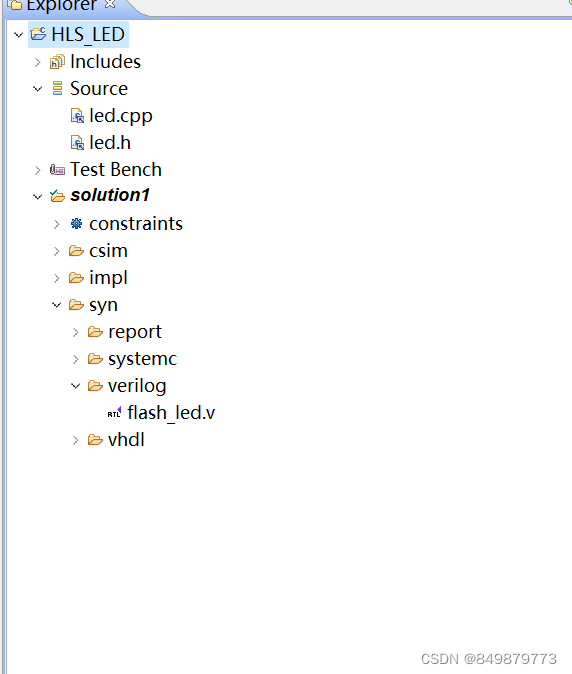

在导航栏中,文件列表所示

其中 source 栏用来存放功能函数的源码,Test Bench 用来存放 C 仿真文件, solution 中包含着本次工程运行中和运行完成后的输出文件

3.2 添加源文件

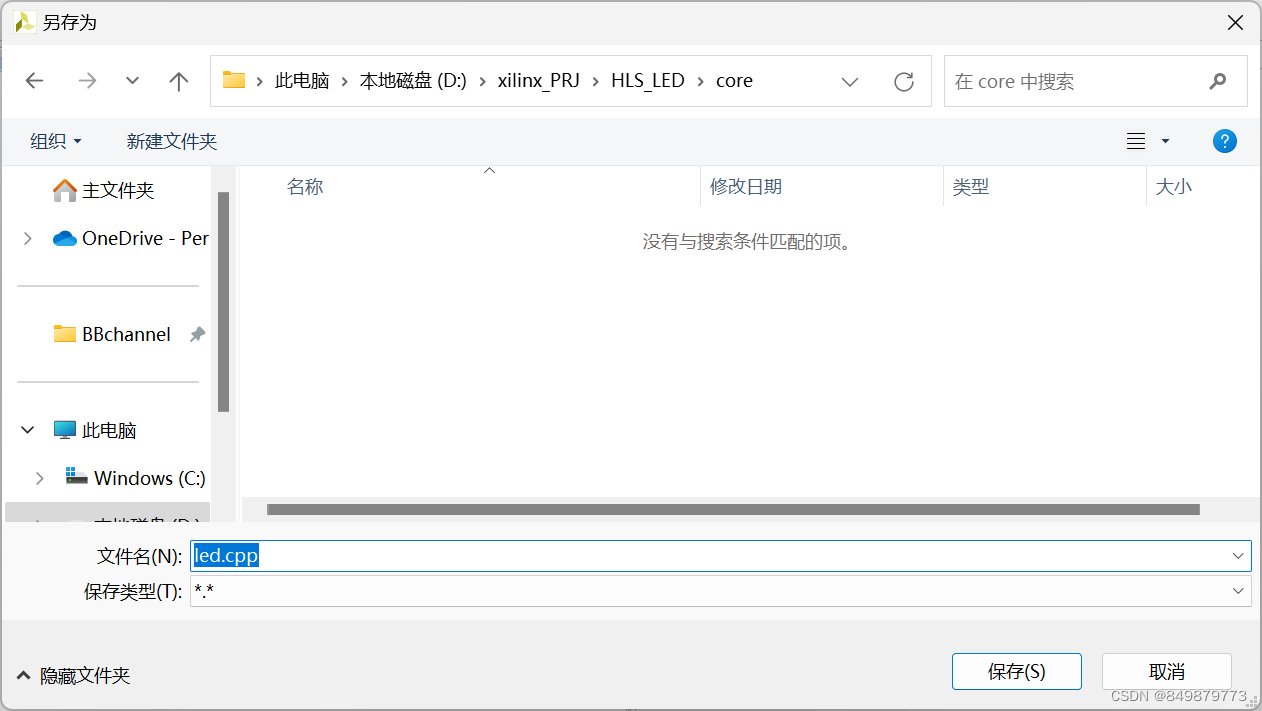

首先,我们添加本次工程的源码,右键 Source,点击 New file,在弹 出的窗口中,选中我们存放源码的目录后。新建一个 led.cpp 文件

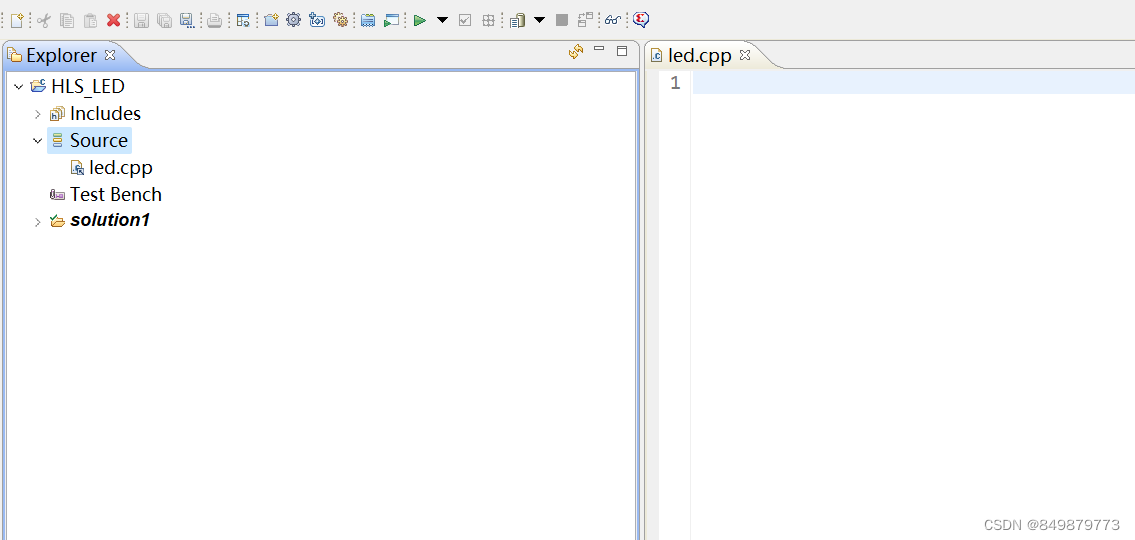

回到保存后 HLS 会自动打开我们刚创建的文件,我们可以在该文件中编写, 我们要实现的函数的代码

按照同样的方法,我们可以为该 cpp 文件添加一个头文件

3.2.1 led.h

#ifndef _SHIFT_LED_H_

#define _SHIFT_LED_H_

#define CNT_MAX 100000000

//#define CNT_MAX 100

#define FLASH_FLAG CNT_MAX-2

typedef int led_t;

typedef int cnt_t;

void flash_led(led_t *led_o , led_t led_i);

#endif

其中计数最大值 CNT_MAX 100000000 是在 100M 时钟频率下计数一秒钟所 需要的计数次数,在仿真的时候,我们可以将其注释掉,采用下一个最大值定义, 这样能够加快我们仿真的速度,FLASH_FLAG 是 LED 闪烁的标志,当计数到该值时,LED 发生变化。 接下来时对 int 类型变量的从定义。最后声明了一个函数,这也是我们本次工程中所需要设计的定成函数

3.2.2 led.cpp

#include "led.h"

void flash_led(led_t *led_o , led_t led_i){

cnt_t i;

for(i=0;i<CNT_MAX;i++){

if(i==FLASH_FLAG){

*led_o = ~led_i;

}

}

}

3.2.3 添加 C 仿真文件

添加仿真文件的步骤与添加源文件类似,右键 Test Bench,选择添加新建文 件,在弹出窗口新建一个 test_led.cpp

test_led.cpp

#include "led.h"

#include "stdio.h"

int main(){

led_t led_i=0x01;

led_t led_o;

const int SHIFT_TIME = 4;

int i;

for(i=0;i<SHIFT_TIME;i++){

flash_led(&led_o , led_i);

led_i = led_o;

printf("shift_out is %d \n",(int)(led_o&0x01));

}

}

在仿真文件中,我们将引入了 led.h 这个头文件,并且调用了 flash_led 这个 函数,在仿真文件中,我们将这个输出从新给到输入,最终来输出 led_o 观察 led_o 的变化。完成 C 仿真文件后,我们可以进行 C 仿真和 C 综合映射到 RTL 电路

3.2.4 进行 C 仿真与 C 综合

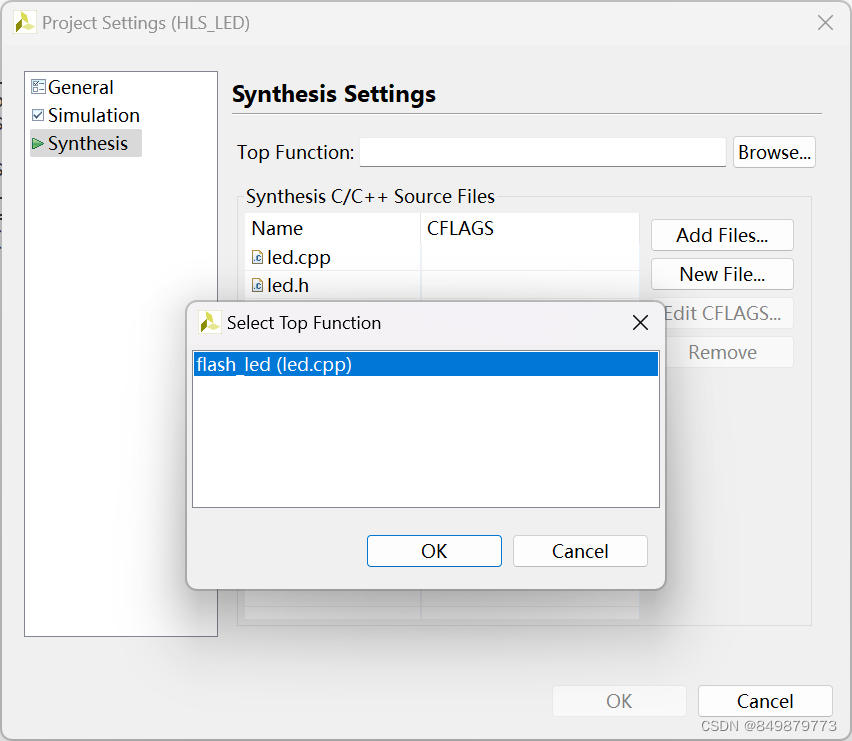

进行仿真之前,我们首先选中我们要仿真的顶层函数,点击 project→选择 project seethings→选择 synthesis→browser→选择 flash_led 作为顶层函数

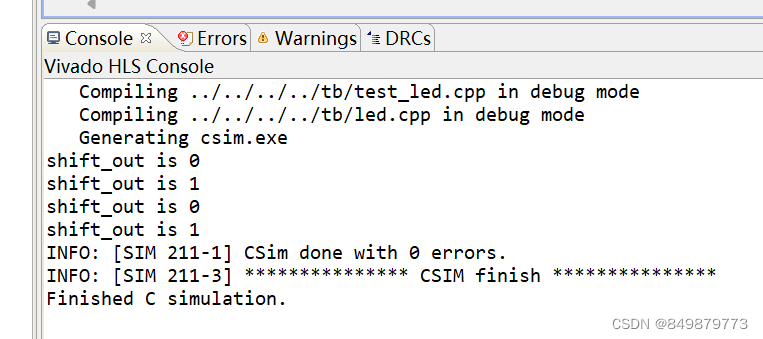

然后点击 project → Run C simulation

在 Console 窗口中,我们可以看到输出的结果时 01 交替变化,证明 C 仿真 的结果正确

如果出现下面的报错将led.h和led.cpp文件删除重新编写

image-20230516155832146

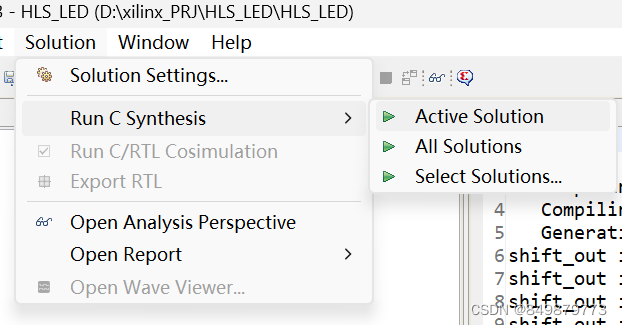

接下来,进行 C 综合,编译器会将 C++代码映射到 RTL 电路,点击 Solution →Run C Synthesis→Active Solution。等待一段时间后,编译器会提示综合后的结果

我们可以查看 C 综合后生成的 RTL 代码,值得说明的是,由 HLS 生成的代 码不具有可读性。在 Solution 的 Syn 中可以找到生成的 Verilog 代码

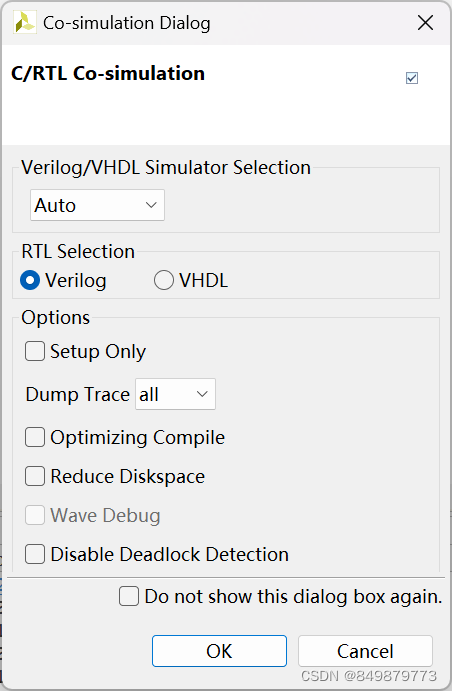

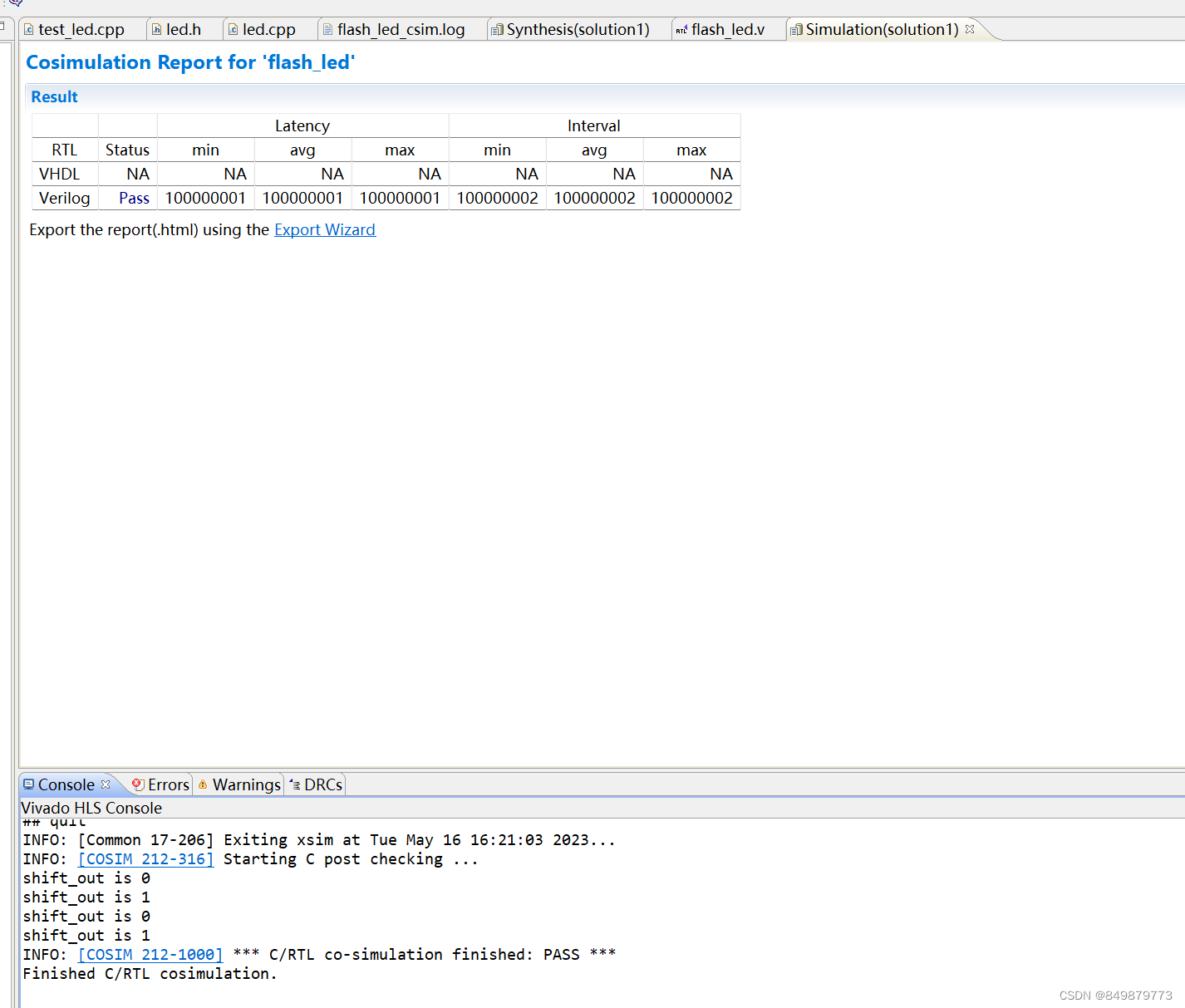

3.2.5 联合仿真

接下来,我们进行 C/RTL 联合仿真,来验证映射出来的 RTL 电路是否正确。Vivado HLS会利用我们的C Testbench 自动生成Verilog的Testbench, 同时,联合仿真结束过后,我们可以通过使用 Vivado 或者 Modelsim 来查看仿真

点击 Solution → Run C/RTL Cosimulation

3.3 导出IP 核

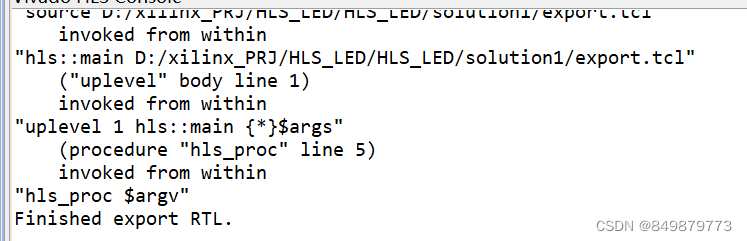

点击 solution 选择 Export RTL 即可以将 HLS 所生成的 RTL 电路导出为 IP 核

3.4 创建 Vivado 工程

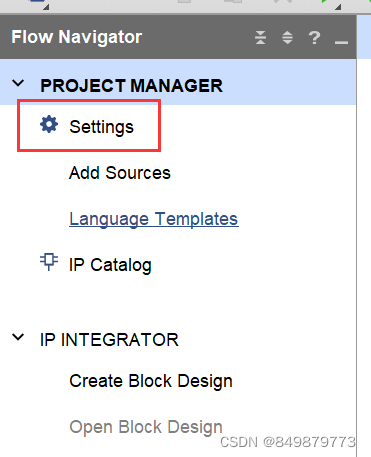

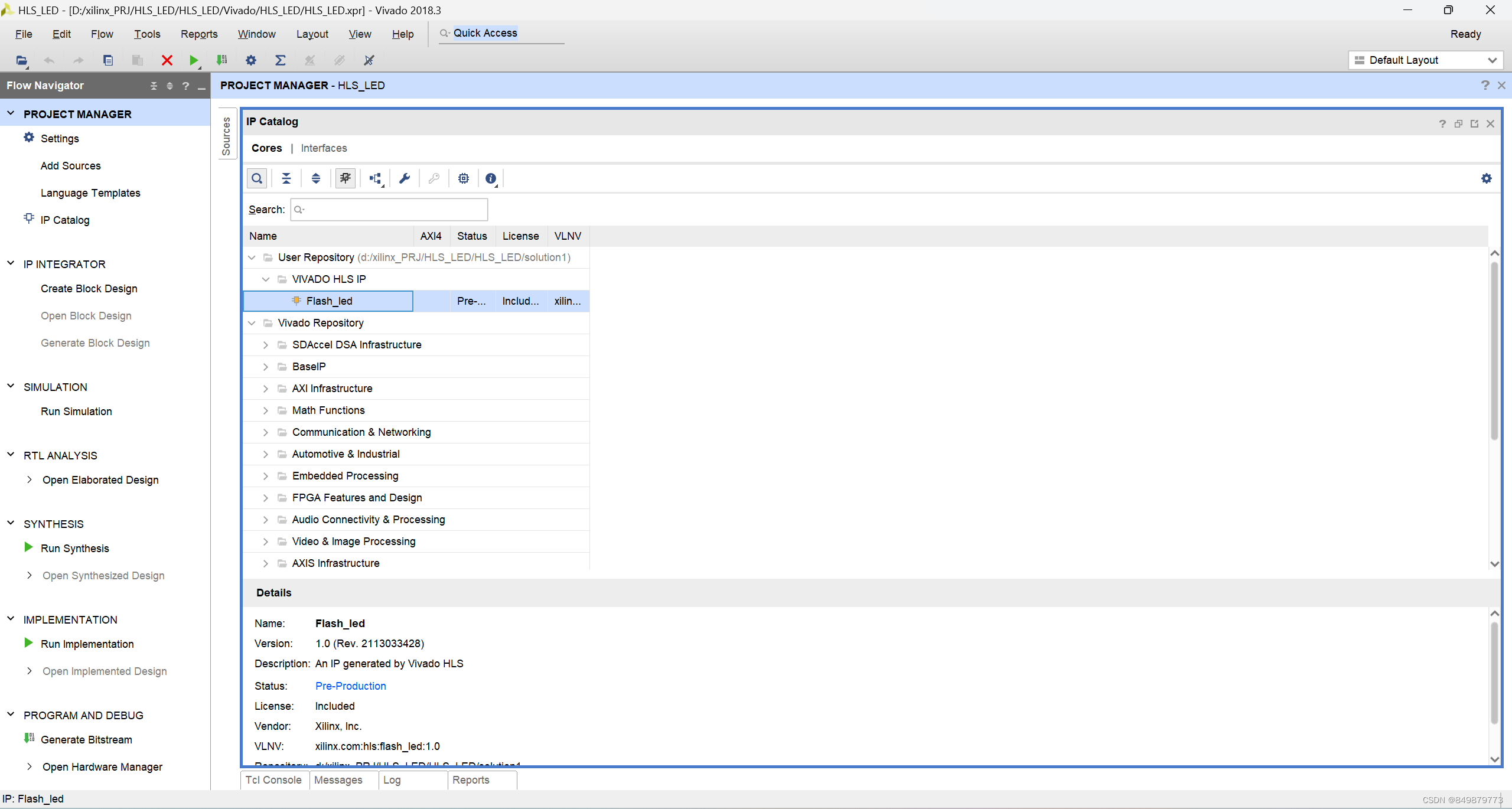

创建完工程后,我们将由 HLS 生成的 IP 添加到我们的 IP 仓库中。点击 settings

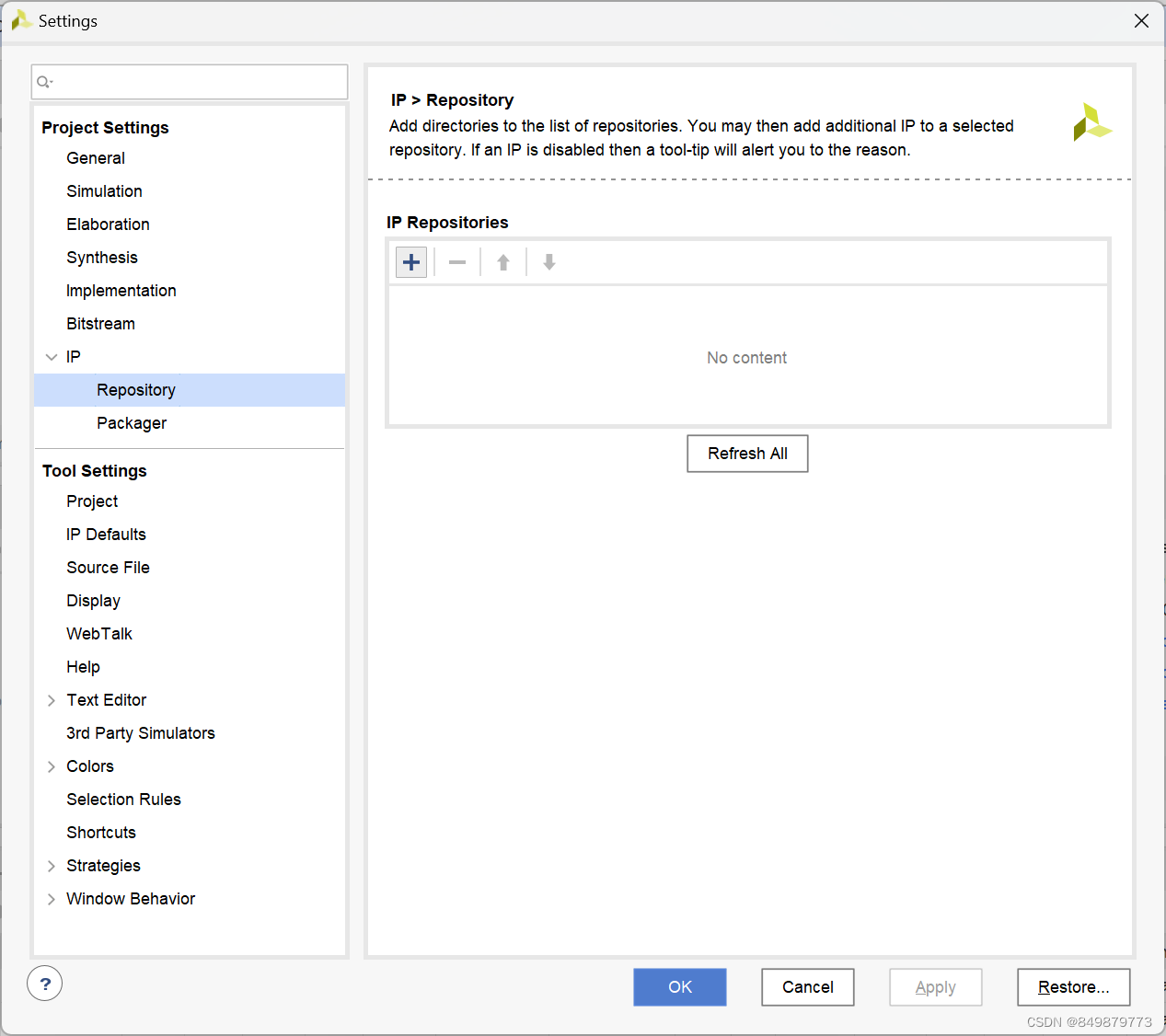

然后点击 IP,选中仓库,再点击+号进行添加由 HLS 生成的 IP

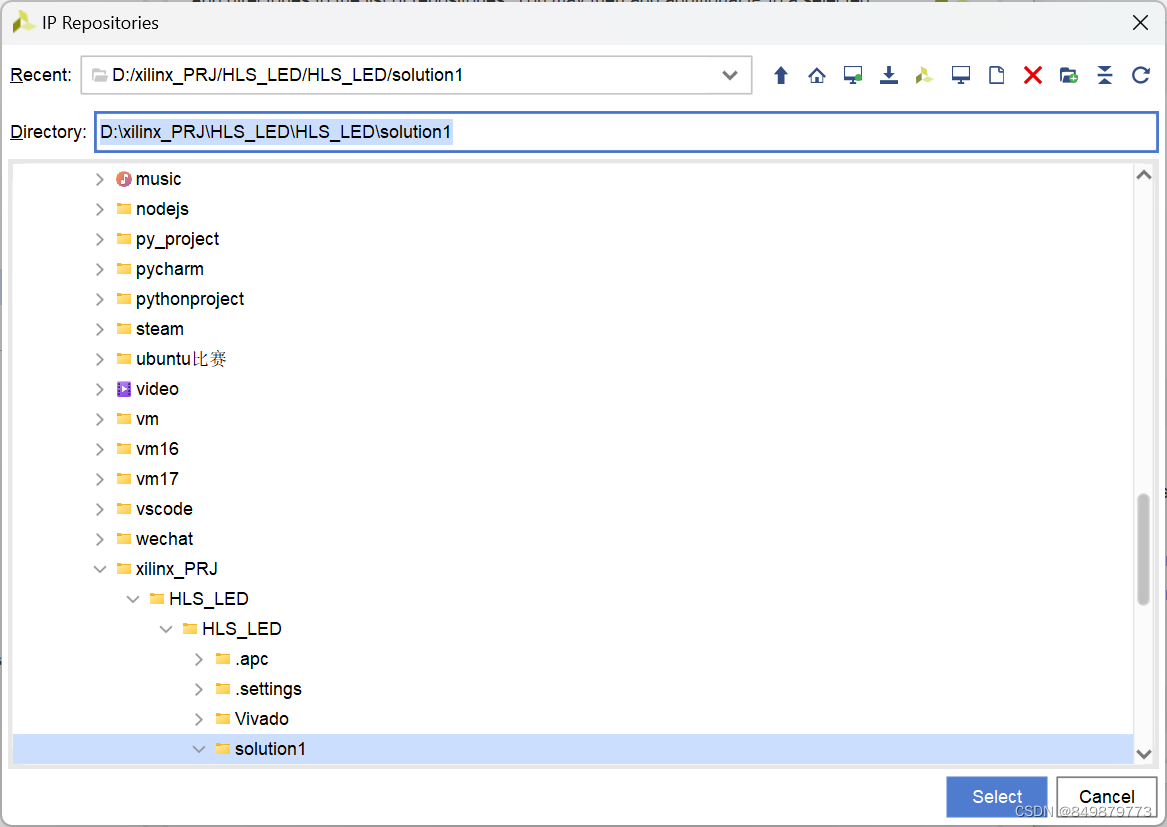

在弹出的界面中,定位到 Solution,点击选择系统将自动识别到 IP

点击 apply → OK,即可将 IP 添加到仓库中。 接下来我们来验证 HLS 生成的 IP 是否被导入到 Vivado IP 仓库。点击 IP Catalog 即可发现 HLS 已经被添加到了 IP 仓库中

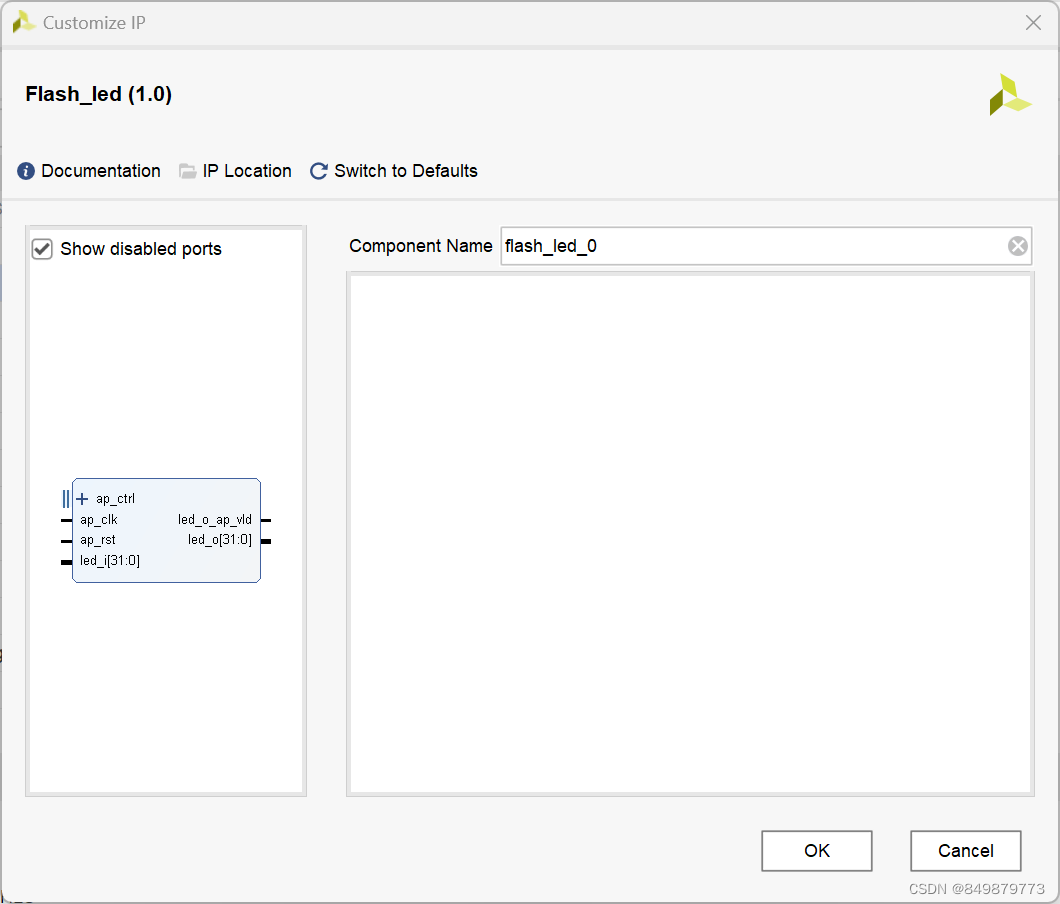

在 IP Catalog 中选中由 HLS 生成的 IP,双击并生成该 IP

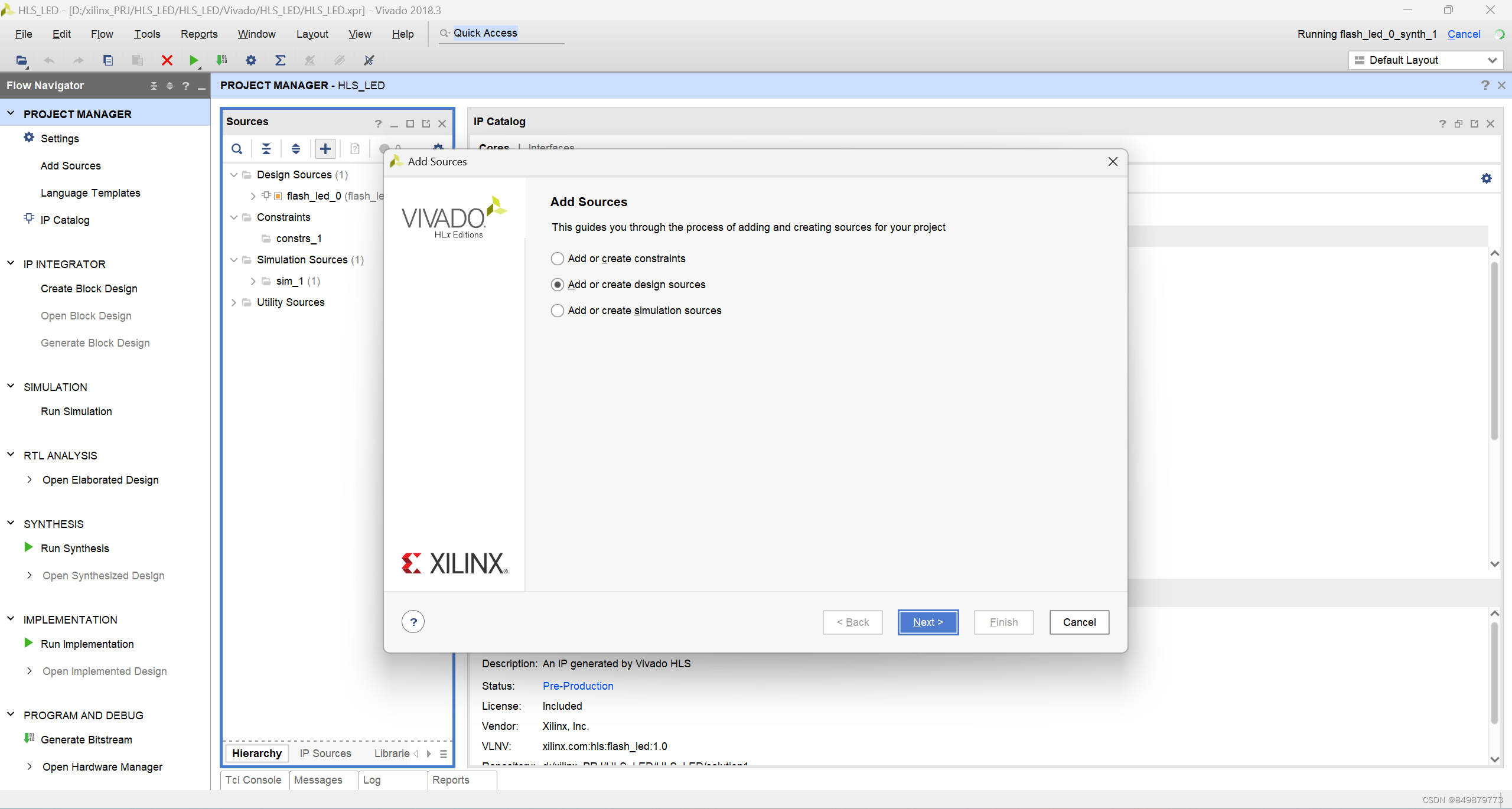

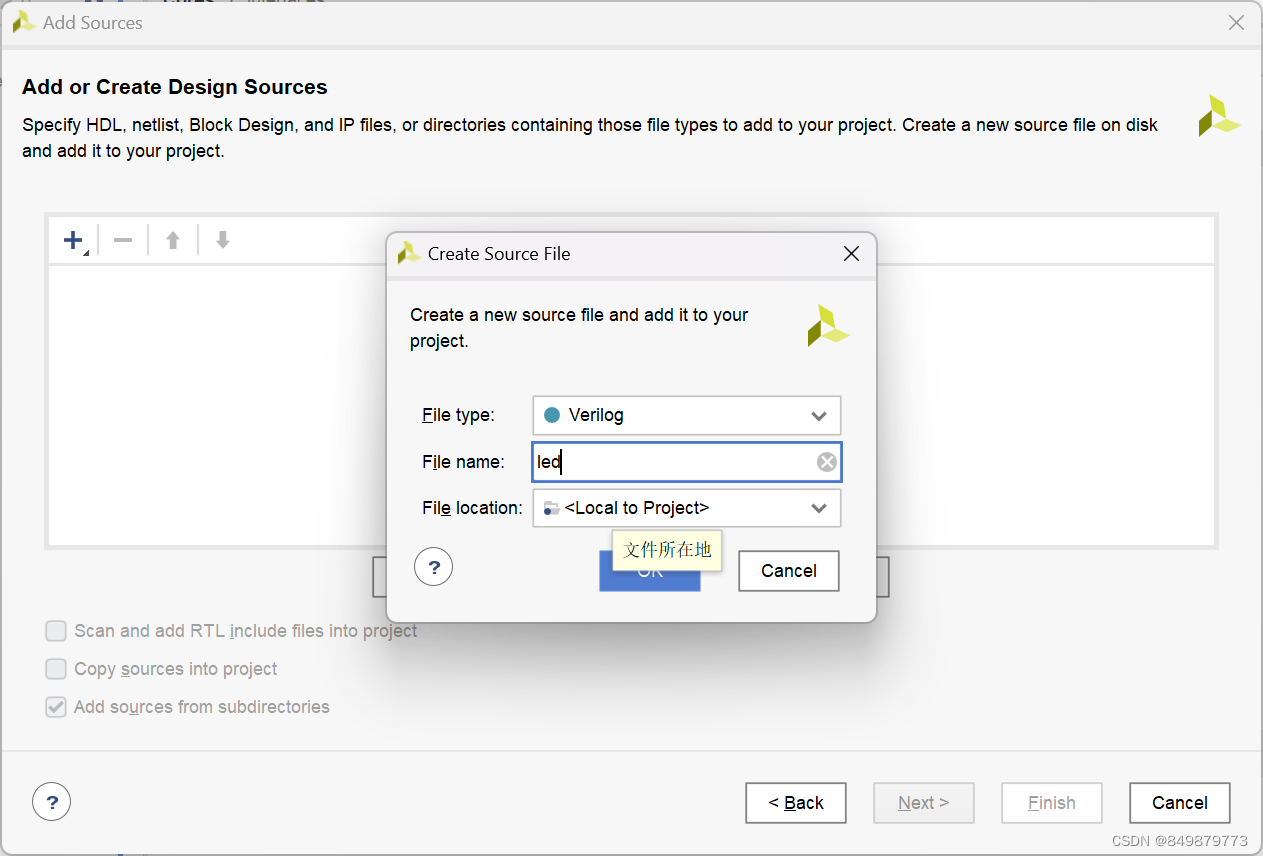

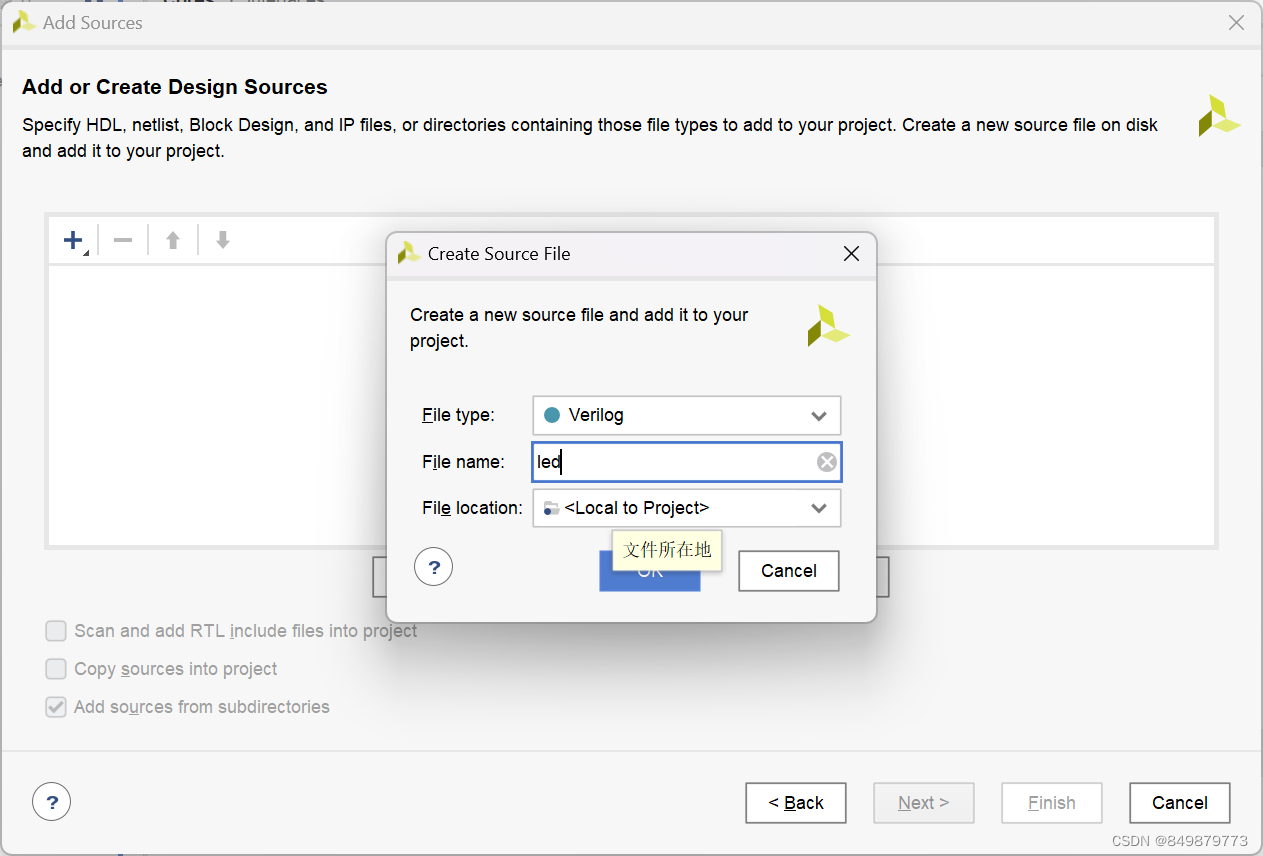

向工程中添加一个新的文件,用于完成本次实验,点击 Add file

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2023/05/16 17:58:35

// Design Name:

// Module Name: led

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module led(

input wire clk ,

input wire rst_n ,

output wire led_o

);

wire rst ;//同步复位

wire ap_ready ;//当前可以接收下一次数据

reg ap_start ;//IP 开始工作

reg led_i_vld ;//输入数据有效

wire led_o_vld ;

reg led_i ;//输入的 led 信号

wire led_o_r ;

wire ap_done ;

wire ap_idle ;

reg [1:0] delay_cnt ;

assign led_o = led_o_r ;

assign rst = ~rst_n ;

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

delay_cnt <= 2'd0;

end

else if(delay_cnt[1] == 1'b0) begin

delay_cnt <= delay_cnt + 1'd1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

ap_start <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

ap_start <= 1'b1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

led_i_vld <= 1'b0;

end

else if(delay_cnt[1]==1'b1)begin

led_i_vld <= 1'b1;

end

end

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

led_i <= 1'b0;

end

else if(led_o_vld==1'b1)begin

led_i <= led_o_r ;

end

end

flash_led_0 inst_flash_led (

.led_o_ap_vld(led_o_vld), // output wire led_o_V_ap_vld

.ap_clk(clk), // input wire ap_clk

.ap_rst(rst), // input wire ap_rst

.ap_start(ap_start), // input wire ap_start

.ap_done(ap_done), // output wire ap_done

.ap_idle(ap_idle), // output wire ap_idle

.ap_ready(ap_ready), // output wire ap_ready

.led_o(led_o_r), // output wire [0 : 0] led_o_V

.led_i(led_i) // input wire [0 : 0] led_i_V

);

endmodule

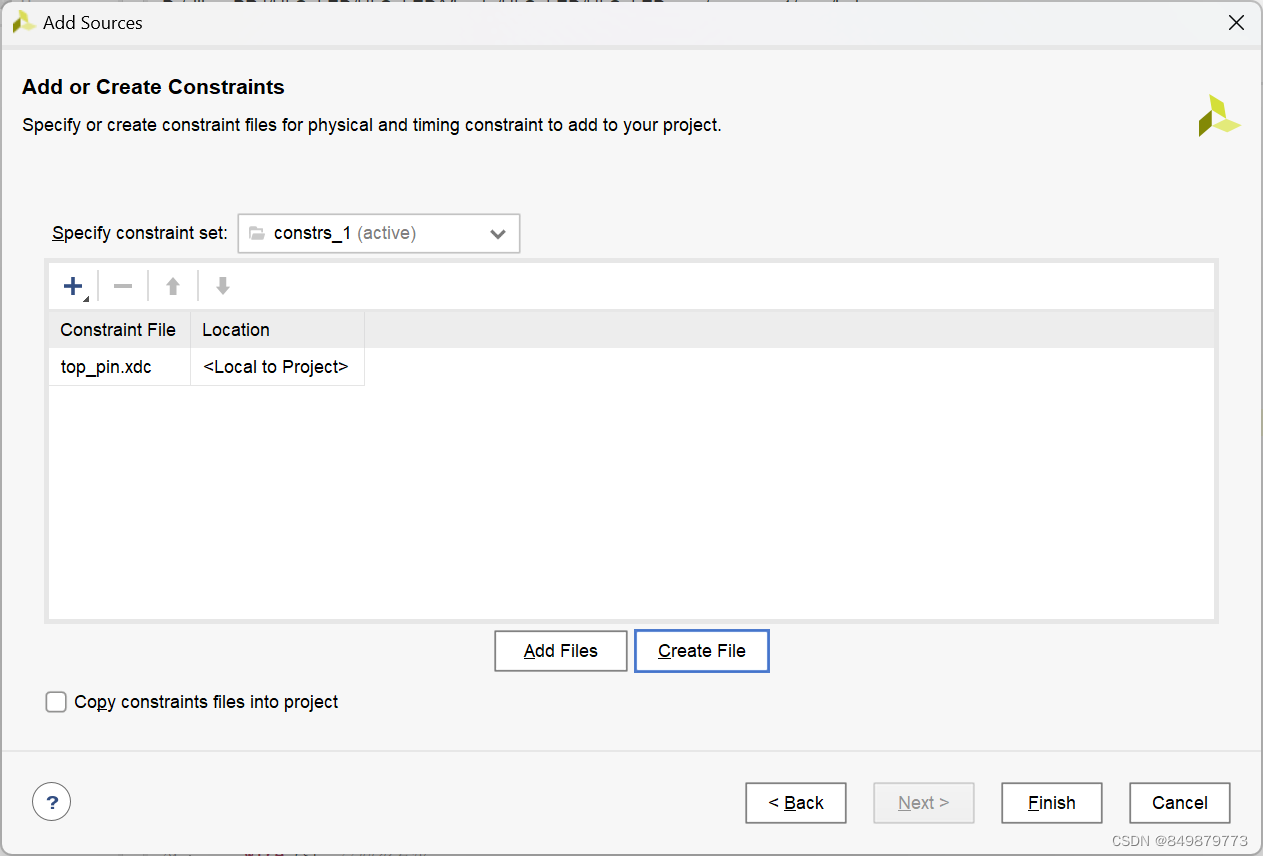

添加管脚约束

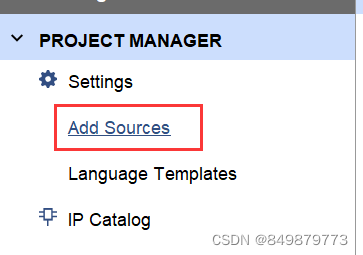

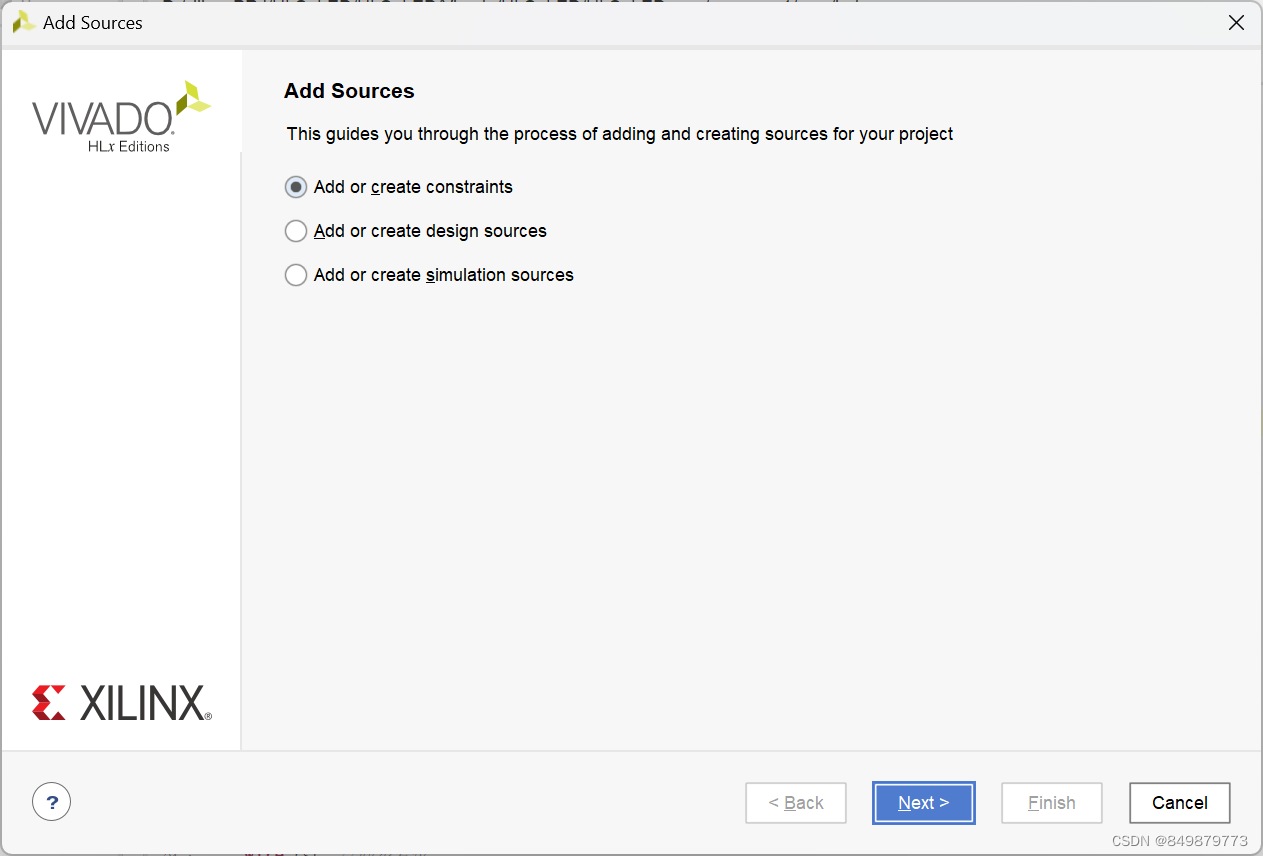

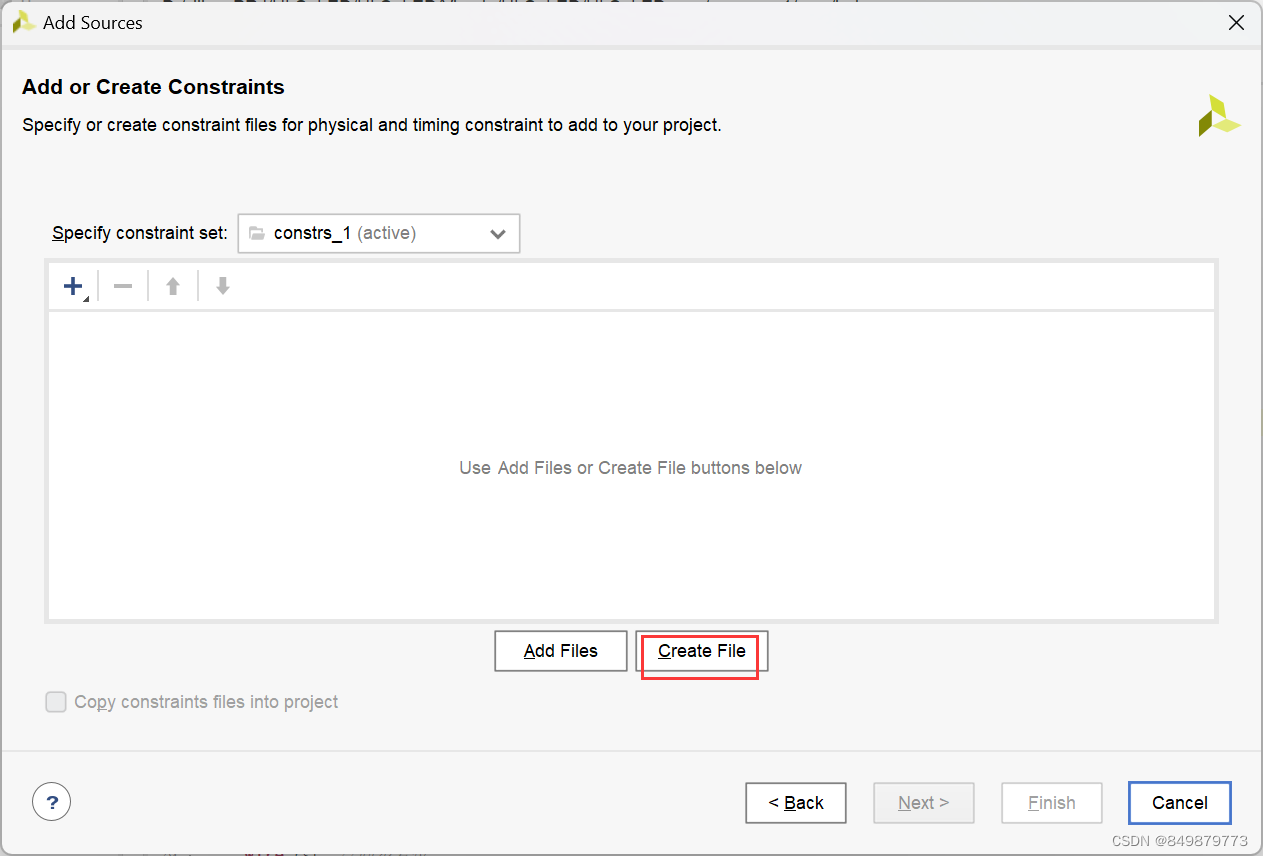

先创建一个.xdc 的约束文件,左侧边栏 Project Manager 下,点击 Add Source 图标

##############LED define##################

set_property PACKAGE_PIN P15 [get_ports {led_o}]

set_property IOSTANDARD LVCMOS33 [get_ports {led_o}]

##############Reset define##################

set_property PACKAGE_PIN P16 [get_ports {rst_n}]

set_property IOSTANDARD LVCMOS33 [get_ports {rst_n}]

##############50M CLK define##################

create_clock -period 20.000 -name clk -waveform {0.000 10.000} [get_ports clk]

set_property PACKAGE_PIN N18 [get_ports {clk}]

set_property IOSTANDARD LVCMOS33 [get_ports {clk}]

4.总结

C语言代码中

子函数对应所需功能的模块,

主函数对应测试平台,用于为子函数输入激励;

步骤:

1、在 C 环境下验证子函数功能,

2、使用 Modelsim 查看生成的 vsim.wlf 文件,时序,

3、编译IP核

4、调用

参考文章

https://blog.csdn.net/QWERTYzxw/article/details/117279573

Z7-Lite 系列教程之HLS篇