链接: 自动构建之CMake

Makefile

Makefile是用于自动化构建软件项目的工具,Makefile的优点是简单、直接,可以直接使用make工具进行构建。但是,Makefile通常需要手动编写和维护,可能会导致跨平台和跨编译器的兼容性问题。

Makefile文件

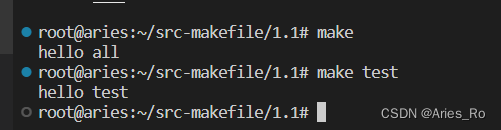

all:

@echo "hello all"

test:

@echo "hello test"

make默认执行第一个任务,也就是all

也可以指定执行,例如make test

Makefile通常包含以下几个部分:

- 变量:用于存储文件名、编译器选项等信息。

- 规则:定义了如何从源文件生成目标文件,包括编译、链接等操作。

- 依赖关系:指定目标文件依赖于哪些源文件,以确保在源文件发生更改时重新构建目标文件。

- 命令:实际执行的编译、链接等操作。

依赖

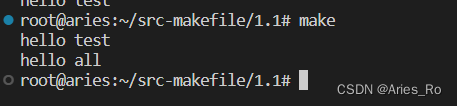

all:test

@echo "hello all"

test:

@echo "hello test"

上述文件中,all就依赖于test,会先执行test,再执行all

多文件形式

Makefile内容

.PHONY: main clean

simple: main.o foo.o

gcc -o simple main.o foo.o

main.o: main.c

gcc -o main.o -c main.c

foo.o: foo.c

gcc -o foo.o -c foo.c

clean:

rm simple main.o foo.o

其中.PHONY是做伪目标作用

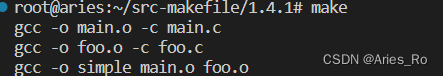

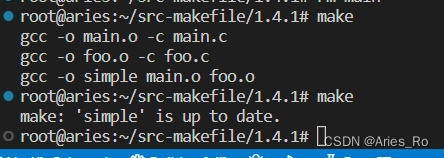

可以看到,simple:依赖于main.o foo.o;其中main.o依赖于main.c文件,foo.o依赖于foo.c文件(这两个依赖可以不用写,但是simple的依赖必须写,因为simple的任务执行前必须要先执行生成main.o和foo.o)

makefile文件执行的时候会检查目标任务结果是否有更新,如果代码没有更新的话,那么make是会不会重复再执行任务。

变量

.PHONY: clean

CC = gcc

RM = rm

EXE = simple

OBJS = main.o foo.o

$(EXE): $(OBJS)

$(CC) -o $(EXE) $(OBJS)

main.o: main.c

$(CC) -o main.o -c main.c

foo.o: foo.c

$(CC) -o foo.o -c foo.c

clean:

$(RM) $(EXE) $(OBJS)

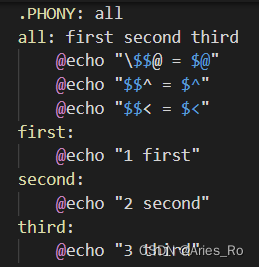

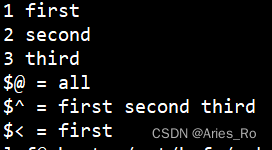

自动变量

$@

$^

$<

可以看到其中

$@所指的是其中命令被运行的目标任务名称

$^则表示的是规则中的所有依赖条件。

$<表示的是规则中的第一个依赖条件。

通配符

采用变量加通配符等,可以实现自适应编译的操作。

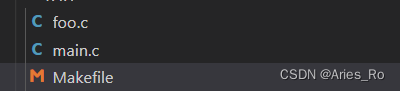

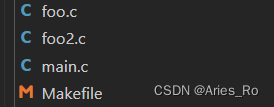

假如文件分布

Makefile内容

.PHONY: clean

CC = gcc

RM = rm

EXE = simple

#SRCS = main.c foo.c

SRCS = $(wildcard *.c) #wildcard 是通配符函数,可以找到所有的.c文件

#SRCS = foo.c foo2.c main.c

OBJS = $(patsubst %.c,%.o,$(SRCS))#patsubst 是字符串替换函数,把.c换成对应的.o

#OBJS = foo.o foo2.o main.o

$(EXE): $(OBJS)

$(CC) -o $@ $^

%.o: %.c #% 也是匹配符

$(CC) -o $@ -c $^

clean:

$(RM) $(EXE) $(OBJS)

src: # 测试make src显示相应的xx.c

@echo $(SRCS)

objs:# 测试make objs显示相应的xx.o

@echo $(OBJS)

其中%是匹配符https://blog.csdn.net/BobYuan888/article/details/88640923

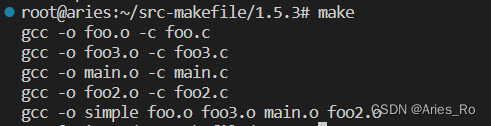

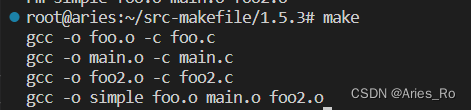

make执行结果:

此时假如我增加一个foo3函数,可以不更新Makefile文件,仍然可以编译成功