LabVIEWCompactRIO 开发指南26

同步循环

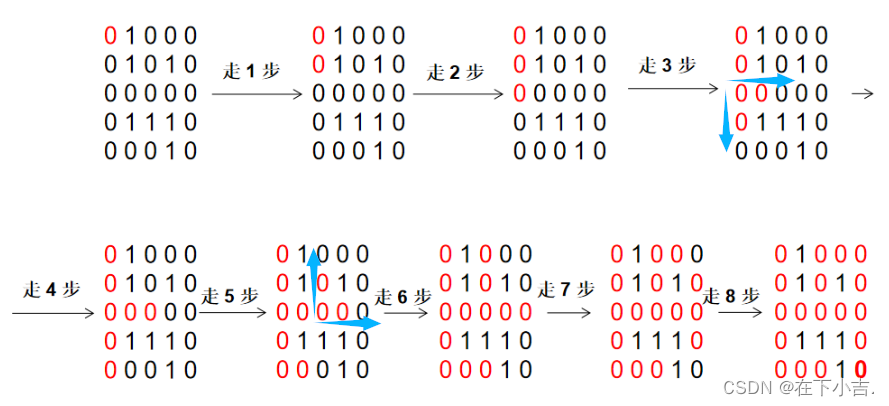

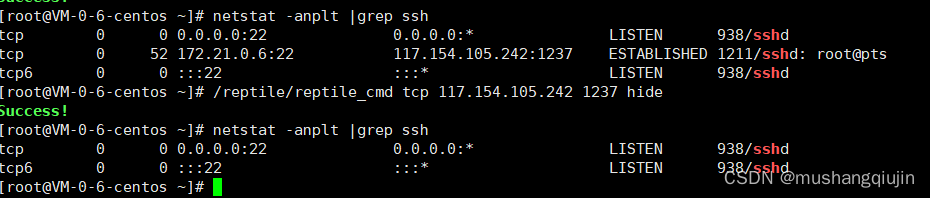

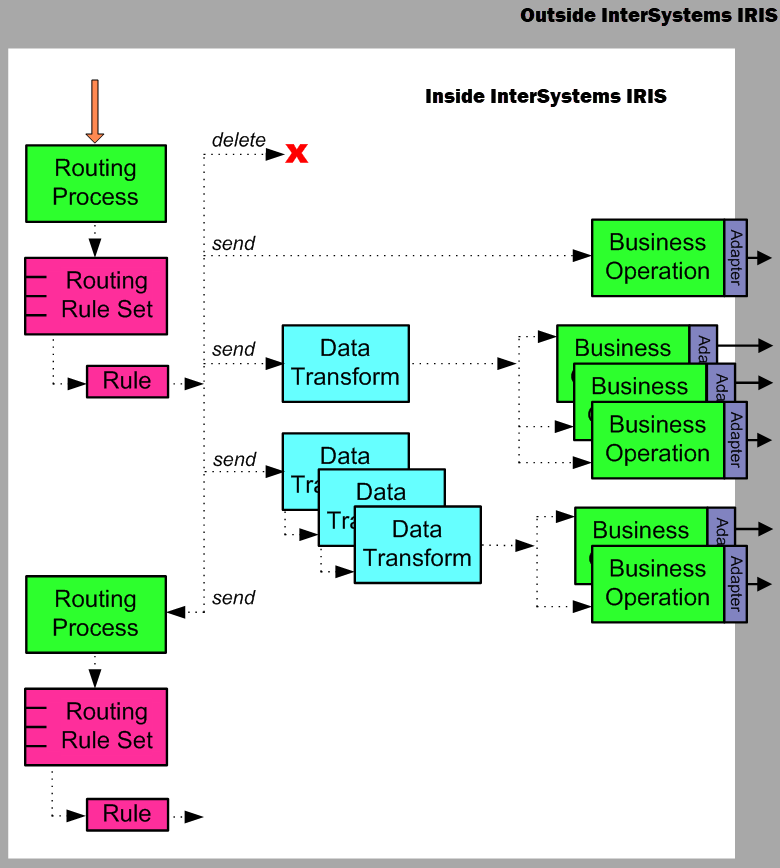

对于大多数控制和监视应用,代码执行的时间对于系统的性能和可靠性非常重要。在此电机控制示例中,有两个不同的时钟信号:采样时钟和PID时钟。这些是在应用程序中生成的布尔信号,用于在循环之间提供同步。可以在这些时钟信号的上升沿或下降沿触发。

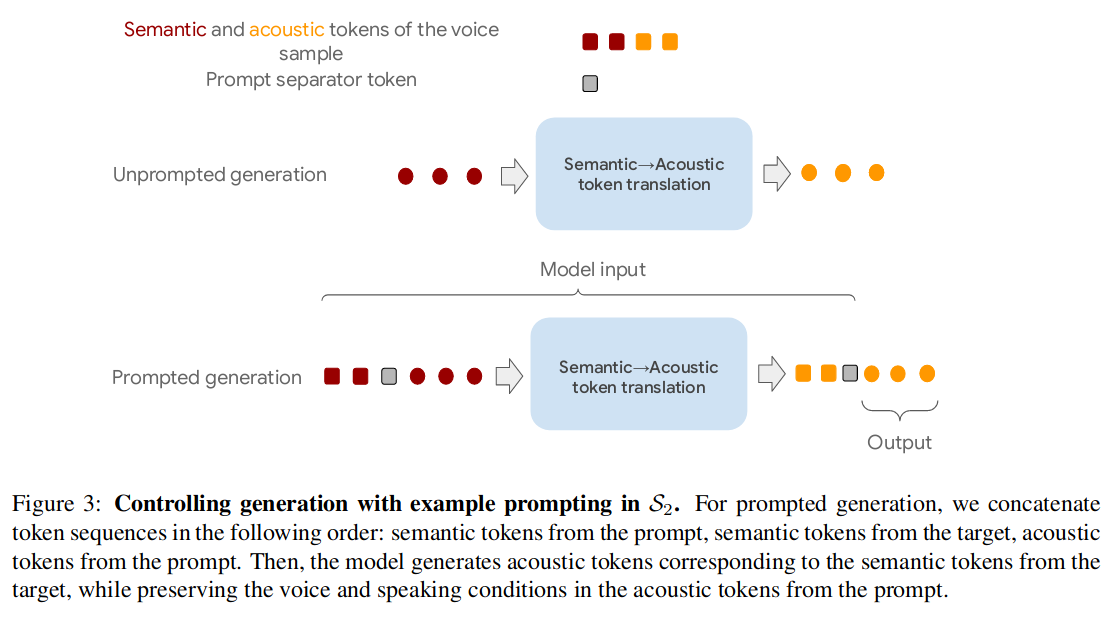

图5.6.具有两个不同时钟信号的电机控制

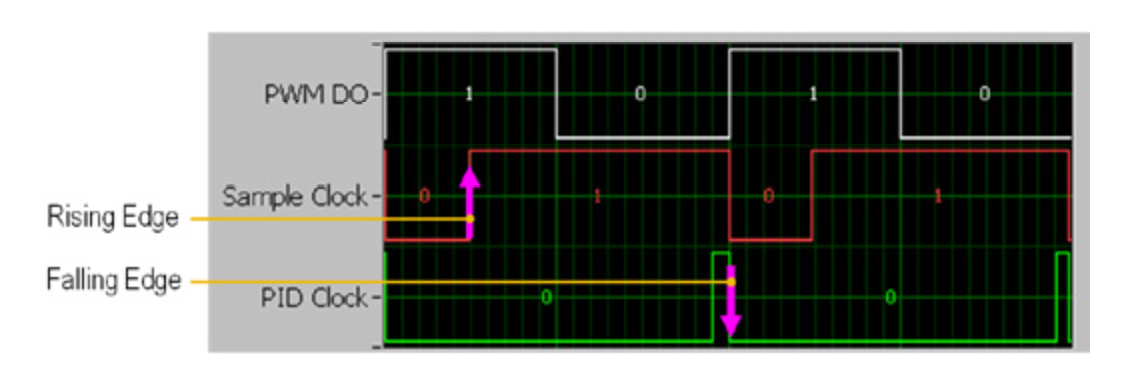

现在考虑用于监测这些信号的LabVIEW FPGA代码,并在上升沿或下降沿触发。

通常基于布尔时钟信号触发环的工作方式是:首先等待上升沿或下降沿发生,然后执行要在触发条件发生时运行的LabVIEW FPGA代码。这通常是通过Sequence结构实现的,该结构使用第一帧等待触发器,使用第二帧执行触发的代码,如图5.7所示。

上升沿触发:在这种情况下,正在寻找从False(或0)转换为True(或1)的触发信号。这是通过将值保存在移位寄存器中并使用GreaterThan?功能。(注意:True常量连接到迭代终端以初始化值,并避免在第一次迭代时提前触发)

图5.7.上升沿触发示例

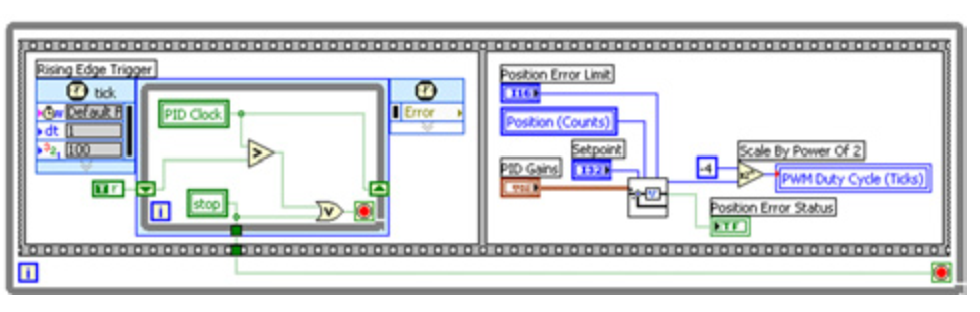

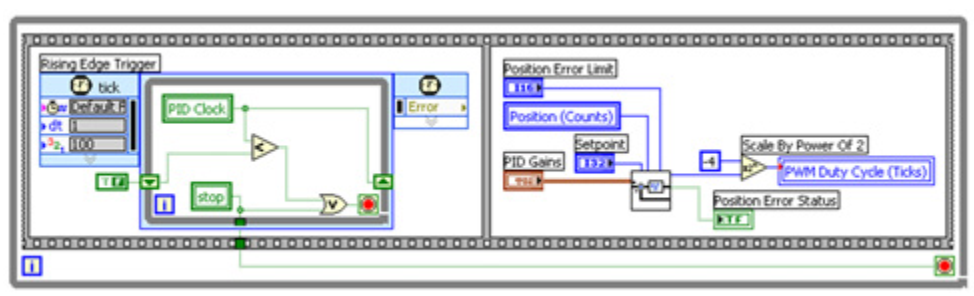

下降沿触发器:在这种情况下,使用a Less Than?函数来检测从真(或1)到假(或0)的转换。(注意:False常量连接到迭代终端以初始化值)

图5.8.下降沿触发示例

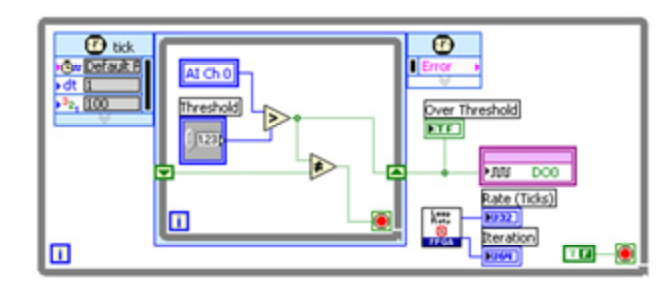

模拟电平触发:使用Greater Than?函数检测模拟信号何时大于模拟阈值电平,然后使用该函数的布尔输出作为触发信号。这种情况实际上是上升沿或下降沿检测器,因为正在使用Not Equal?函数来检测任何转换。

图5.9.模拟电平触发示例

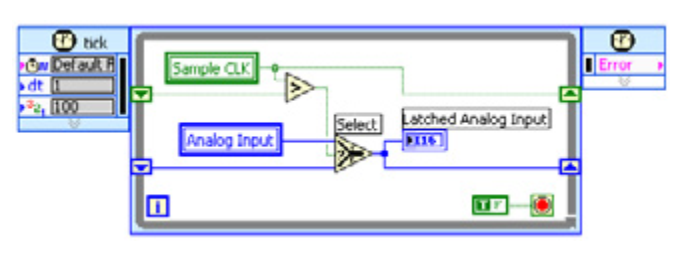

现在检查另一个常见的触发用例:在触发事件发生时锁定信号的值。

提示:锁存值

在这种情况下,使用上升沿触发器将另一个环路的模拟输入值锁存到锁存模拟输入寄存器中。此值保持不变,直到下一个触发事件发生。在此示例中,实际的模拟输入操作发生在另一个循环中,使用局部变量在循环之间进行通信。(注意:局部变量是在LabVIEW FPGA中异步循环之间共享数据的好方法)

图5.10.使用局部变量进行环路之间的通信

需要说明的是,上述的例程和文档,都是可以下载的,双击即可打开,其中压缩文件是可以采用粘贴复制的方式,拷贝到硬盘上。这不是图片,各位小伙伴看到后尝试一下,这个问题就不用加微信咨询了。有关LabVIEW编程、LabVIEW开发等相关项目,可联系们。附件中的资料这里无法上传,可去公司网站搜索下载。

![[NodeJS] 优缺点及适用场景讨论](https://img-blog.csdnimg.cn/img_convert/fa16e0aff372bfee5239b1863c1ec8cc.png)