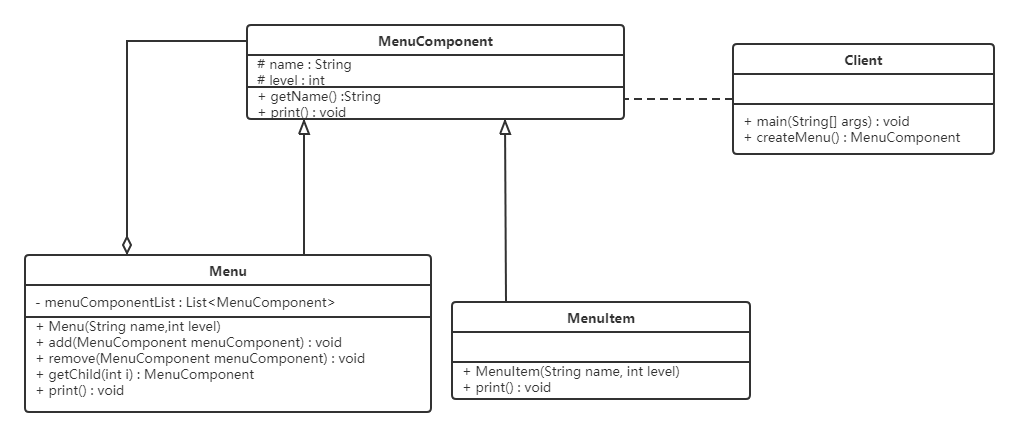

linux pl320 mbox控制器驱动分析-(3)pl320驱动代码分析

- 1 pl320 mbox控制器宏定义

- 2 初始化接口

- 3 ipc_handler mbox中断处理函数

- 4 数据的收发

- 4.1 数据发送

- 4.2 数据接收

- 4.3 中断发送接收测试代码

- 5 设置以及清除远端目的core

- 5.1 设置远端目的core

- 5.2 清除远端目的core

pl320-ipc.c mbox中断控制器的驱动代码路径为:driver/mailbox/pl320-ipc.c

1 pl320 mbox控制器宏定义

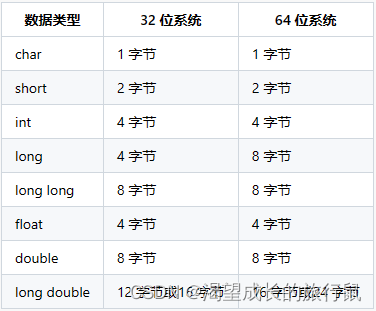

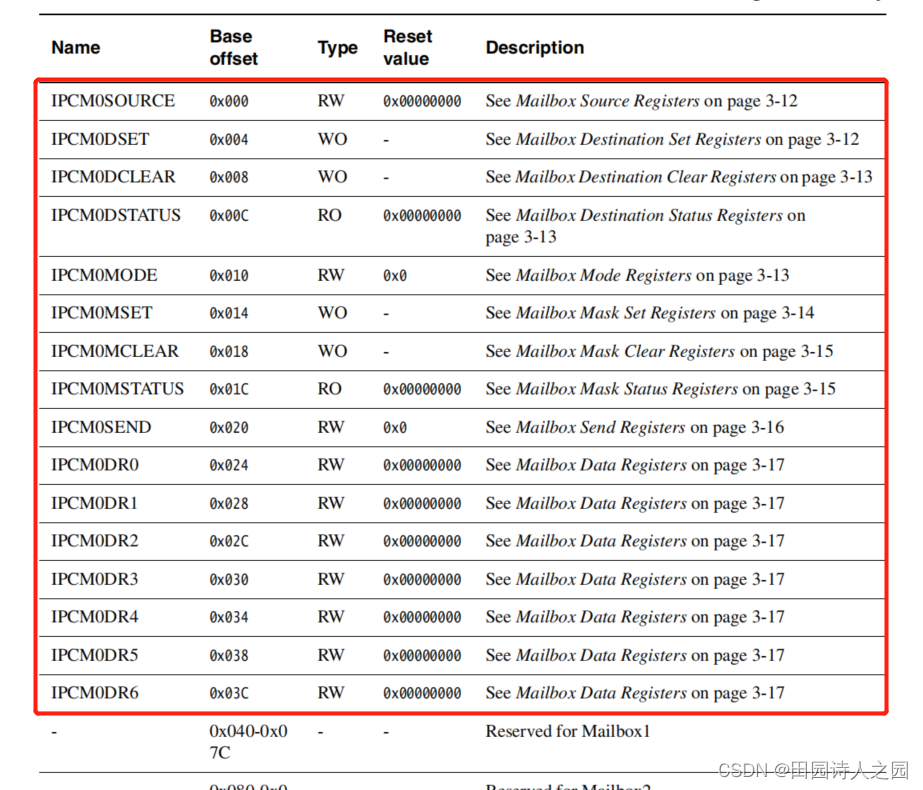

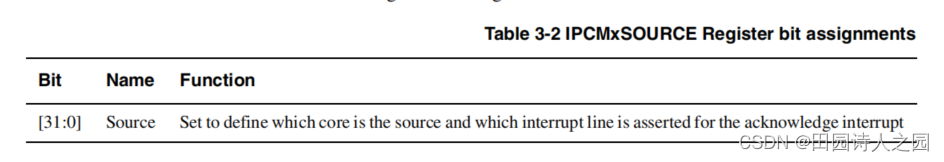

- #define IPCMxSOURCE(m) ((m) * 0x40) 每个mbox有0x40byte的控制寄存器用于做ipcm处理。而每个mbox的第一个寄存器用于设置源 core的。

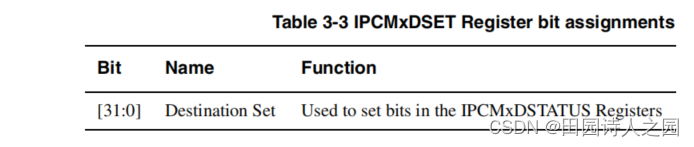

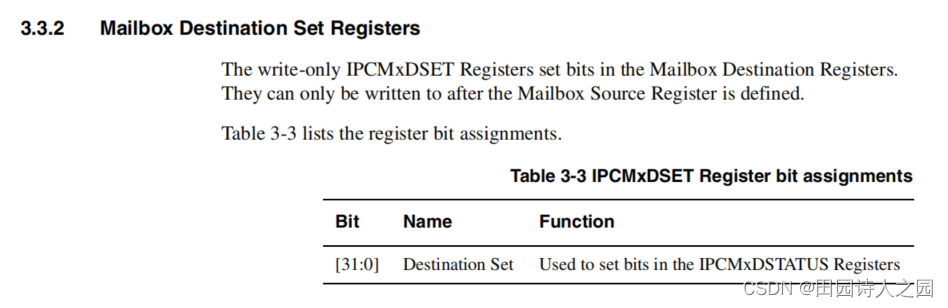

- #define IPCMxDSET(m) (((m) * 0x40) + 0x004)

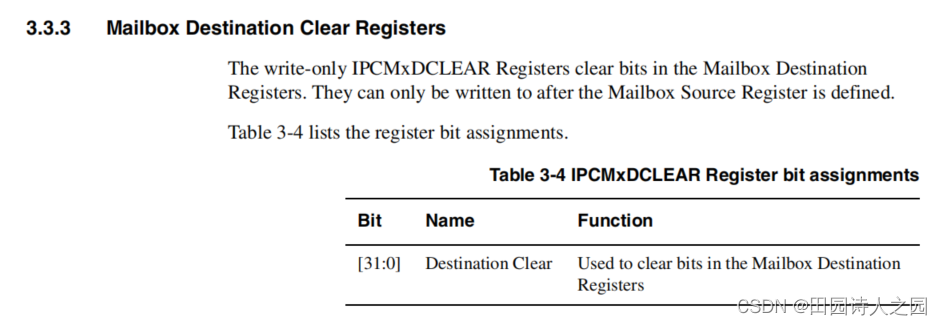

- IPCMxDCLEAR ~ IPCMxDR则依次对应于上面的表格所表示的寄存器。

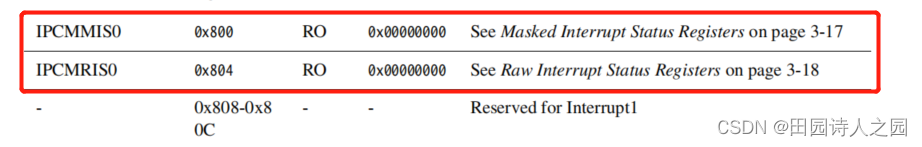

- IPCMMIS和IPCMRIS寄存器用于判断mbox中断源的

- #define MBOX_MASK(n) (1 << (n)) 用于判断当前的中断来自于哪个mbox

#define IPCMxSOURCE(m) ((m) * 0x40)

#define IPCMxDSET(m) (((m) * 0x40) + 0x004)

#define IPCMxDCLEAR(m) (((m) * 0x40) + 0x008)

#define IPCMxDSTATUS(m) (((m) * 0x40) + 0x00C)

#define IPCMxMODE(m) (((m) * 0x40) + 0x010)

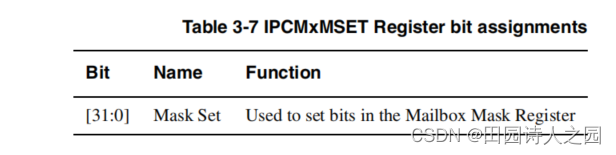

#define IPCMxMSET(m) (((m) * 0x40) + 0x014)

#define IPCMxMCLEAR(m) (((m) * 0x40) + 0x018)

#define IPCMxMSTATUS(m) (((m) * 0x40) + 0x01C)

#define IPCMxSEND(m) (((m) * 0x40) + 0x020)

#define IPCMxDR(m, dr) (((m) * 0x40) + ((dr) * 4) + 0x024)

#define IPCMMIS(irq) (((irq) * 8) + 0x800)

#define IPCMRIS(irq) (((irq) * 8) + 0x804)

#define MBOX_MASK(n) (1 << (n))

#define IPC_TX_MBOX 1

#define IPC_RX_MBOX 2

#define CHAN_MASK(n) (1 << (n))

#define A9_SOURCE 1 /* core 1 表示为A9 core */

#define M3_SOURCE 0 /* core 0 表示为m3 core */

2 初始化接口

-

ipc_base = ioremap(adev->res.start, resource_size(&adev->res));依据在设备树中分配设置的ipcm地址做iomap地址映射,用于对pl320 mbox中断控制器做处理。 -

writel_relaxed(0, ipc_base + IPCMxSEND(IPC_TX_MBOX));将当前IPC_TX_MBOX channel的mbox修改为0,表示当前不做数据发送处理。 -

ret = request_irq(ipc_irq, ipc_handler, 0, dev_name(&adev->dev), NULL);注册pl320 mbox的中断处理函数 -

writel_relaxed(CHAN_MASK(A9_SOURCE), ipc_base + IPCMxSOURCE(IPC_TX_MBOX));设置IPC_TX_MBOX channel的mbox的源core 为 A9_SOURCE

-

writel_relaxed(CHAN_MASK(M3_SOURCE), ipc_base + IPCMxDSET(IPC_TX_MBOX));设置IPC_TX_MBOX channel的mbox的目的core 为 M3_SOURCE

-

writel_relaxed(CHAN_MASK(M3_SOURCE) | CHAN_MASK(A9_SOURCE), ipc_base + IPCMxMSET(IPC_TX_MBOX));设置IPC_TX_MBOX的收发core的中断使能

static int pl320_probe(struct amba_device *adev, const struct amba_id *id)

{

int ret;

ipc_base = ioremap(adev->res.start, resource_size(&adev->res));

if (ipc_base == NULL)

return -ENOMEM;

writel_relaxed(0, ipc_base + IPCMxSEND(IPC_TX_MBOX));

ipc_irq = adev->irq[0];

ret = request_irq(ipc_irq, ipc_handler, 0, dev_name(&adev->dev), NULL);

if (ret < 0)

goto err;

/* Init slow mailbox */

writel_relaxed(CHAN_MASK(A9_SOURCE),

ipc_base + IPCMxSOURCE(IPC_TX_MBOX));

writel_relaxed(CHAN_MASK(M3_SOURCE),

ipc_base + IPCMxDSET(IPC_TX_MBOX));

writel_relaxed(CHAN_MASK(M3_SOURCE) | CHAN_MASK(A9_SOURCE),

ipc_base + IPCMxMSET(IPC_TX_MBOX));

/* Init receive mailbox */

writel_relaxed(CHAN_MASK(M3_SOURCE),

ipc_base + IPCMxSOURCE(IPC_RX_MBOX));

writel_relaxed(CHAN_MASK(A9_SOURCE),

ipc_base + IPCMxDSET(IPC_RX_MBOX));

writel_relaxed(CHAN_MASK(M3_SOURCE) | CHAN_MASK(A9_SOURCE),

ipc_base + IPCMxMSET(IPC_RX_MBOX));

return 0;

err:

iounmap(ipc_base);

return ret;

}

3 ipc_handler mbox中断处理函数

irq_stat = readl_relaxed(ipc_base + IPCMMIS(1));读取core 1的中断状态寄存器,以判断中断的来源

Masked Interrupt Status Registers:

The read-only IPCMMISx Registers contain the current mailbox status for every interrupt identified by the address encoding. This enables each core to read a single register to determine which mailbox caused the interrupt. For example, if Core0 is mapped to Channel ID0, it reads IPCMMIS0 to determine which mailboxes require attention.

irq_stat & MBOX_MASK(IPC_TX_MBOX)判断当前的中断是否来自于IPC_TX_MBOX mboxwritel_relaxed(0, ipc_base + IPCMxSEND(IPC_TX_MBOX));清除中断irq_stat & MBOX_MASK(IPC_RX_MBOX)判断当前的中断是否来自于IPC_RX_MBOX mbox__ipc_rcv(IPC_RX_MBOX, data);接收数据writel_relaxed(2, ipc_base + IPCMxSEND(IPC_RX_MBOX));向源core发送ack中断,通知源core已经处理完成当前的mbox中断。

static irqreturn_t ipc_handler(int irq, void *dev)

{

u32 irq_stat;

u32 data[7];

irq_stat = readl_relaxed(ipc_base + IPCMMIS(1));

if (irq_stat & MBOX_MASK(IPC_TX_MBOX)) {

writel_relaxed(0, ipc_base + IPCMxSEND(IPC_TX_MBOX));

complete(&ipc_completion);

}

if (irq_stat & MBOX_MASK(IPC_RX_MBOX)) {

__ipc_rcv(IPC_RX_MBOX, data);

atomic_notifier_call_chain(&ipc_notifier, data[0], data + 1);

writel_relaxed(2, ipc_base + IPCMxSEND(IPC_RX_MBOX));

}

return IRQ_HANDLED;

}

4 数据的收发

4.1 数据发送

writel_relaxed(data[i], ipc_base + IPCMxDR(mbox, i));将数据写入到对应mbox channel的数据寄存器中。writel_relaxed(0x1, ipc_base + IPCMxSEND(mbox));向远端目的core发送中断。

The Mailbox Send Register bits can only be written to after the Mailbox Source Register is defined:

• setting bit 0 generates an interrupt to the destination core(s)

• setting bit 1 generates an interrupt to the source core.

static void __ipc_send(int mbox, u32 *data)

{

int i;

for (i = 0; i < 7; i++)

writel_relaxed(data[i], ipc_base + IPCMxDR(mbox, i));

writel_relaxed(0x1, ipc_base + IPCMxSEND(mbox));

}

4.2 数据接收

数据接收函数是依次从当前mbox的7个数据寄存器中取出数据。

static u32 __ipc_rcv(int mbox, u32 *data)

{

int i;

for (i = 0; i < 7; i++)

data[i] = readl_relaxed(ipc_base + IPCMxDR(mbox, i));

return data[1];

}

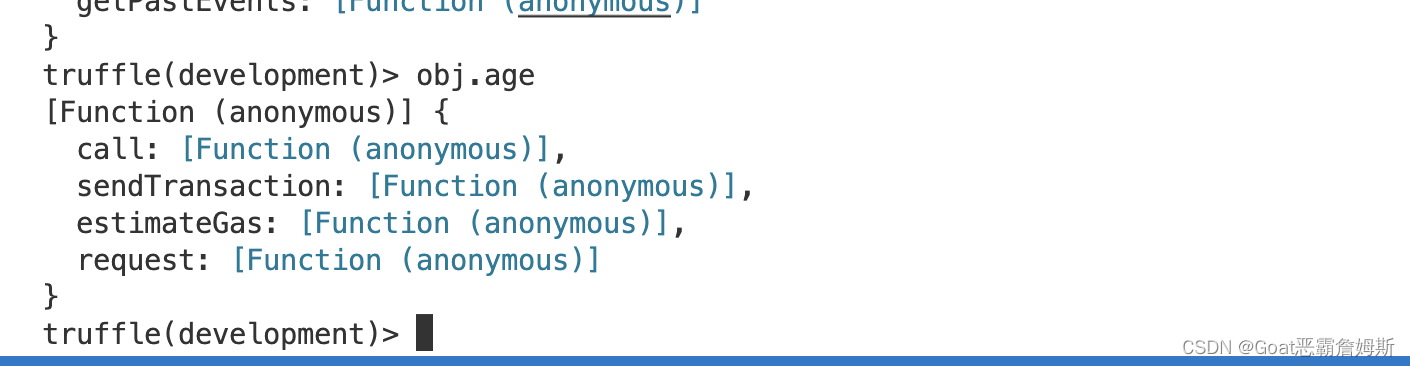

4.3 中断发送接收测试代码

__ipc_send(IPC_TX_MBOX, data);设置数据寄存器要发送的数据,同时触发发送向远端目的core的中断。- wait_for_completion_timeout(&ipc_completion, msecs_to_jiffies(1000));等待中断处理函数完成数据的处理,然后继续执行后面的处理操作。

- ret = __ipc_rcv(IPC_TX_MBOX, data);接收数据

int pl320_ipc_transmit(u32 *data)

{

int ret;

mutex_lock(&ipc_m1_lock);

init_completion(&ipc_completion);

__ipc_send(IPC_TX_MBOX, data);

ret = wait_for_completion_timeout(&ipc_completion,

msecs_to_jiffies(1000));

if (ret == 0) {

ret = -ETIMEDOUT;

goto out;

}

ret = __ipc_rcv(IPC_TX_MBOX, data);

out:

mutex_unlock(&ipc_m1_lock);

return ret;

}

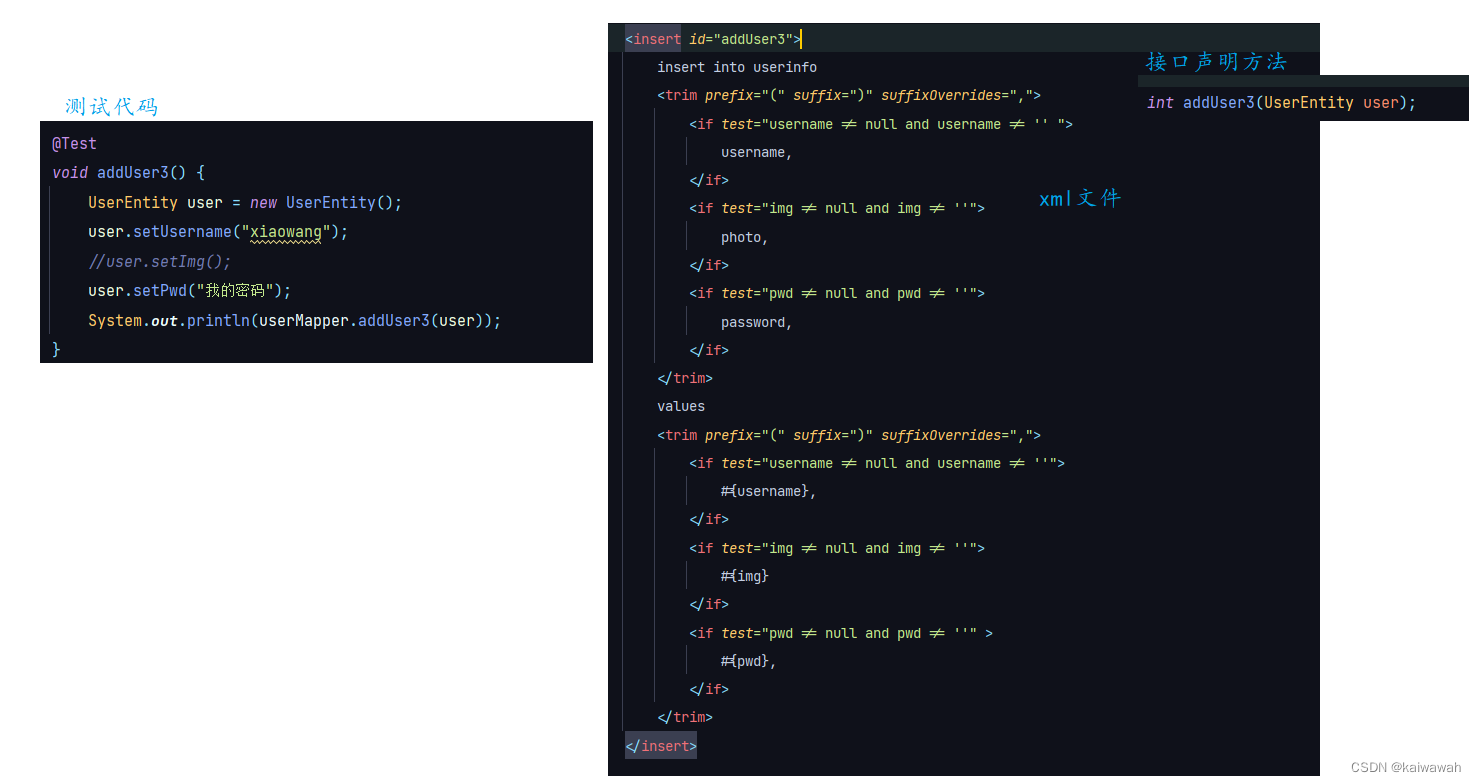

5 设置以及清除远端目的core

5.1 设置远端目的core

static inline void set_destination(int source, int mbox)

{

writel_relaxed(CHAN_MASK(source), ipc_base + IPCMxDSET(mbox));

writel_relaxed(CHAN_MASK(source), ipc_base + IPCMxMSET(mbox));

}

5.2 清除远端目的core

static inline void clear_destination(int source, int mbox)

{

writel_relaxed(CHAN_MASK(source), ipc_base + IPCMxDCLEAR(mbox));

writel_relaxed(CHAN_MASK(source), ipc_base + IPCMxMCLEAR(mbox));

}