这块ZYNQ-7000的二手板子很经典,最早在2019年被人发现。板子资源还是不错的,共引出了3*14个PL侧的IO,可用来研究PL、PS-PL交互,学习PS侧SDK,Linux开发。唯一的遗憾是Bank电压固定为3.3V,没法玩LVDS。

参考资料

- 从零开始的ZYNQ学习(基于矿卡EBAZ4205) (CSDN博客,主要偏PS侧,如Linux镜像构建)

- EBAZ4205入门 (英文,参考价值高)

- 基于EBAZ4205的FPGA学习记录 (PL PS工程共几十个,很详细,网站本身也很好)

- bilibili-ZYNQ 矿板开发教程-低成本开发板学习ZYNQ (一套教学视频)

- github-EBAZ4205 (这是矿板很多重要一手资料的源头)

- EBAZ4205资料集合 (gitee上汇总的资料)

- EBAZ4205学习资源整理 (cnblogs博客)

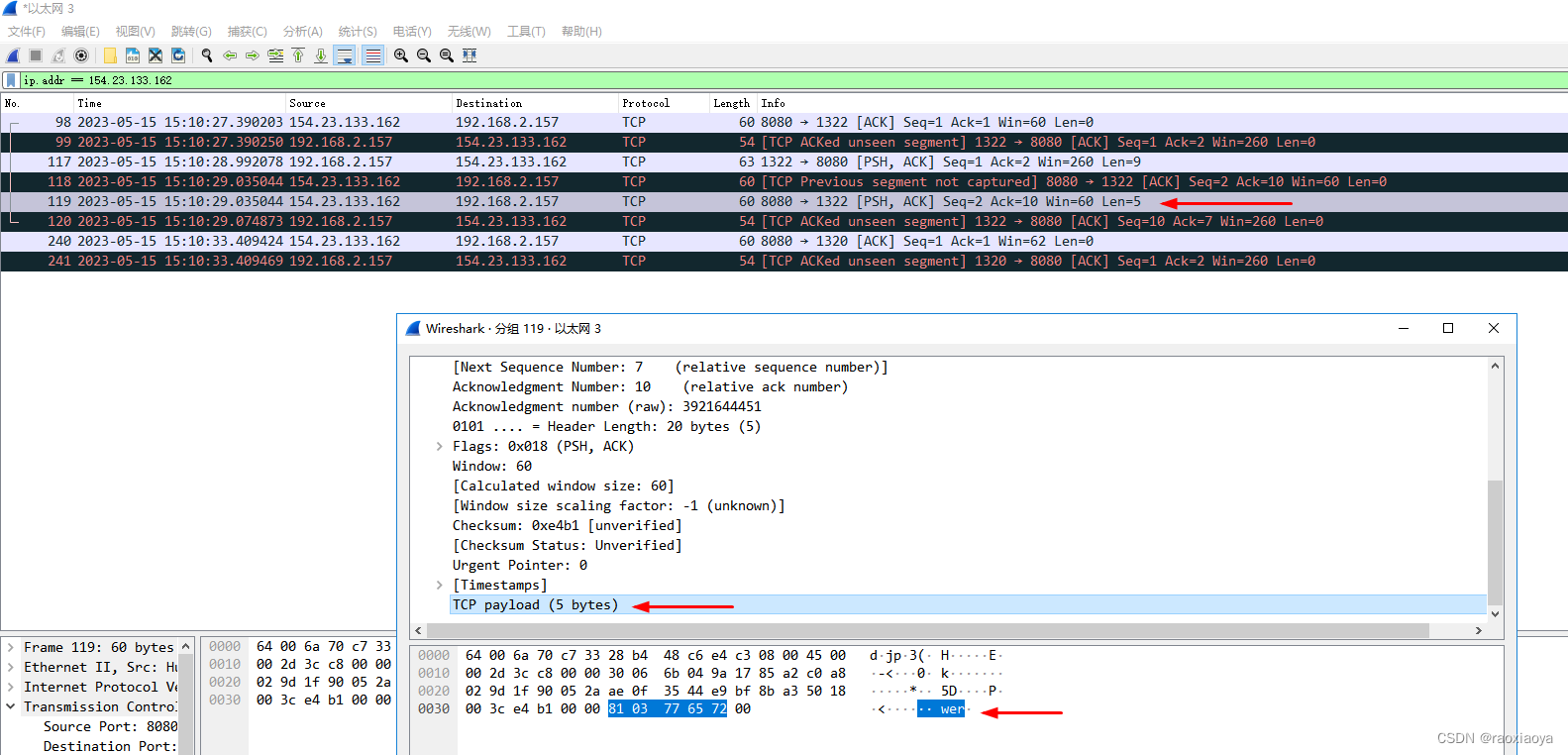

DATA1~DATA3连接器对应的FPGA引脚号:

(来自bilibili-ZYNQ 矿板开发教程-低成本开发板学习ZYNQ )

改造与验证

供电

左边的排线接口和右边的座子二选一。推荐使用排线接口,使用5557座还需注意板上的大二极管是否焊接。供电要求是5V,2A。

正确上电后的现象

PWR绿色LED常亮,下载成功指示灯在上电数秒后点亮。网口LED常亮约1min后闪烁。上电能从串口(4线排针)读出U-boot信息。

改造

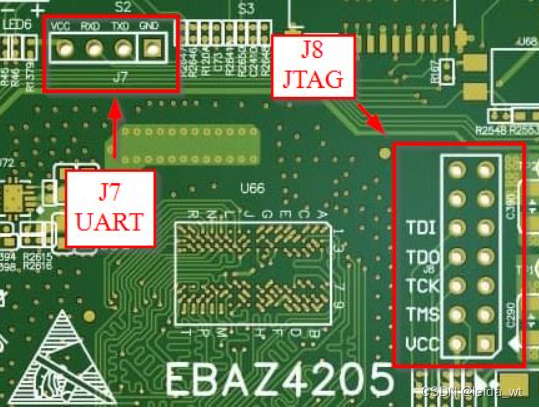

1. 焊接JTAG和串口的排针。

2. 为PL侧引入时钟信号

为节约成本,矿板的PL侧时钟是空焊的,内部从PS侧通过PS为PL提供时钟。这样编写纯PL程序就比较麻烦,必须例化并运行PS(仅例化还不行,必须运行PS侧程序,否则PS输出的时钟频率不正确)。

PL端时钟有多种输入方式(见ebaz4205硬件资源):

a. 补焊PL的50MHz有源晶振。

b. 与ETH PHY芯片IP101GA共享时钟源,板子上预留了R1485和PL端U18 pin相连,可以将该pin设置为时钟输入,作为PL的时钟源。

选择焊接R1485的方案,0402封装,33欧,使得25M晶振信号接入到U18管脚,U18(IO_L12P_T1_MRCC_34),是Bank34的一个支持MRCC功能的引脚。MRCC是多域时钟输入引脚,专用于输入时钟信号。

注意: 这个时钟频率比较低,只有25MHz,在使用ILA时需注意,ILA模块的时钟频率要大于2倍的JTAG频率ref。调试时需注意配置JTAG调试器频率。

3. 改造BOOT电阻(重要)

参考:EBAZ4205矿板ZYNQ7010 使用JTAG烧录程序到NAND并运行

虽然理论上任何BOOT模式下JTAG均可以使用,但是在PS有运行程序时,很大概率Vitis无法下载PS程序。为此,将板子上的R2578挪到R2585,从而将NAND启动改为JTAG启动。修改后上电直接进入JTAG模式,不会再执行NAND中的矿板程序,vitis调试就不会卡死了。

4. 改造XADC电源

矿板XADC电源没接到1.8V,可以飞个线,参考解决EBAZ4205矿板XADC读不到数据。