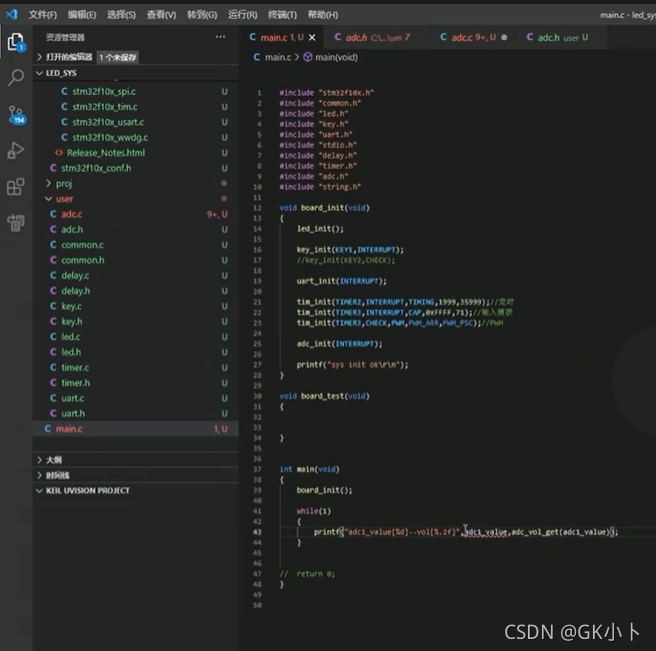

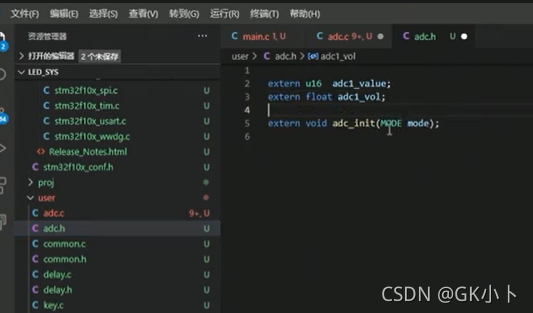

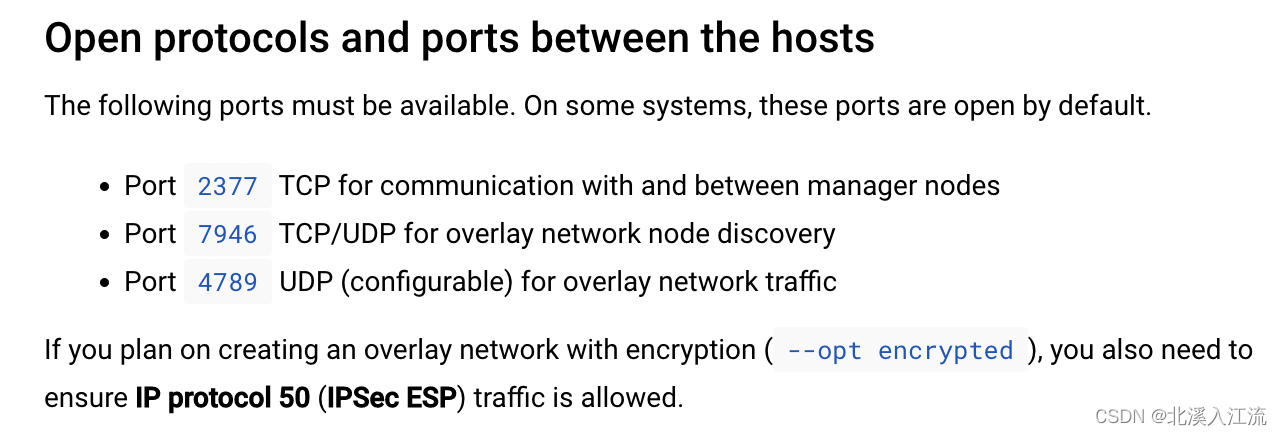

ADC原理:

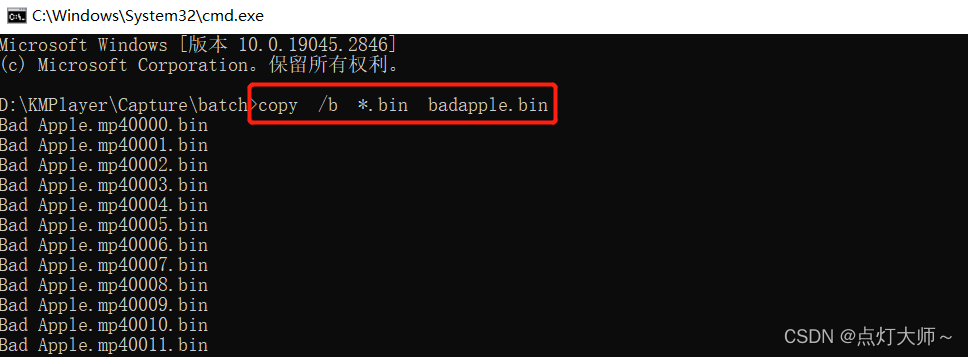

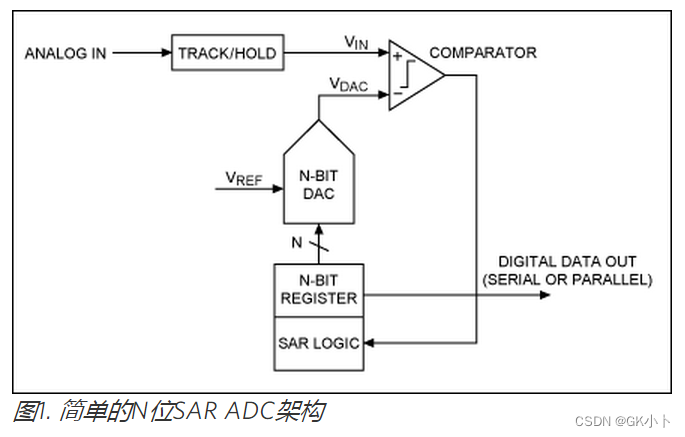

原理上是将采集保持器与DAC分开的,如下:

STM32 逐次逼近寄存器型(SAR)模拟数字转换器(ADC)

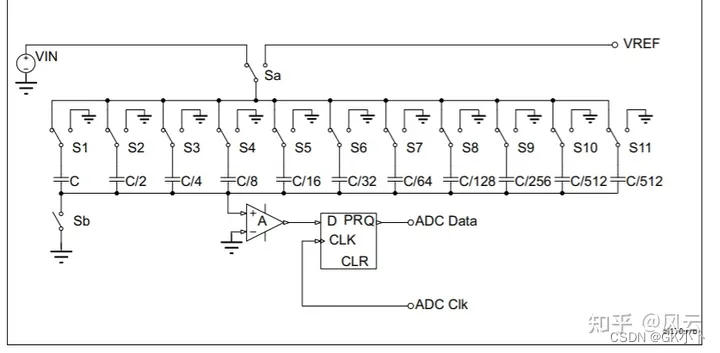

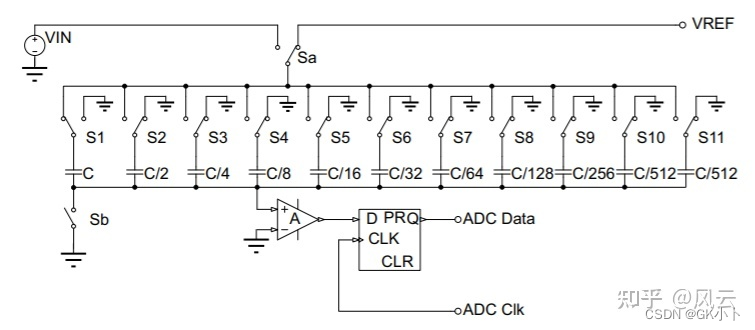

但实际电路可将DAC与采集保持器合并,主要运用的原理就是电容电荷再分配:

SAR ADC 逐次逼近型模数转换原理及噪声来源分析(以STM32内置ADC为例)

电荷再分配型SAR ADC

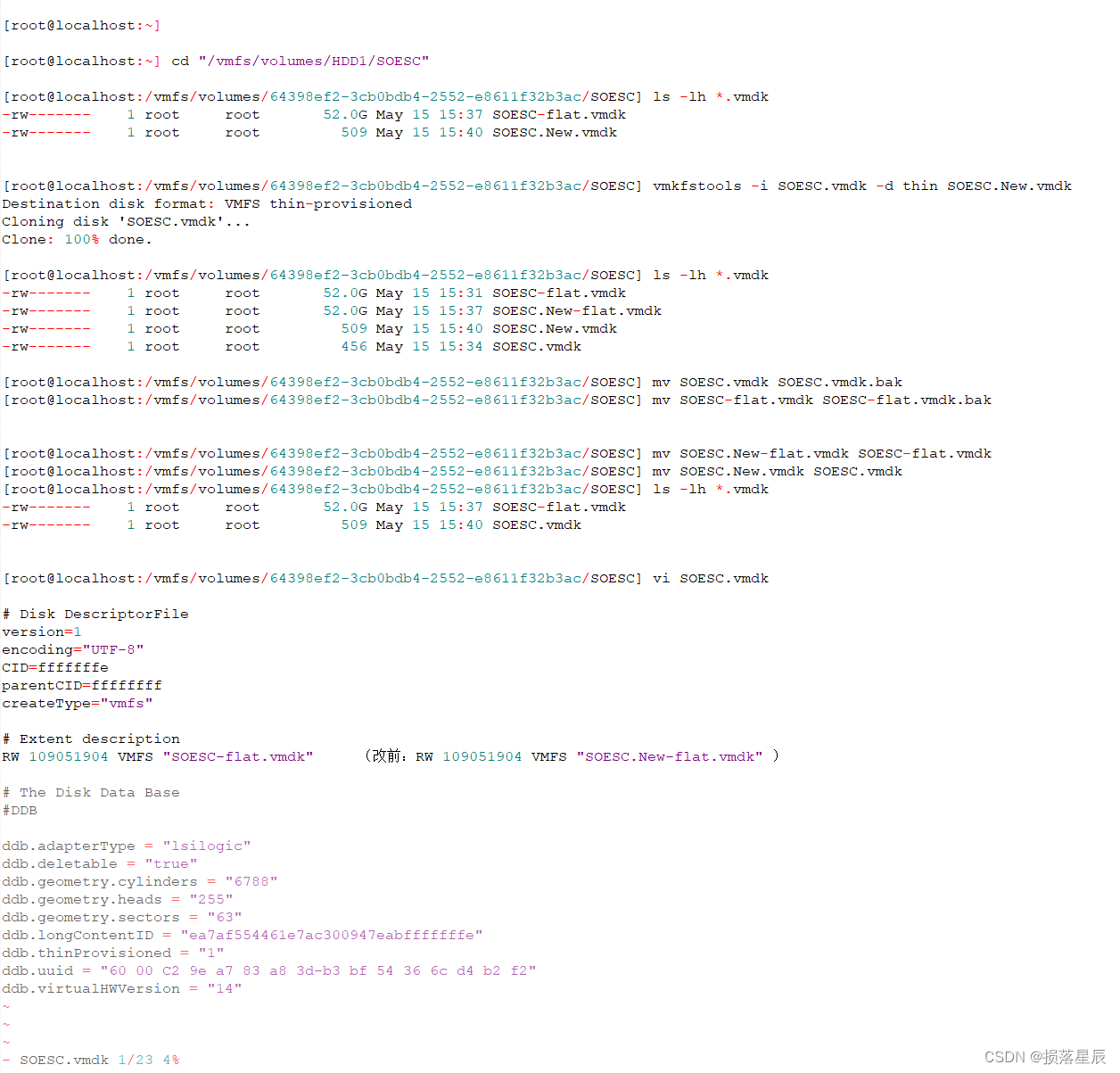

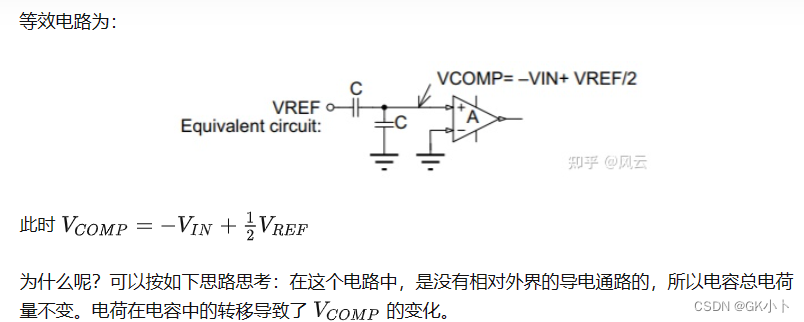

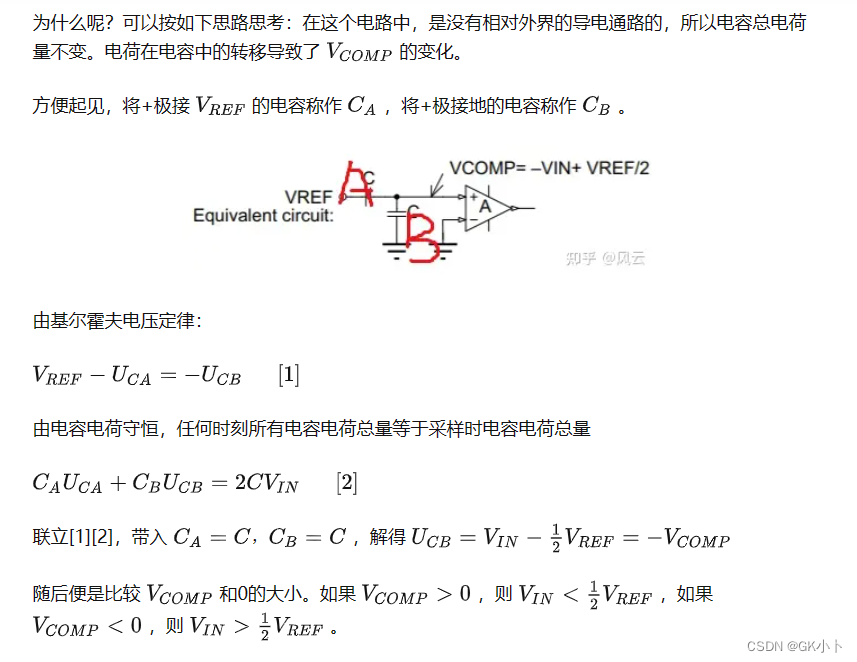

其中第四步进行比较电路见图如下:

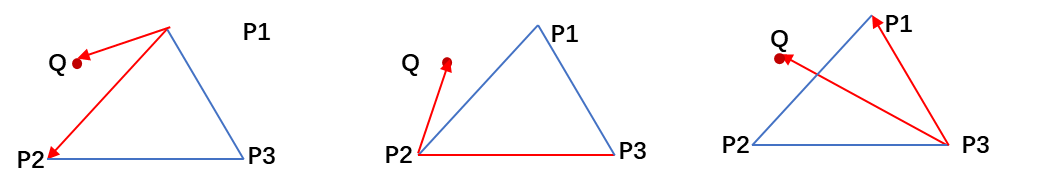

上述有两句话可能不太好理解:

说在这个电路中是没有相对外界的导电通路的,所以总电荷量不变。

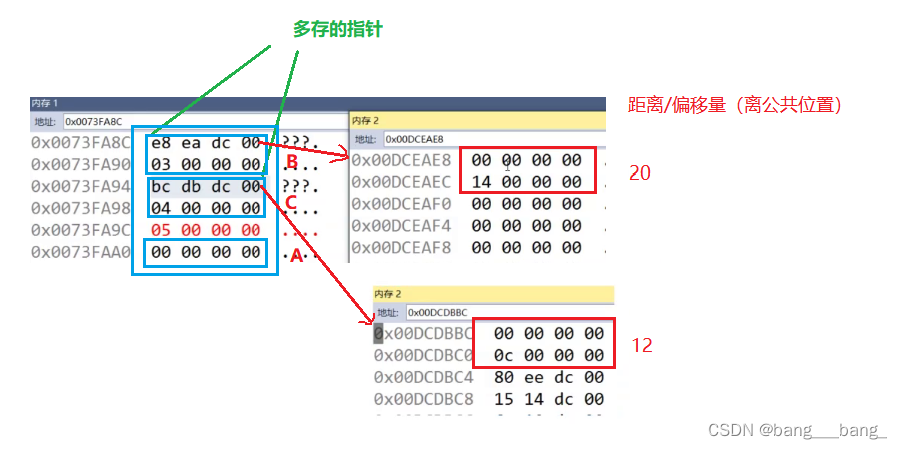

(这里不对,该电路还是有对外界导通的,S1线路接入Vref,还是会对电容充放电的,应该说是S1-S11的公共端电极板,也就是等效电路电容A的右极板是没有与外界导电导通的,所以该极板处根据电荷守恒,任何时刻电荷都守恒才得出上述2的公式)

联立公式1,2就可以得出Ucb = Vin - 1/2 Vref

该公式还有个更容易理解的方式,充电电容可以看做电源,在电容电路中该comp处电压为-Vin,等效电路即两个等值电容串联组成的分压器所以在Vref电路,该处电压为1/2 Vref,根据电路叠加Vcomp = -Vin + 1/2 Vref

电容的定义:

电容器的电荷量是指一个极板所带电量的绝对值

根据Q = CU可得

QA = CVin + 1/2 Vref

QB = CVin - 1/2 Vref

在等效电路中我们可以的到一个关系, Q总 = Vref * 1/2 C ,这里的1/2C是电容A和B的串联起来的等效电容

这里我们发现Q总并不等于QA + QB,这里我们忽略了一个问题,串联电容的等效电容公式初始条件是各电容电荷都为0才能使用该等效公式,如果电容初始时就有电荷,那么通过该公式算得的电荷就不是所有电容加起来的总电荷,只是接入电源后产生的电荷,然后再加上原来的电荷才是总的电荷

初始电荷都为空的电容,电容串联后接入电源各电容电荷相等,且等于总电荷,可以根据Q=I*T

串联电路的总电容与各分电容的关系

这里还有一个问题就是电荷量是绝对值,但电荷是有正负的

在该等效电路,当没有接入Vref时,A电容左极板的电荷为CVin极性+,B电容有极板的电荷为CVin极性为+

当接入Vref时,A电容左极板会被充电1/2Vref 极性+,根据叠加,A电容左极板(也即A电容)总电量为CVin + 1/2Vref

B电容右极板会被充电1/2Vref 极性-,根据叠加,B电容右极板(也即B电容)总电量为CVin - 1/2Vref

从上各种分析都能看出来A和B电容的电量确实是不变的,主要就是A电容的右极板和B电容的左极板(也即S1-S11所有电容的公共极板,被Vin充电后保持的)在该过程中并没有与外界导电导通,也就没有放电

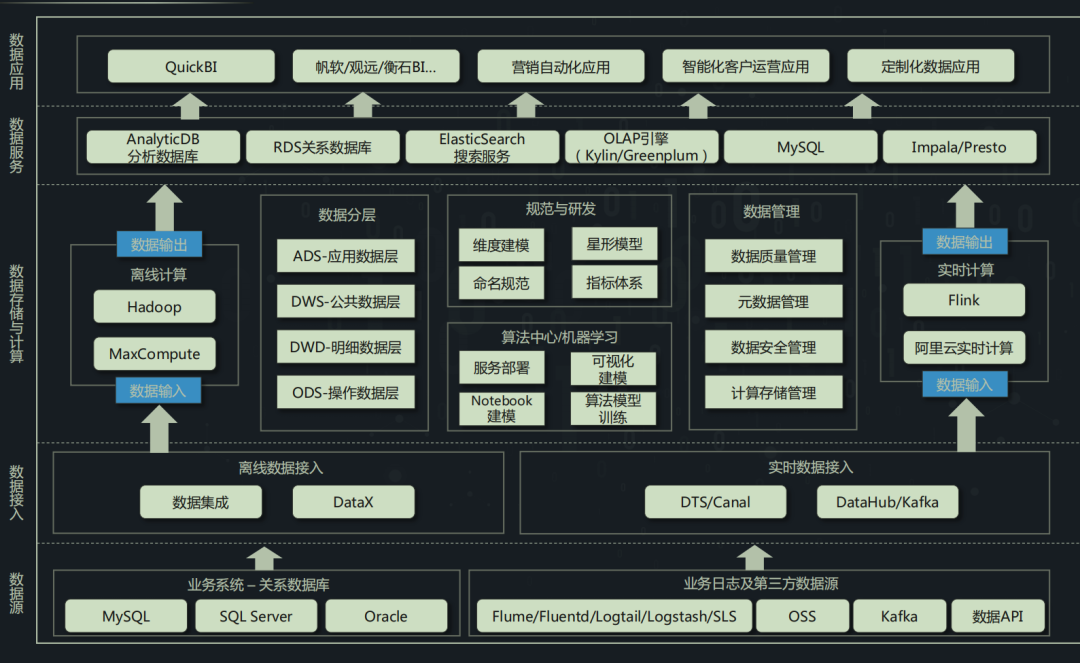

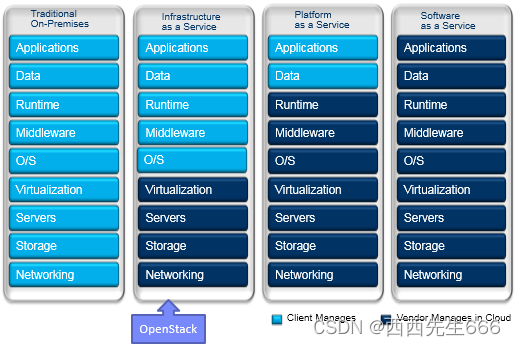

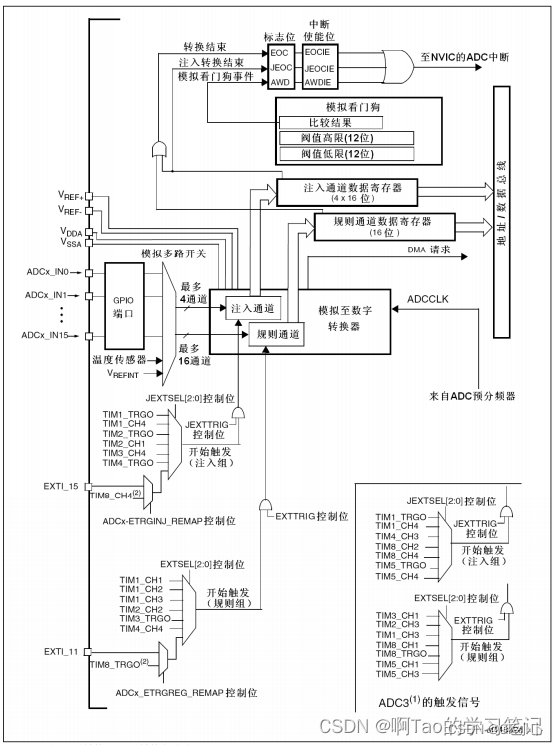

ADC模块架构:

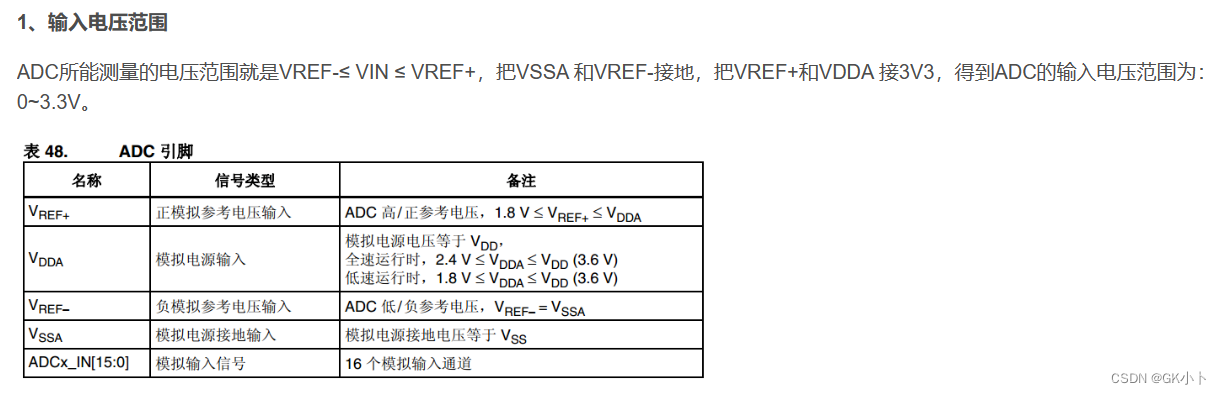

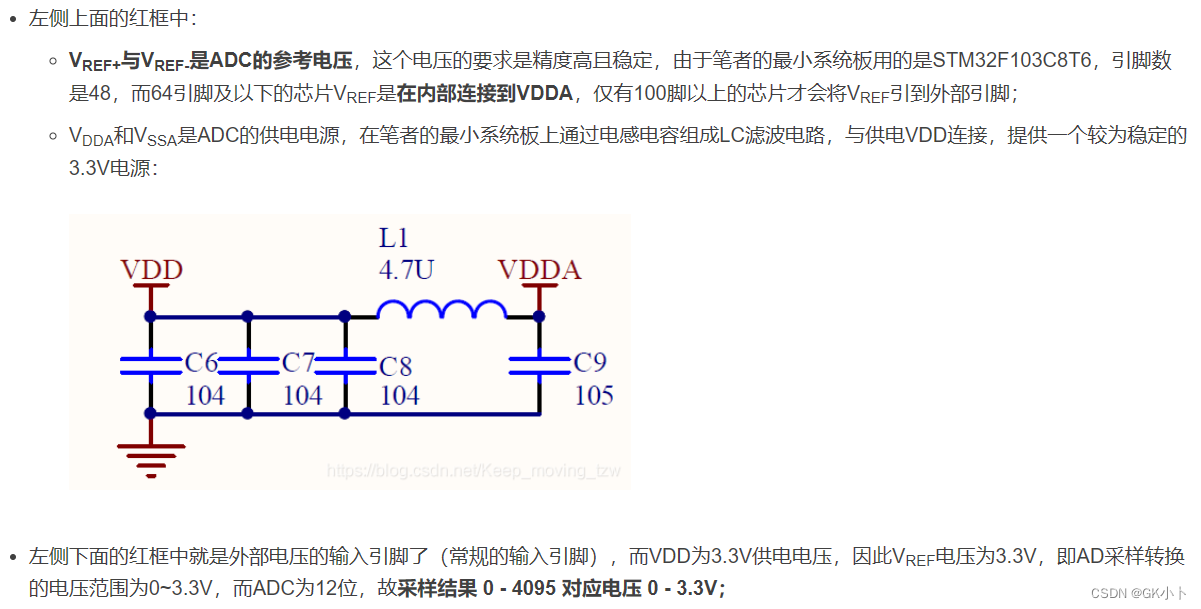

输入电压范围:

详细参考如下链接文章:

数据采集之ADC

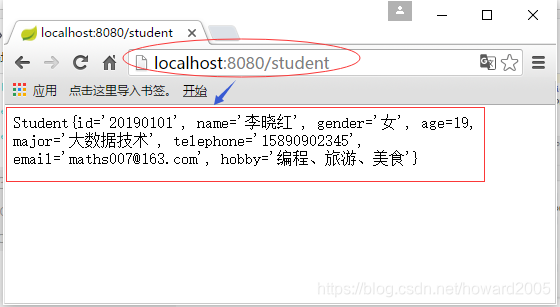

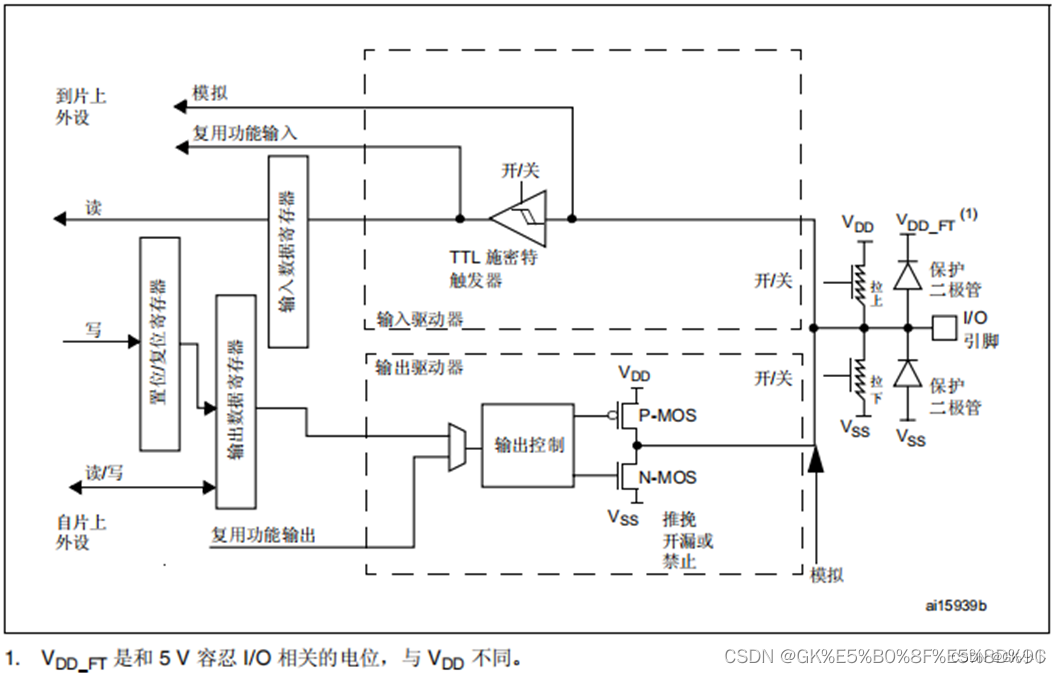

GPIO模拟输入引脚直接连接ADCx_INx引脚,所以GPIO引脚与ADC通道不需要映射

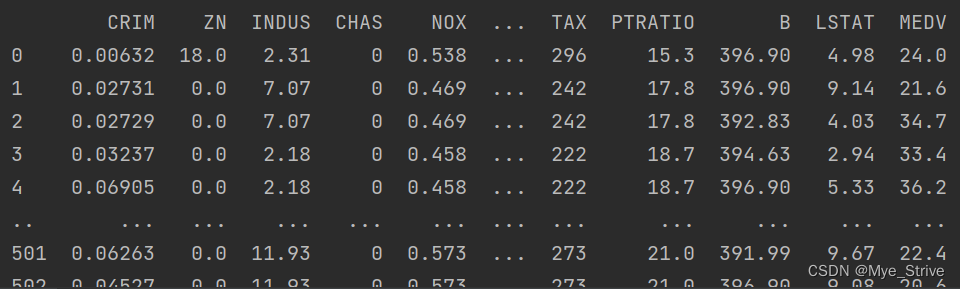

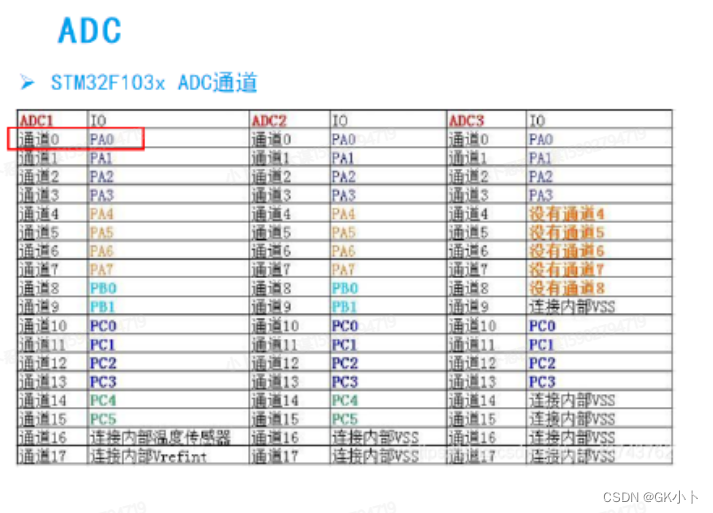

GPIO口对应的ADC通道:

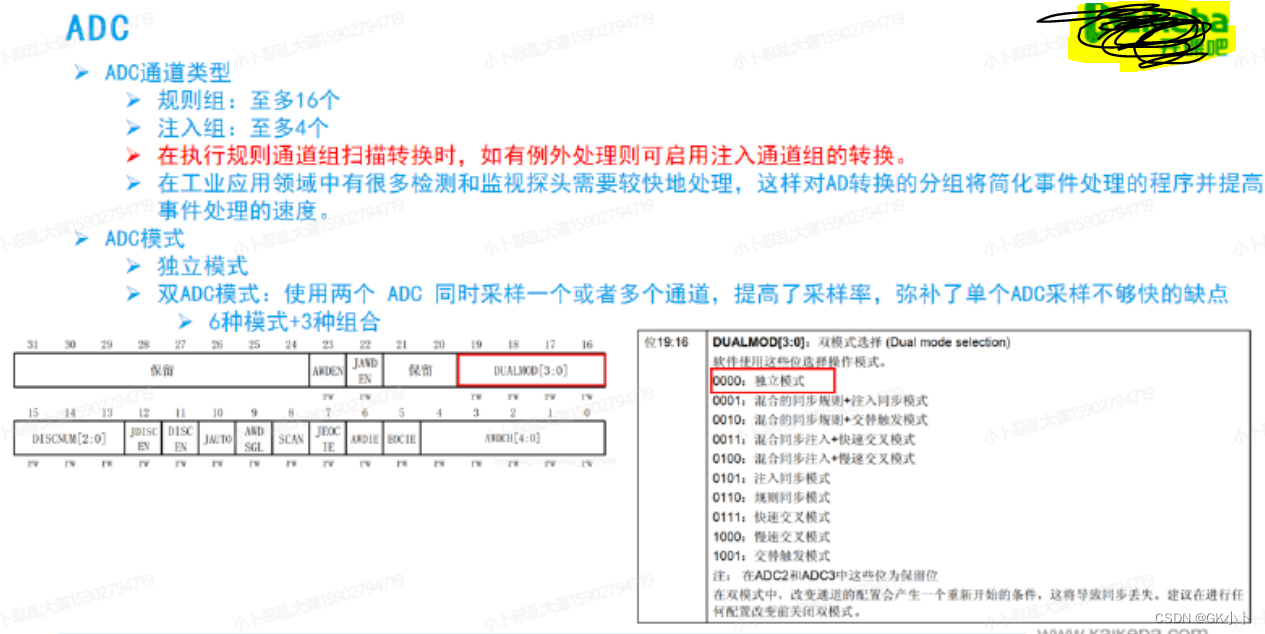

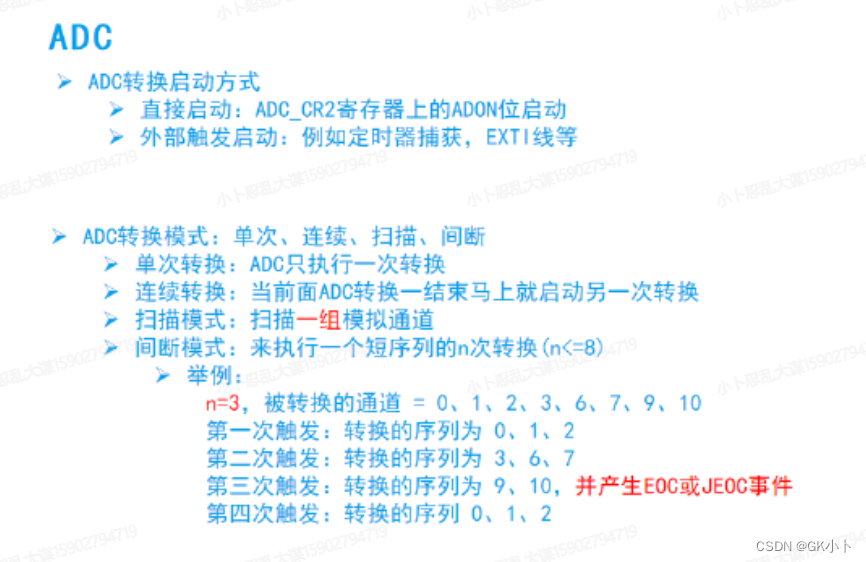

上述的ADC模式和转换模式不是一个意思,一个是控制几个ADC来采样,一个是在一个ADC采样应该采取什么样的模式,都是通过ADC_CR寄存器来设置

详细的转换模式解释可以参考如下链接文章:

STM32 的ADC解析

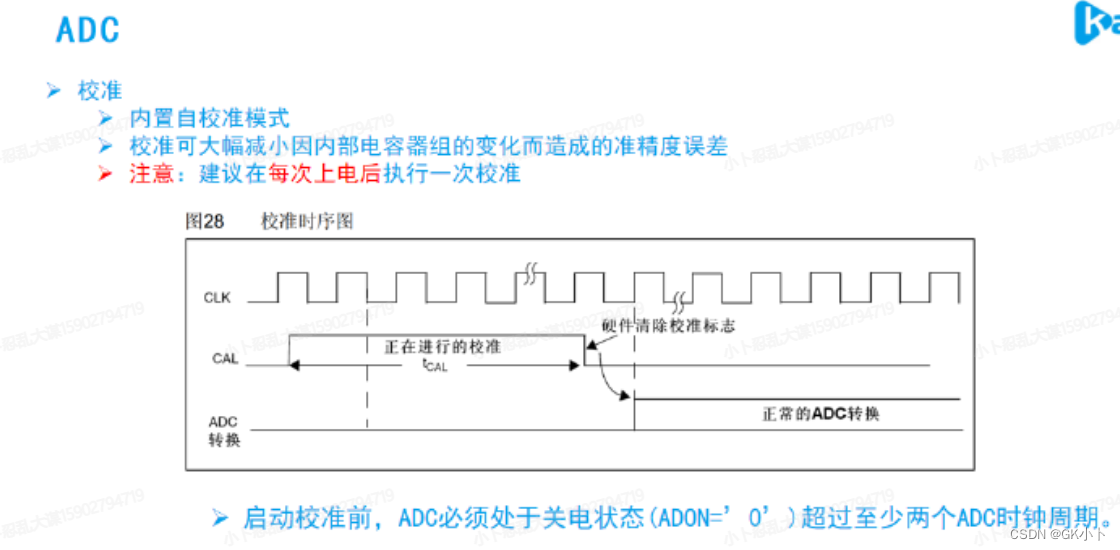

校准:

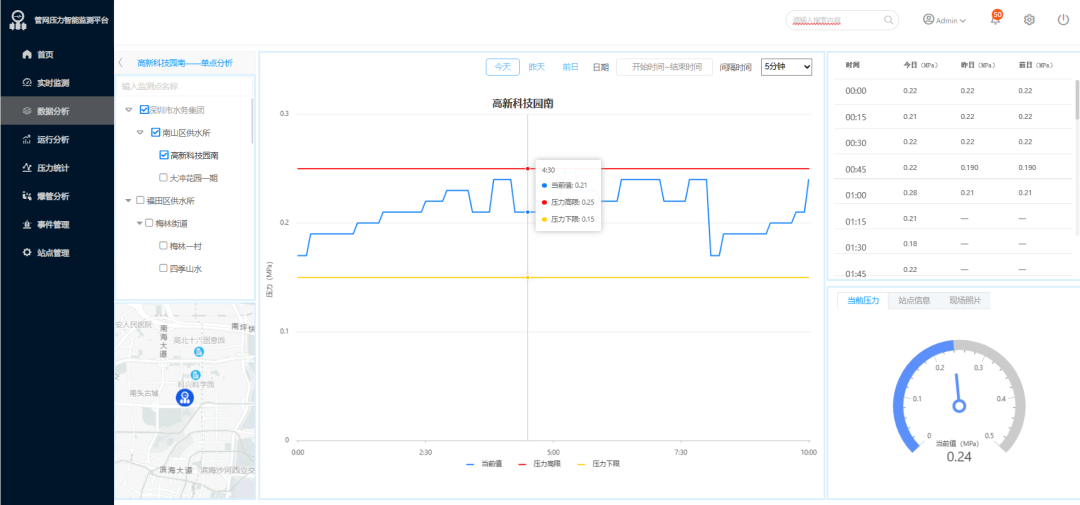

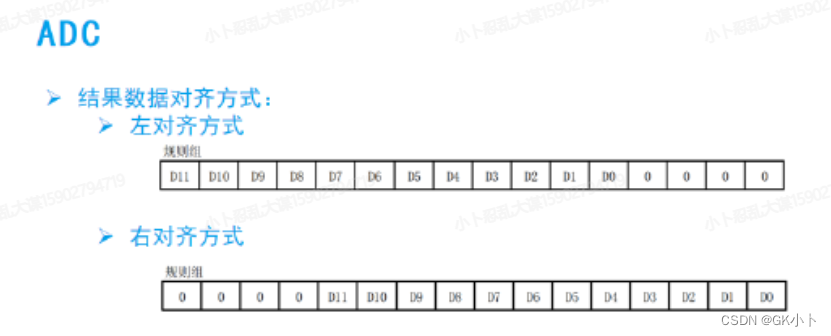

对齐:

因为stm32是数据存储是采用小端模式,1、即数据的低位存放在低地址处,2、stm32中低地址在右边,综上两个所以要采用右对齐

如果是大端加低地址左边的话就是采用左对齐了

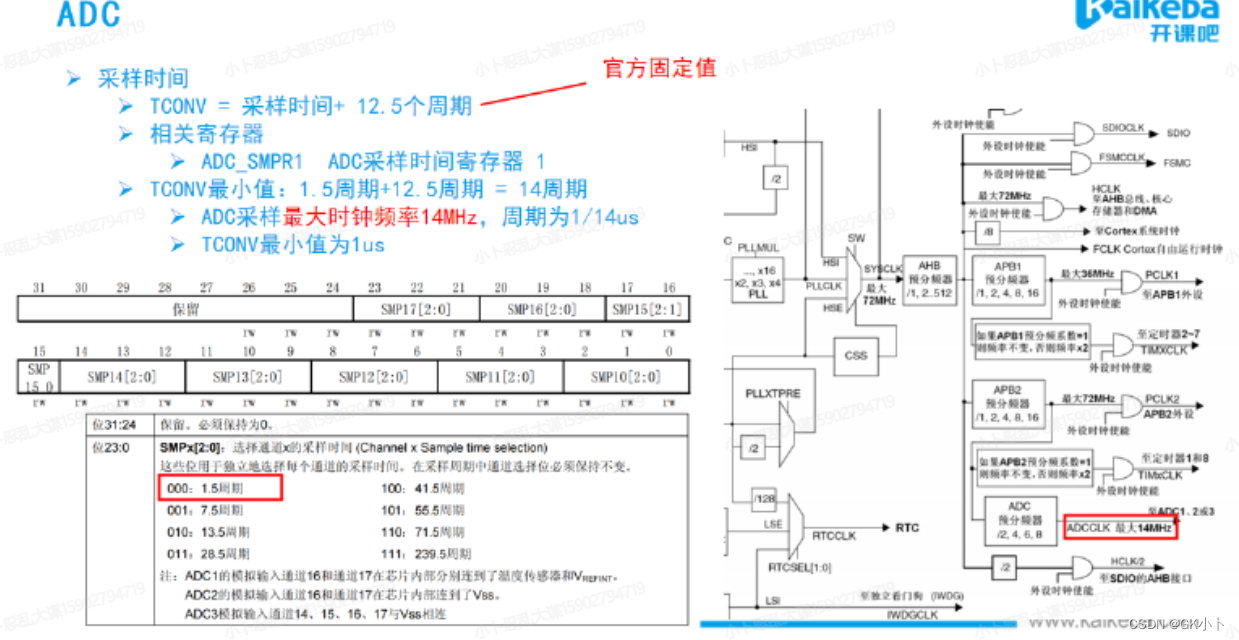

采样时间:

上述的12.5个周期应该是逐次比较的时间,应该改ADC的位数为12位