👉个人主页:highman110

👉作者简介:一名硬件工程师,持续学习,不断记录,保持思考,输出干货内容

参考书籍:《深入浅出SSD:固态存储核心技术、原理与实战》

物理层概述

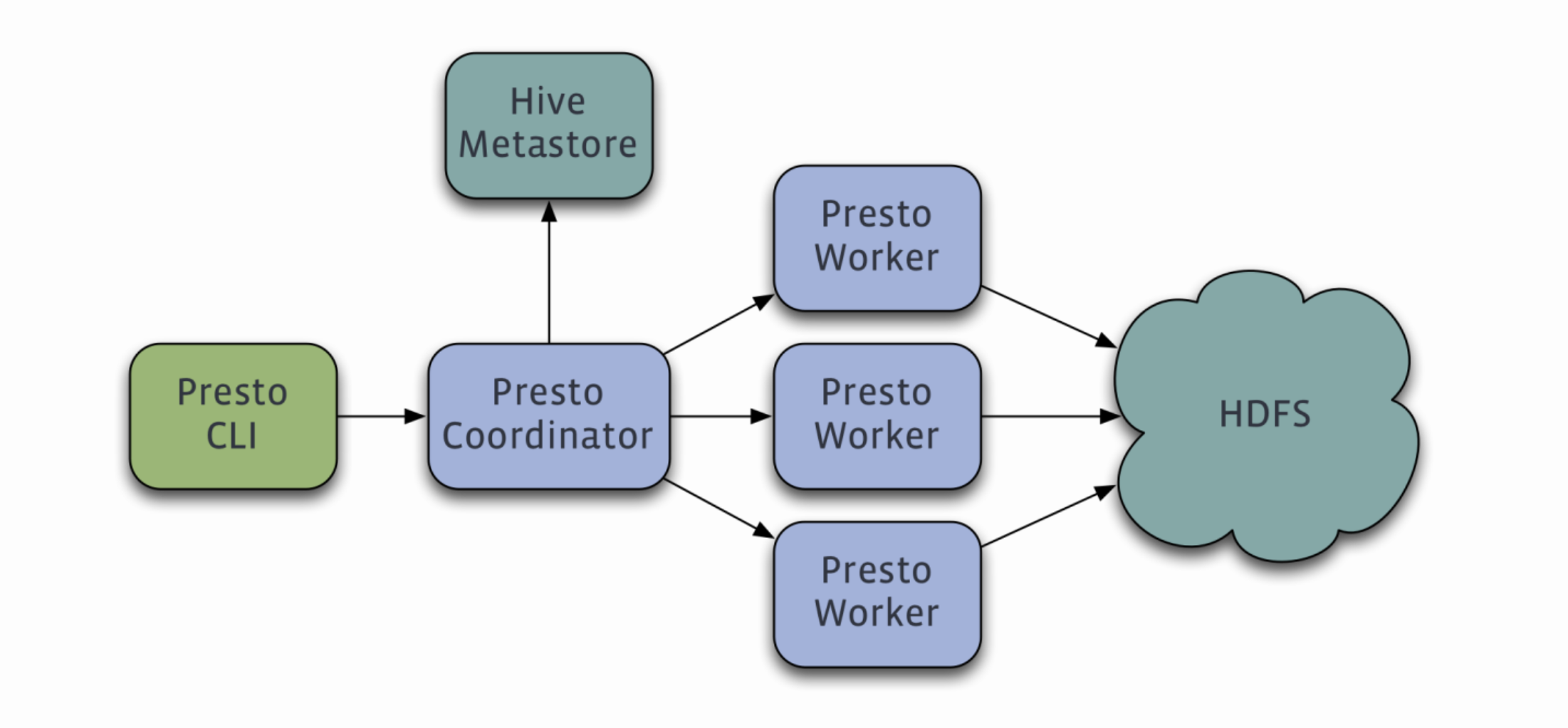

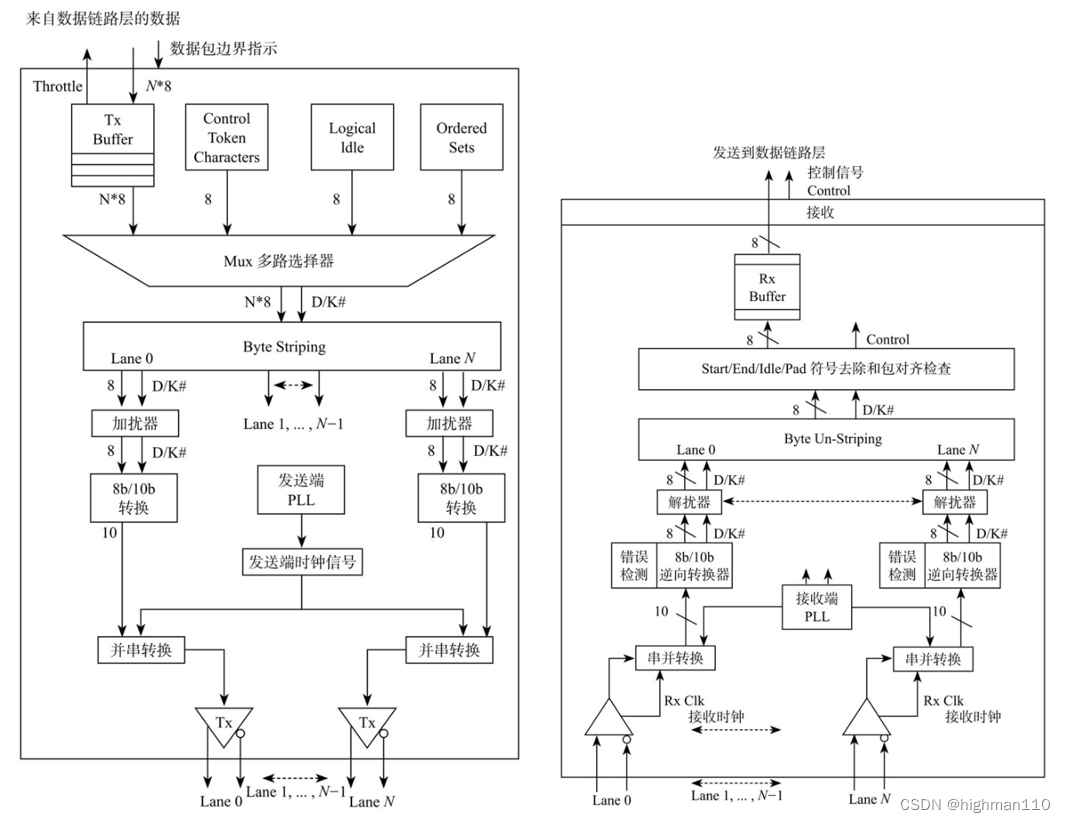

物理层为数据链路层之下的硬件底层,其主要作用有两个,一是传输TLP和DLLP,二是发送和接收物理层本身的报文PLP(physical layer packet)。物理层包括逻辑子层和电气子层,结构框图如下,左边为发送侧,右边为接收侧:

以发送侧为例进行说明:

物理层从数据链路层获得TLP或者是DLLP,然后放到TxBuffer里。

物理层给TLP或者DLLP加入头(Start code)和尾(End code、Gen 3之后没有给每个TLP或DLLP加尾巴,而是一段数据流加一个尾巴);给每个TLP或者DLLP加上边界符号,这样接收端就能把TLP或者DLLP区分开。加头尾之后通过MUX多路选择器,进入Byte Stripping。除了TLP、DLLP之外,物理层定义的PLP(order sets)、idle码流(在没有TLP、DLLP、PLP的时候发idle数据,编码之前是全0)、控制字符也可以通过MUX进入Byte Stripping。

PCIe链路上可能有若干个Lane。在物理层,TLP或者DLLP数据会分派到每个Lane上独立传输,这个过程叫Byte Stripping。在经过不同lane的走线延时后,lane与lane之间产生了skew,在接收端会进行de-skew。

数据进入每条Lane后,分别加扰(Scramble),目的是减少电磁干扰(EMI),手段是让数据与随机数据进行异或操作,输出伪随机数据,然后再发送出去。

加扰后的数据进行8/10编码(Gen3到Gen5都是128/130编码)。8/10编码是IBM的专利,目的主要有:让数据流中的0和1个数相当,保持直流平衡;嵌入时钟信息,PCIe不需要专门的随路时钟进行信号传输。这个scramble和8/10编码在之前的“以太网硬件”系列文章里也详细讲过,原理是一样的。

最后进行并串转换,发送到串行物理总线上去。

接收侧就是和发送侧相反,这里暂不多提。

关于物理层发送和接收的逻辑细节,后面会慢慢展开,将会解答几个问题:1、PCIE支持非同源的独立时钟架构,当发送和接收端时钟有偏差时,是怎么做到不丢包的?2、PCIE的不同lane差分对间并没有严格的等长要求,数据分散在不同lane中,接收端是怎么对齐的?3、从上面的框图看到,为什么发送端字节拆分放在扰码和8B/10B编码之前,这样每一条lane都需要一个扰码和8B/10B编码,这不是增加了成本吗,为什么不先做扰码和8B/10B编码再做字节拆分?