系列文章目录

第一章 计算系统概论

第二章 运算方法和运算器

第三章 多层次的存储器

第四章 指令系统

第五章 中央处理器

第六章 总线系统

第七章 外围设备

第八章 输入输出系统

文章目录

- 系列文章目录

- 前言

- 第五章 中央处理器

- 5.1 CPU功能和组成

- 5.1.1 CPU的功能

- 5.1.2 CPU的基本组成

- 5.1.3 CPU中的主要寄存器

- 5.1.4 操作控制器与时序产生器

- 5.2 指令周期

- 5.2.1 指令周期的基本概念

- 5.2.2 MOV指令的指令周期

- 5.2.3 LAD指令的指令周期

- 5.2.4 ADD指令的指令周期

- 5.2.5 STO指令的指令周期

- 5.2.6 JMP指令的指令周期

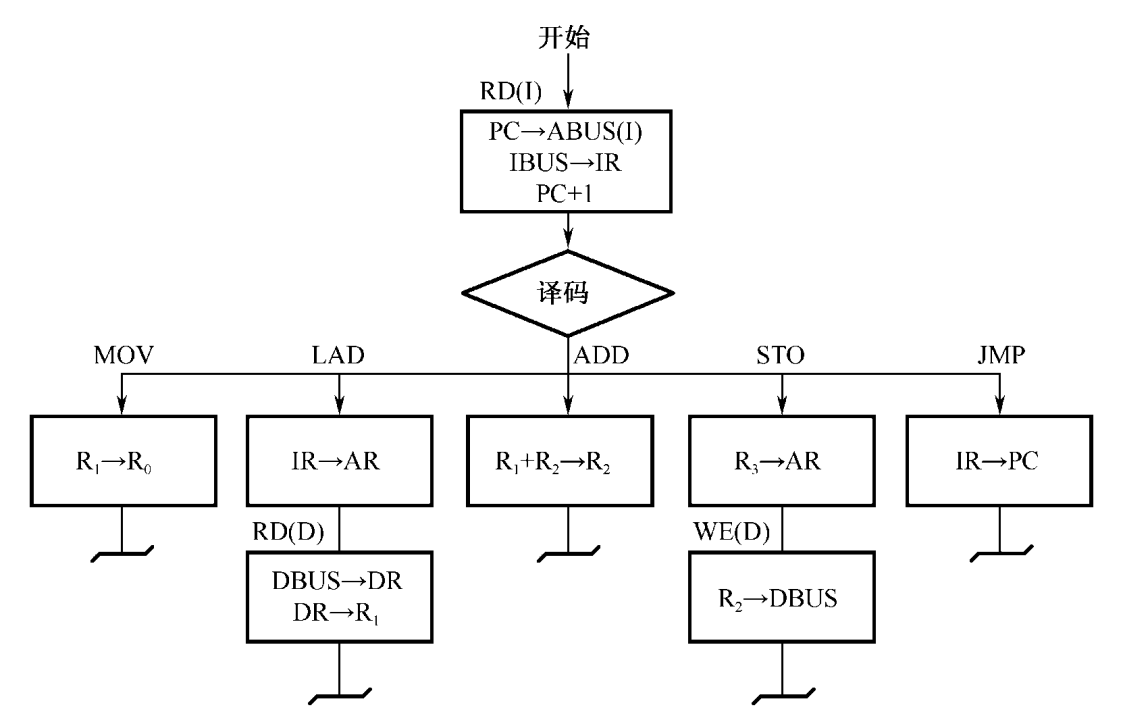

- 5.2.7 用方框图语言表示指令周期

- 5.3 时序产生器和控制方式

- 5.4 微程序控制器

- 5.5 硬连线控制器

- 5.6 流水CPU

- 5.7 RISC CPU

- 总结

前言

第五章 中央处理器

5.1 CPU功能和组成

5.1.1 CPU的功能

- 指令控制(程序的顺序控制)

- 操作控制(一条指令有若干操作信号实现)

- 时间控制(指令各个操作实施时间的定时)

- 数据加工(算术运算和逻辑运算)

5.1.2 CPU的基本组成

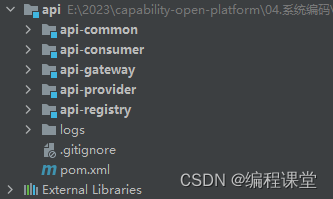

- 中央处理器CPU = 运算器 + cache + 控制器

- 运算器

- ALU

- 通用寄存器:R0~R3

- 暂存器:DR

- 状态字寄存器:PSW

- cache

- 指令cache:PC,IBUS

- 数据cache:AR,DBUS

- 控制器

- 控制器组成:程序计数器、指令寄存器、数据缓冲器、地址寄存器、通用寄存器、状态寄存器、时序发生器、指令译码器、总线(数据通路)

- 程序计数器PC(Programming Counter)

- 用来存放正在执行的指令的地址或接着将要执行的下一条指令的地址。

- 顺序执行时,每执行一条指令,PC的值应加1

- 要改变程序执行顺序的情况时,一般由转移类指令将转移目标地址送往PC ,可实现程序的转移。

- PC里有两个数据,正在执行的指令和即将执行的指令

- 指令寄存器IR(Instruction Register)

- 指令寄存器用来存放从存储器中取出的待执行的指令。

- 在执行该指令的过程中,指令寄存器的内容不允许发生变化,以保证实现指令的全部功能。

5.1.3 CPU中的主要寄存器

-

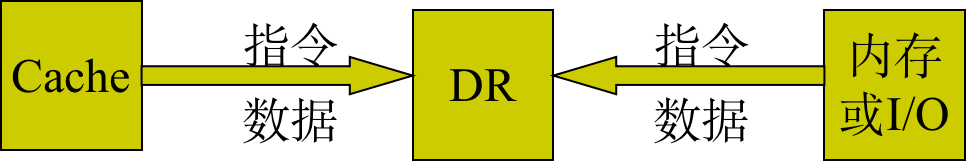

数据缓冲寄存器(DR)

- 中转站

- 补偿速度差别

-

指令寄存器(IR)

-

程序计数器(PC)

-

数据地址寄存器(AR)

-

通用寄存器(R0~R3)

-

状态字寄存器(PSW)

5.1.4 操作控制器与时序产生器

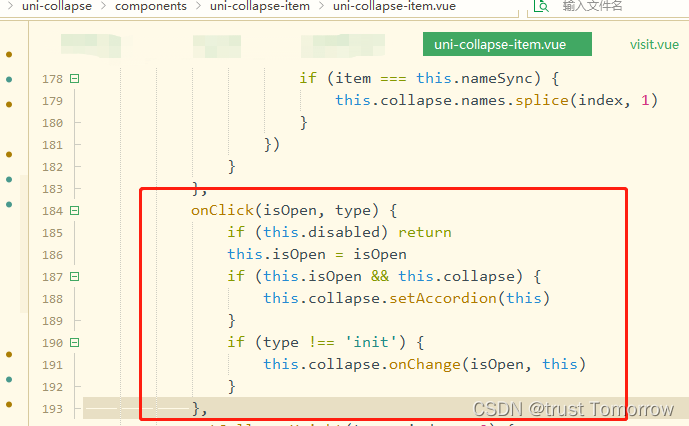

- 操作控制器:为数据通路(寄存器之间传送信息的通路)的建立提供各种操作信号。根据设计方法不同,可分为时序逻辑型和存储逻辑型:

- 硬布线控制器

- 微程序控制器

- 时序产生器:提供定时和时序信号

- 其他功能部件:中断系统、总线接口等

5.2 指令周期

5.2.1 指令周期的基本概念

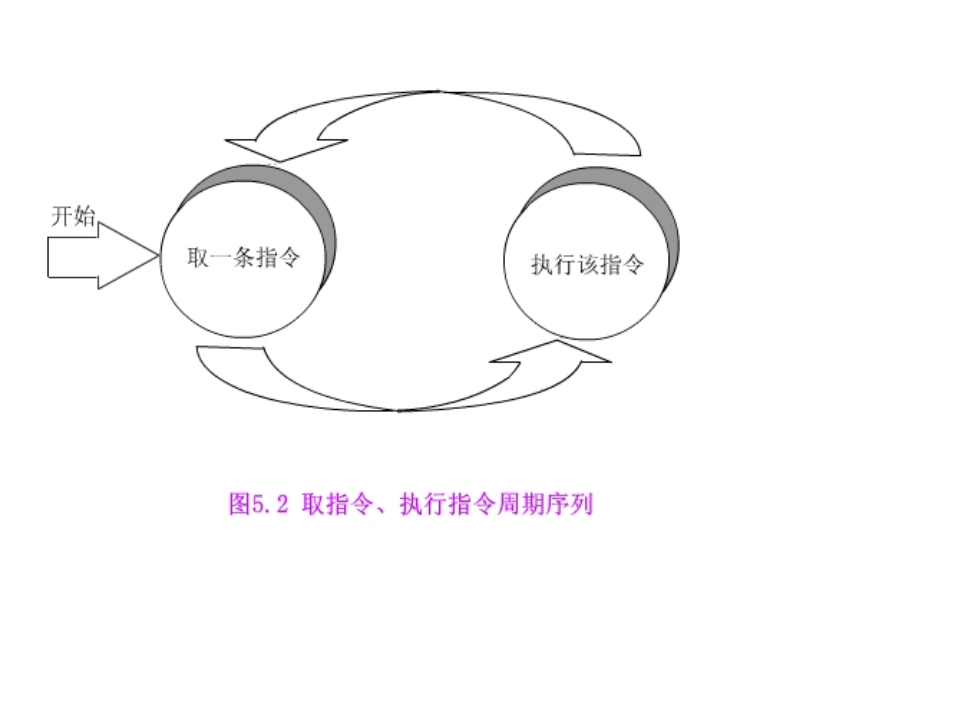

概念

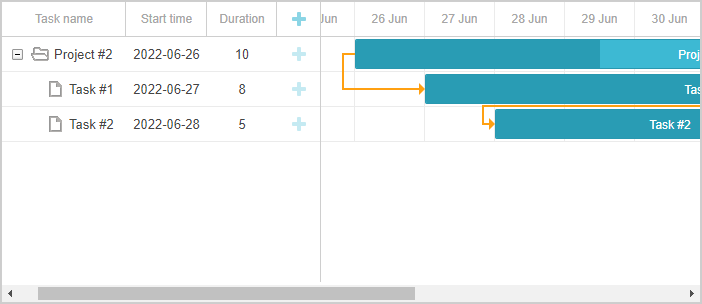

- 指令周期:指取指令、分析指令到执行完该指令所需的全部时间。

- 各种指令的指令周期相同吗?为什么?

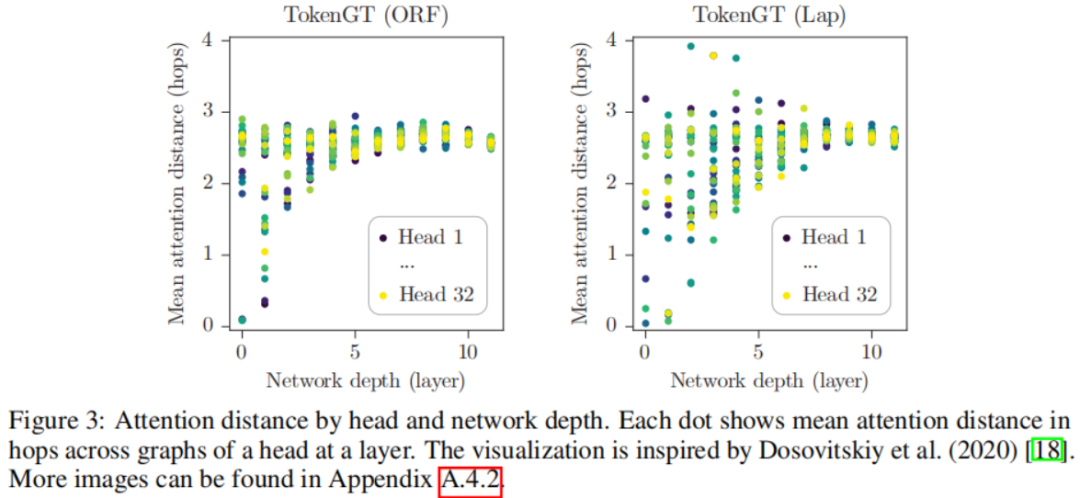

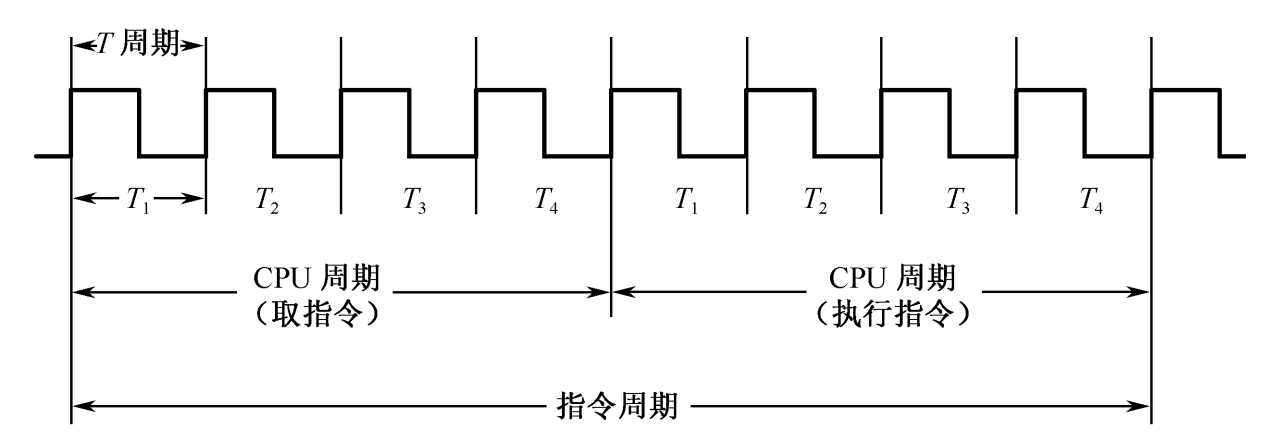

- CPU周期通常又称时钟周期

- 通常把一条指令周期划分为若干个机器周期,每个机器周期完成一个基本操作。

- 主存的工作周期(存取周期)为基础来规定CPU周期,比如,可以用CPU读取一个指令字的最短时间来规定CPU周期

- 不同的指令,可能包含不同数目的CPU周期。

- 一个CPU周期中,包含若干个节拍脉冲(T周期)。

- 单周期、多周期的概念

- 时钟周期

- 在一个CPU周期内,要完成若干个微操作。

- 这些微操作有的可以同时执行,有的需要按先后次序串行执行。

- 因而需要把一个CPU周期分为若干个相等的时间段,每一个时间段称为一个节拍脉冲或T周期。

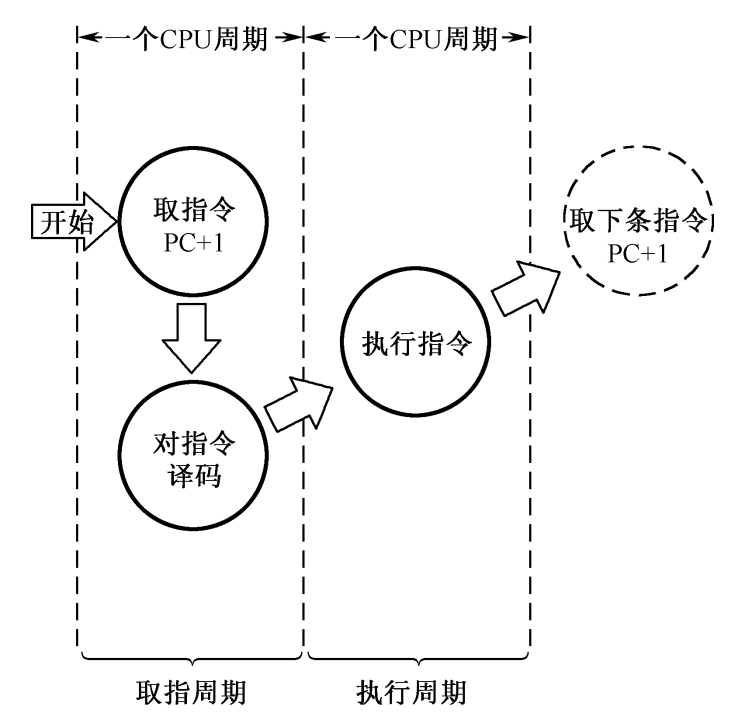

5.2.2 MOV指令的指令周期

- 移动指令

- 取指周期:1CPU周期

- 执行周期:1CPU周期

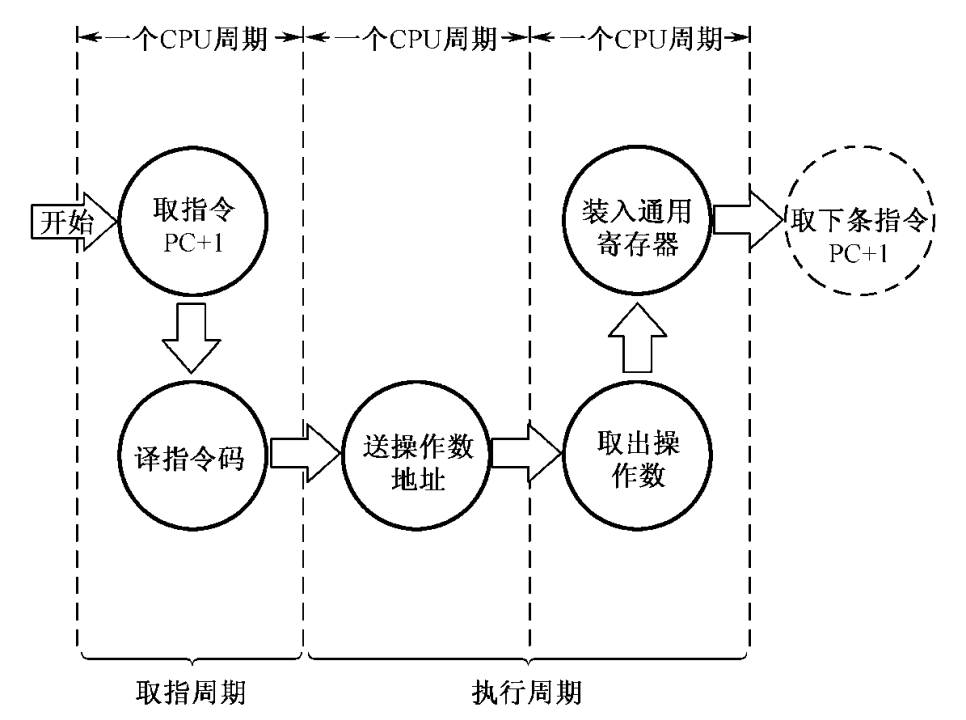

5.2.3 LAD指令的指令周期

- 加载指令

- 取指周期:1CPU周期

- 执行周期:2CPU周期(占用两次CPU总线)

5.2.4 ADD指令的指令周期

- 加法指令

- 第1个CPU周期取ADD指令(指令cache)

- 第2个CPU周期执行加法运算(运算器)

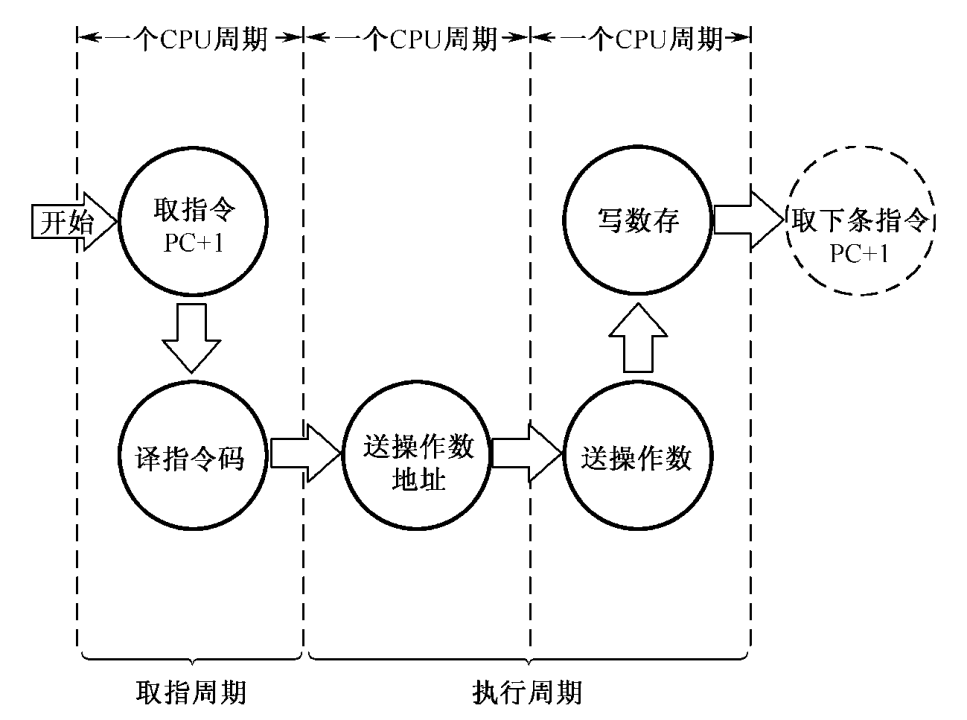

5.2.5 STO指令的指令周期

- 将通用寄存器的数据放到数据cache中(数据置换)

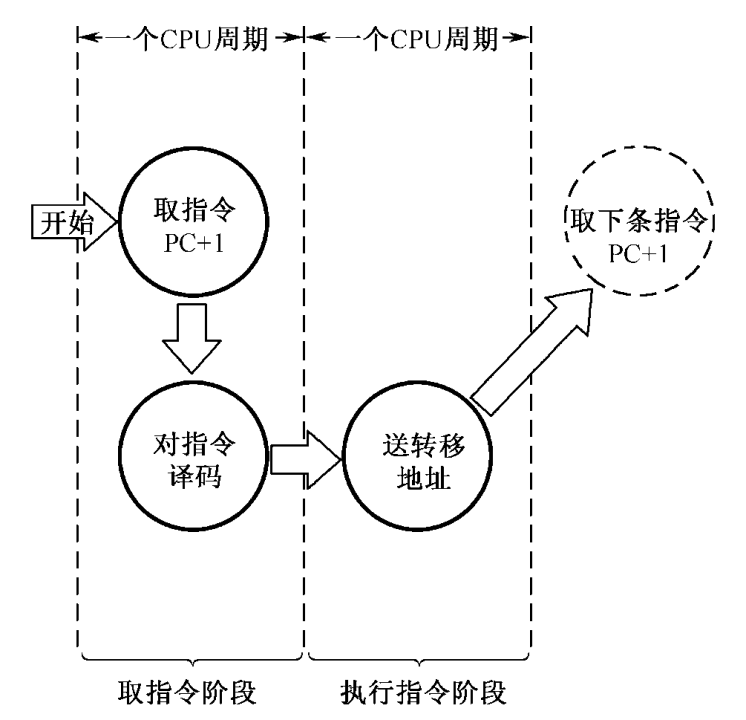

5.2.6 JMP指令的指令周期

- 跳转指令

5.2.7 用方框图语言表示指令周期

- 引入目的主要是为了教学目的(控制器设计)

- 方法:

- 指令系统设计(模型机的五指令系统)

- 方框——按CPU周期

- 方框内内容——数据通路操作或控制操作

- 菱形符号——判别或测试

- ~ ——公操作

- 前边所讲述的5种操作的框图描述