vivado用习惯了,现在快速换到quartus下仿真测试。写一个操作文档,以fpga实现pcm编码为例。

目录

一、建立工程

1、准备源码和仿真文件

2、新建工程

3、加载源文件

4、选择器件

5、仿真器配置

6、工程信息

二、配置工程

7、设置顶层文件

8、配置仿真

9、配置仿真工具路径

三、编译仿真

10、编译

11、仿真

12、正弦波形配置

12.1 Radix配置

12.2 Format配置

一、建立工程

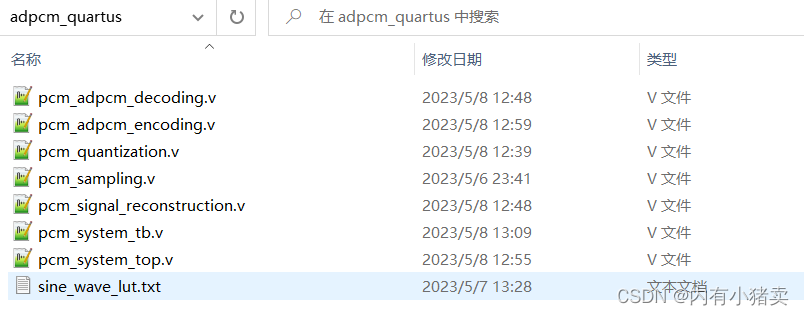

1、准备源码和仿真文件

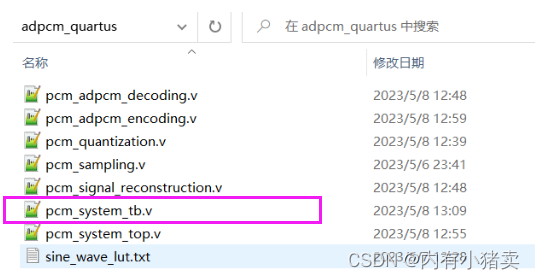

首先在非中文路径下新建一个目录adpcm_quartus,放进去源码和仿真文件

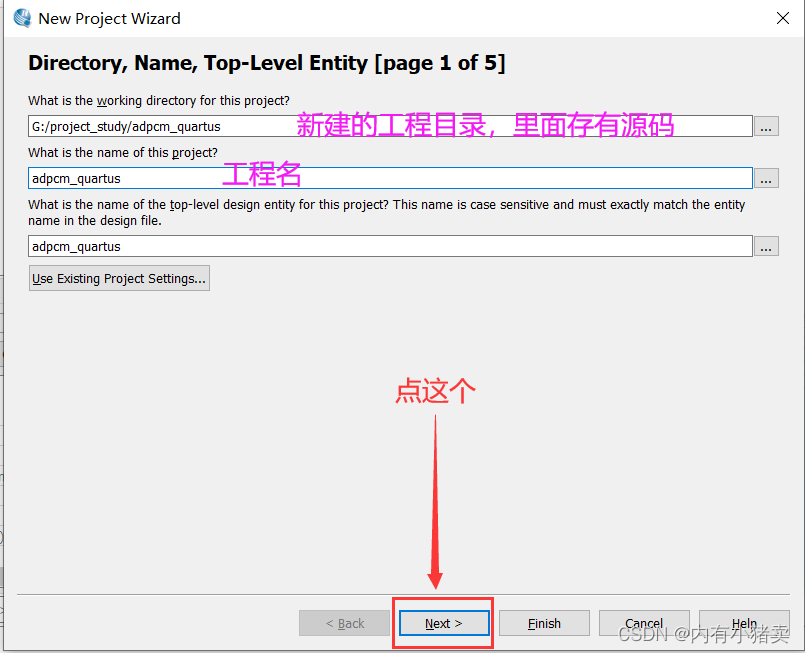

2、新建工程

打开quartus II 13.1,file -> new project wizard,新建一个工程。

3、加载源文件

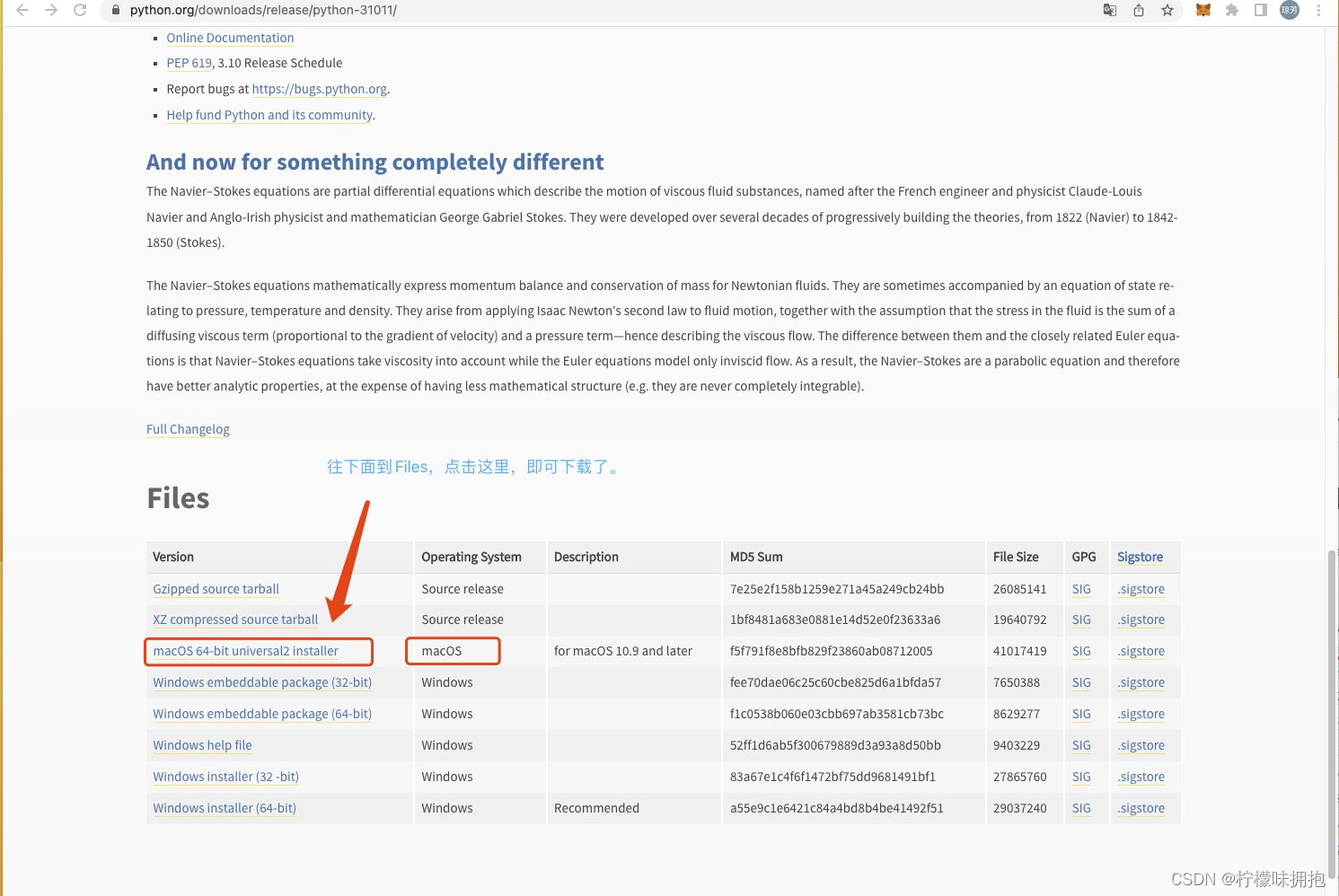

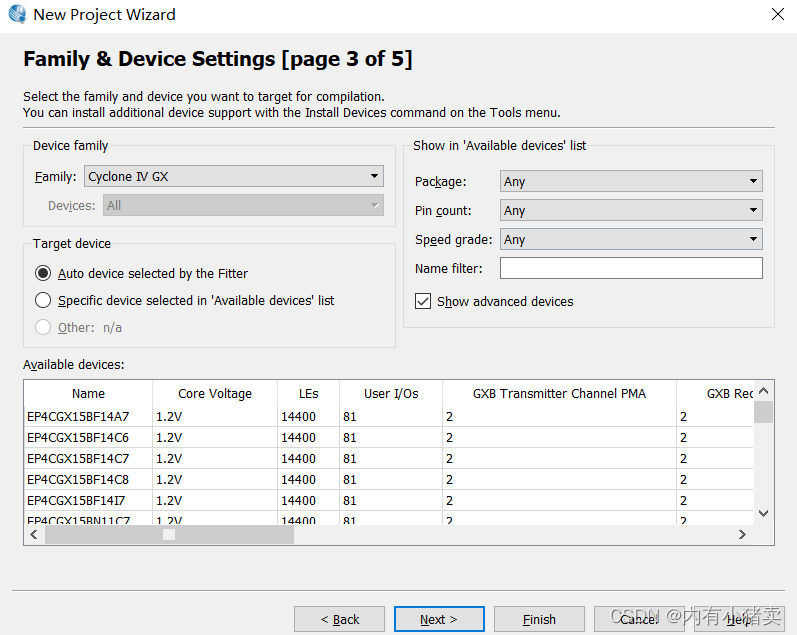

4、选择器件

根据自己的需要随便选,如果不下板子,就点next

5、仿真器配置

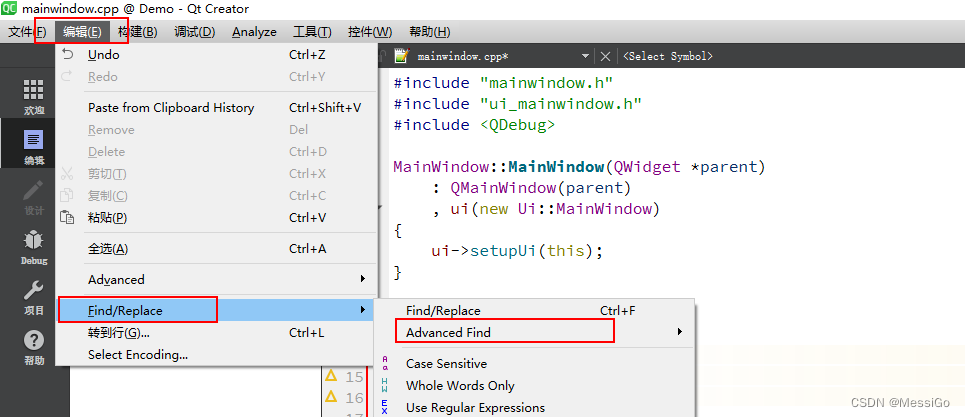

这个仿真器配置只针对该工程,不影响其他工程使用。选择modelsim和verilog hdl。

为啥不使用modelsim-altera呢,因为这样就要按照quartus的格式修改tb文件,比如删除,否则加载不出来波形。

6、工程信息

点finish

二、配置工程

7、设置顶层文件

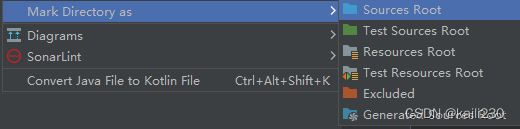

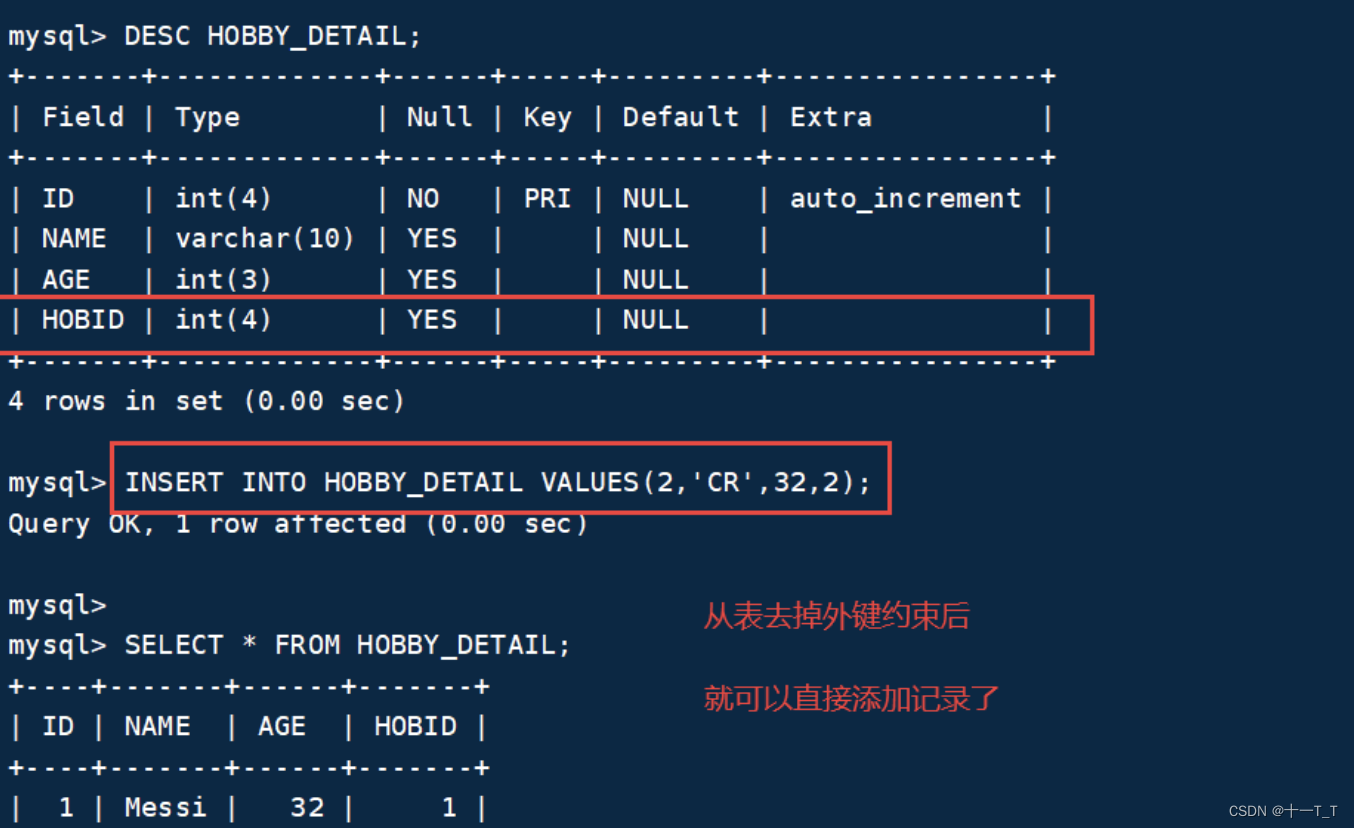

我们导入的源文件里面有一个顶层文件,但是quartus不知道哪个是顶层,手动将其配置为顶层文件。

如果没配置顶层就会报错,如下图:

8、配置仿真

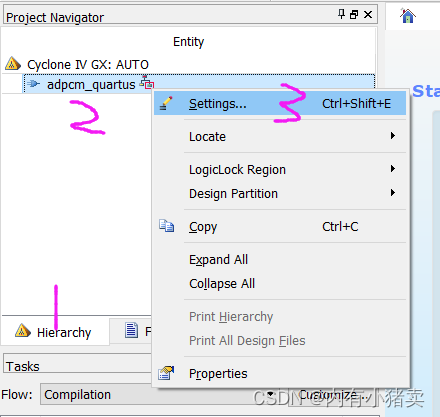

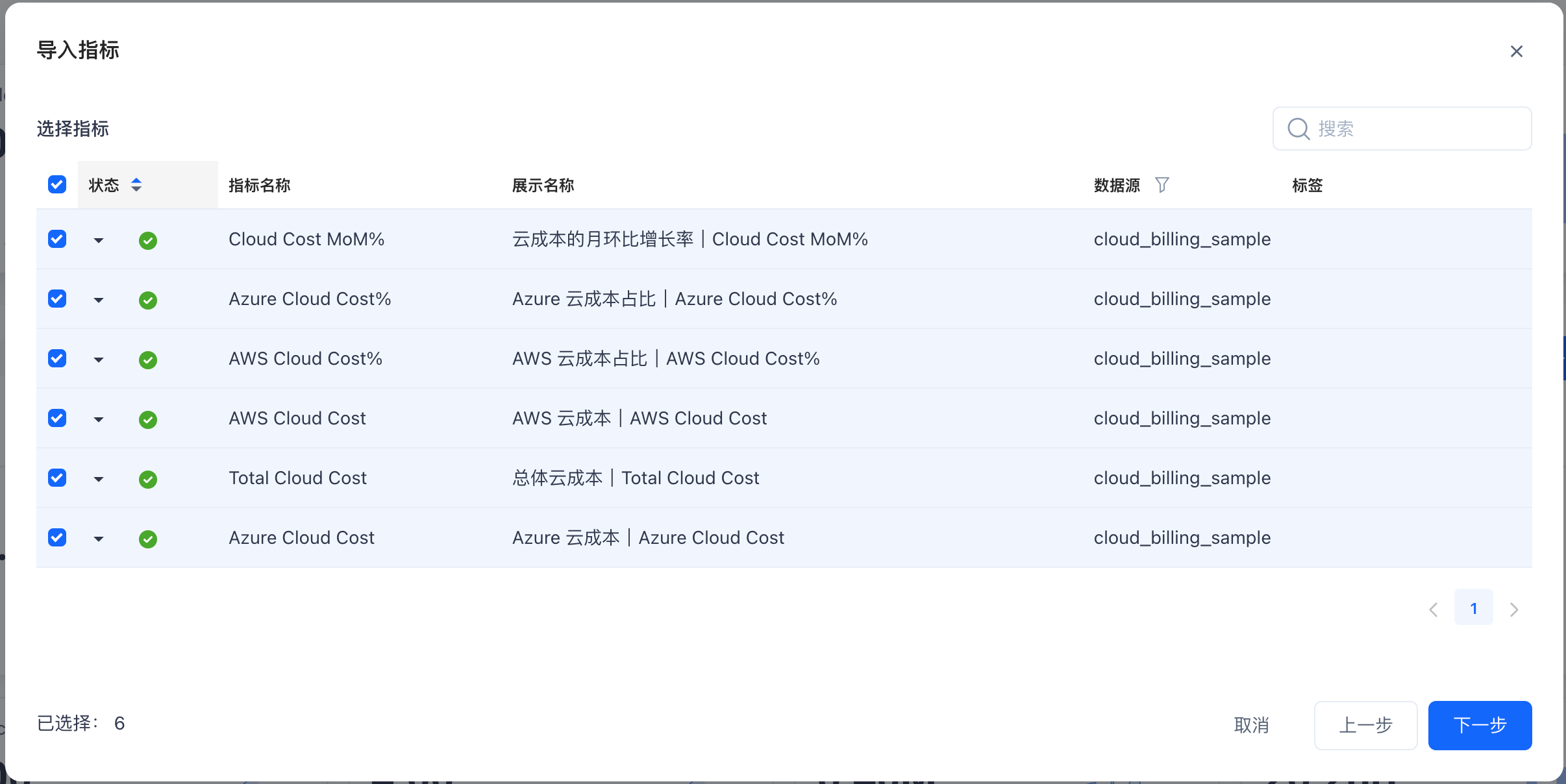

8.1 点击进入setting界面下,

进入以后,我们可以看到仿真工具名字为modelsim,如果不是,改过来。

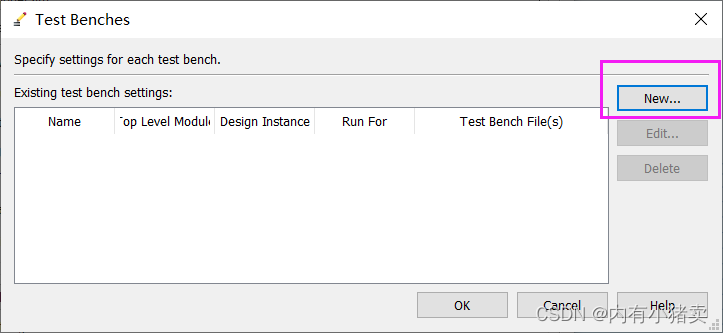

点击"Test Benches"按钮,进入仿真文件加载界面。

点击”new“,加载文件。

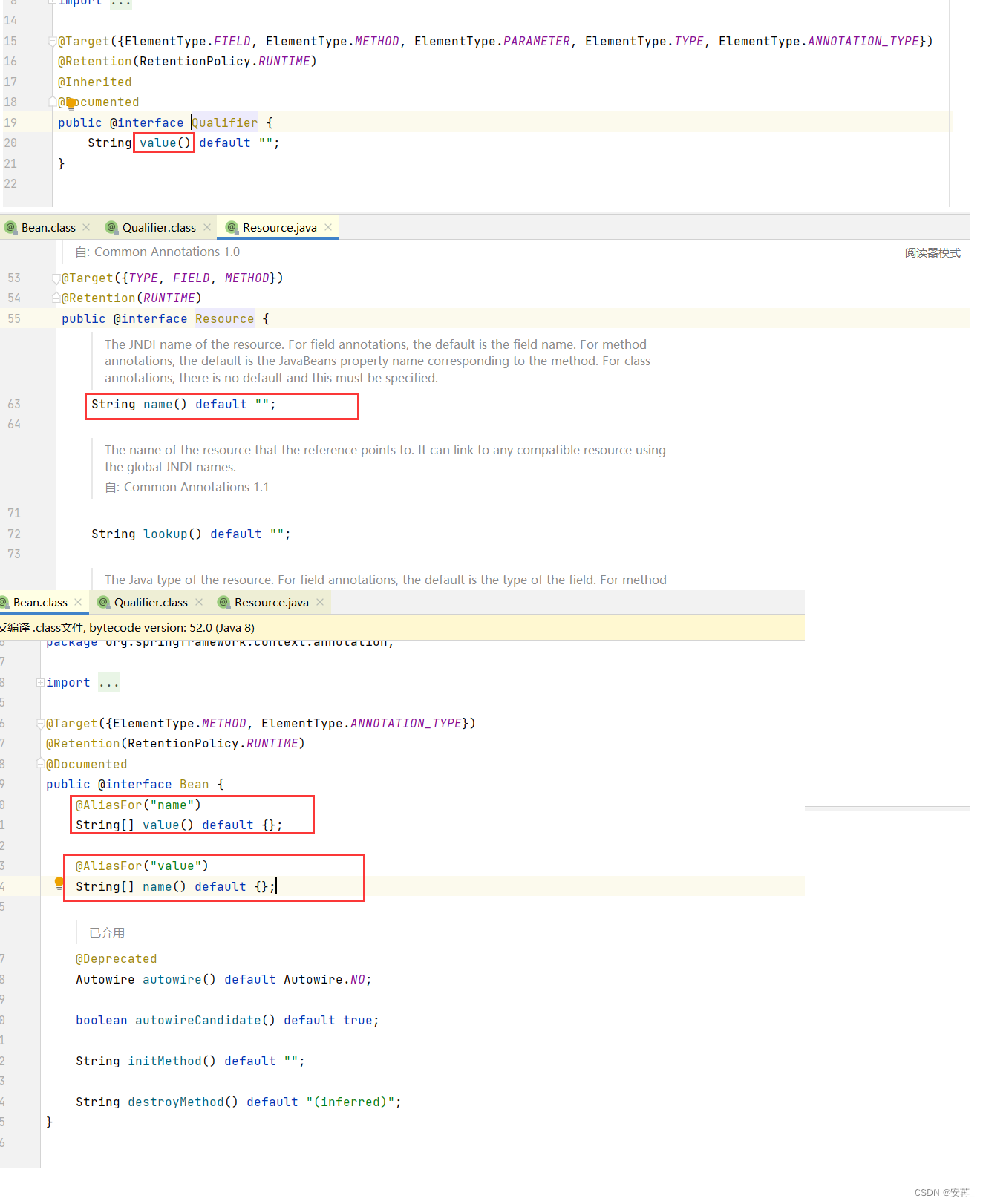

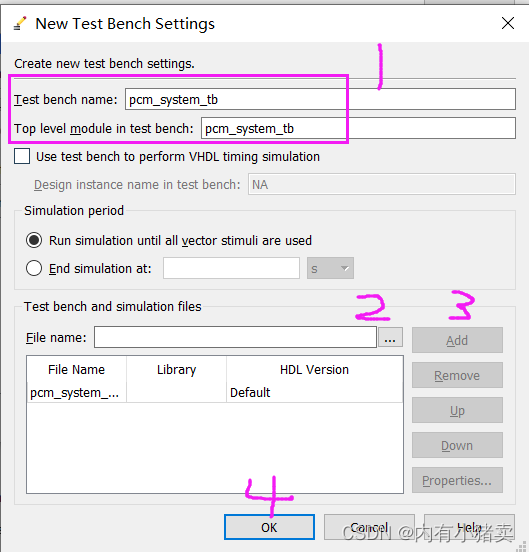

下图紫色框1中”Test bench name“和”Top level module in test bench“命名和tb文件名要一致,这个名字也是tb文件里module的名字,之后依次点击加载tb文件,后面3个界面连点ok。

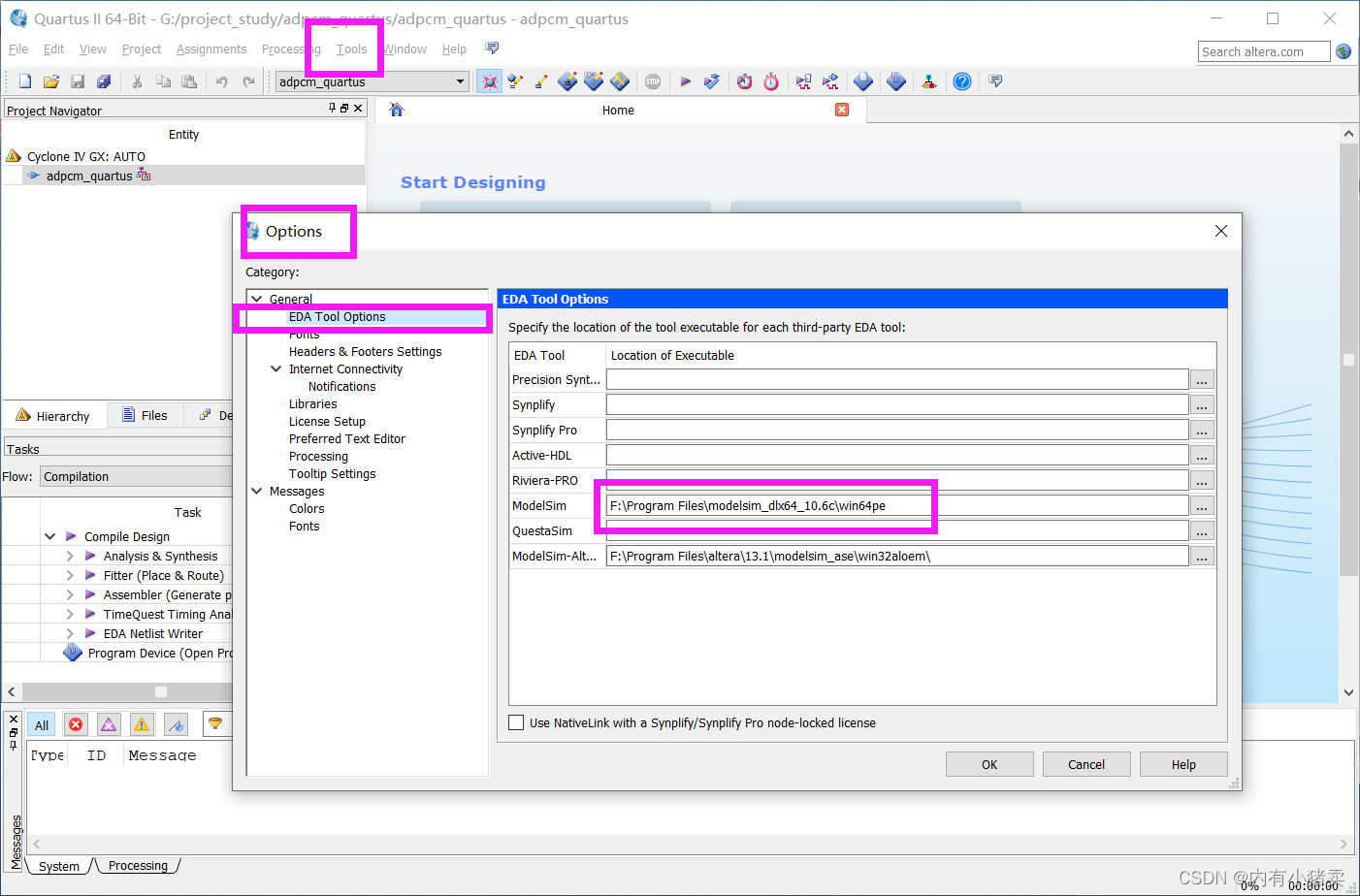

9、配置仿真工具路径

点击tools -> Options -> EDA Tool Options,然后配置Modelsim的启动路径,其他的路径不用管,不影响。

三、编译仿真

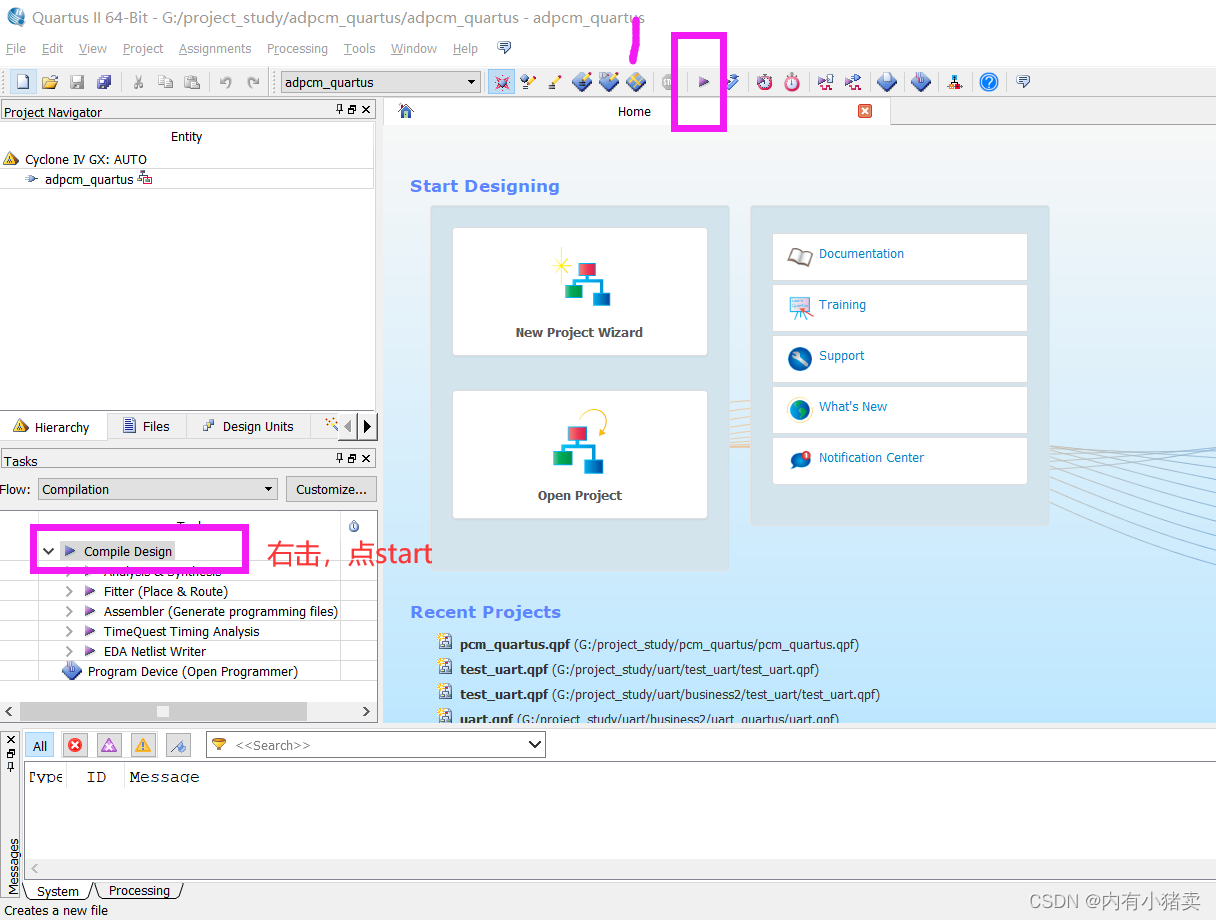

10、编译

下图中2个操作任意一个都可以编译。

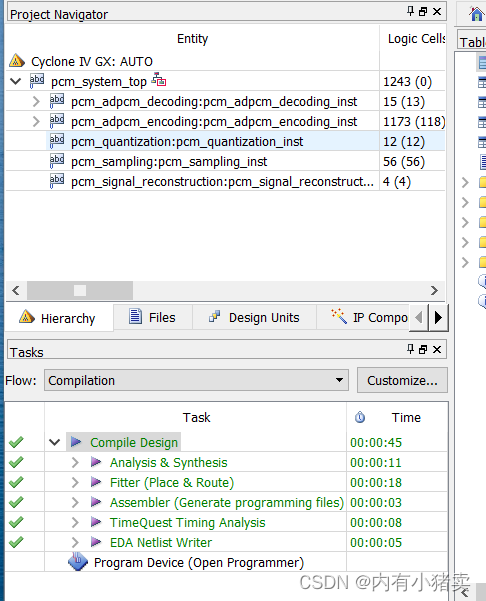

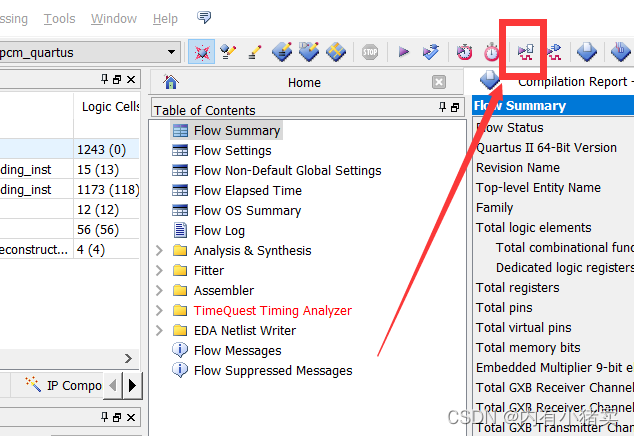

编译好的结果如下:

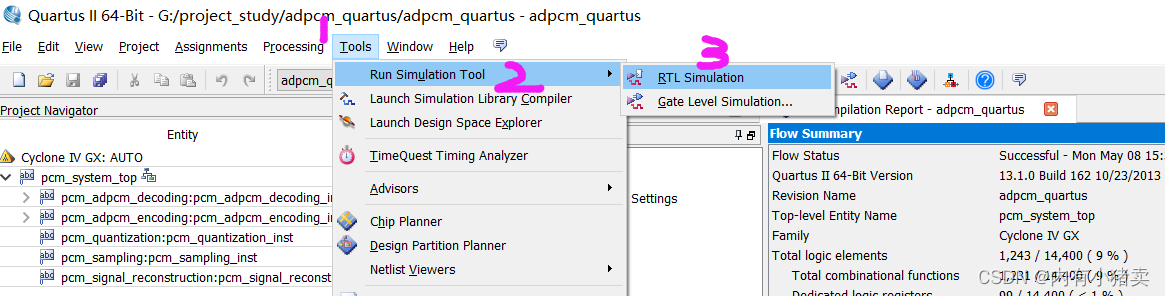

11、仿真

方法1:

方法2:(推荐!)

然后弹出modelsim界面,

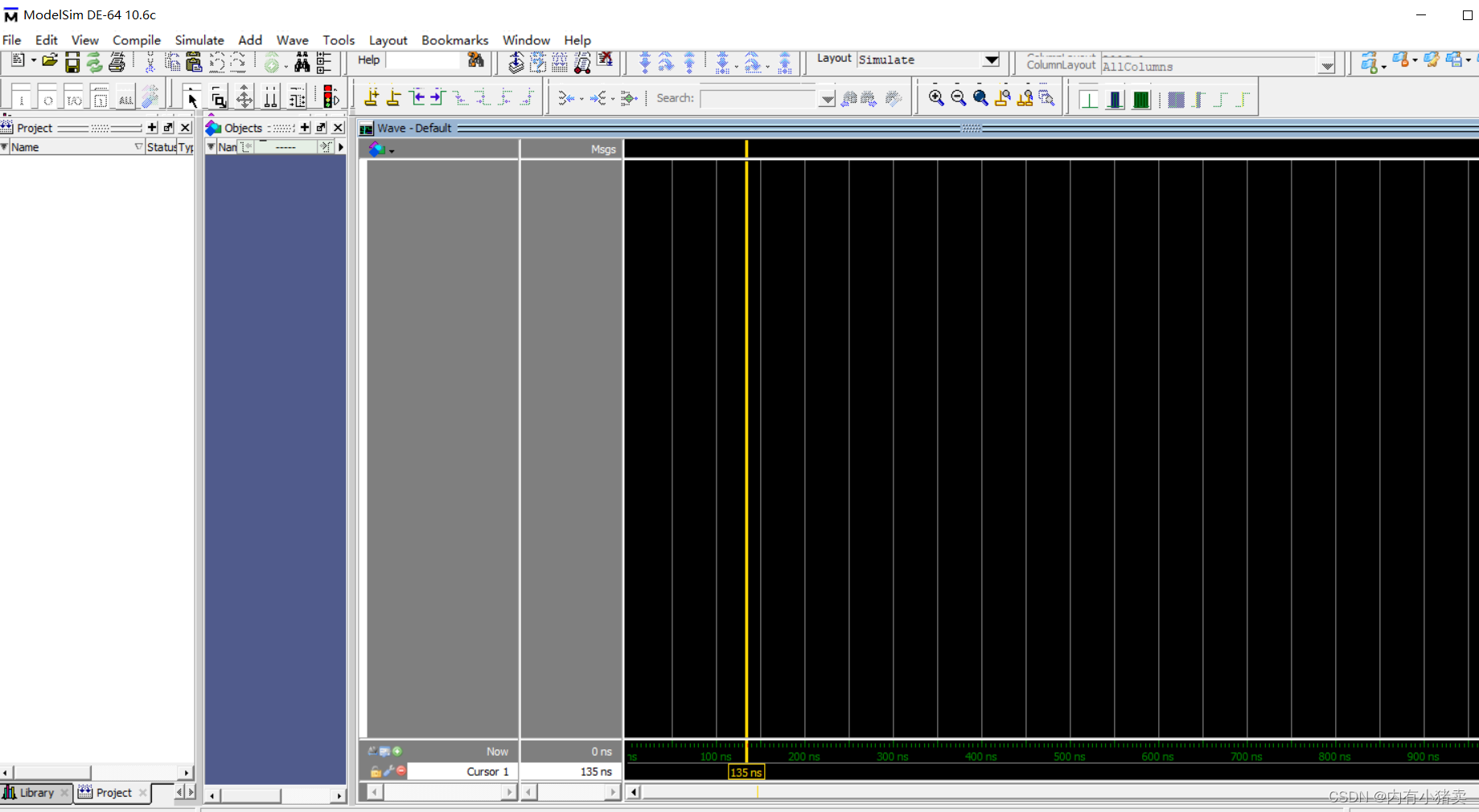

之后弹出空白波形,这时候不要动,等待一会。(注意看左下角会有加载的信息)

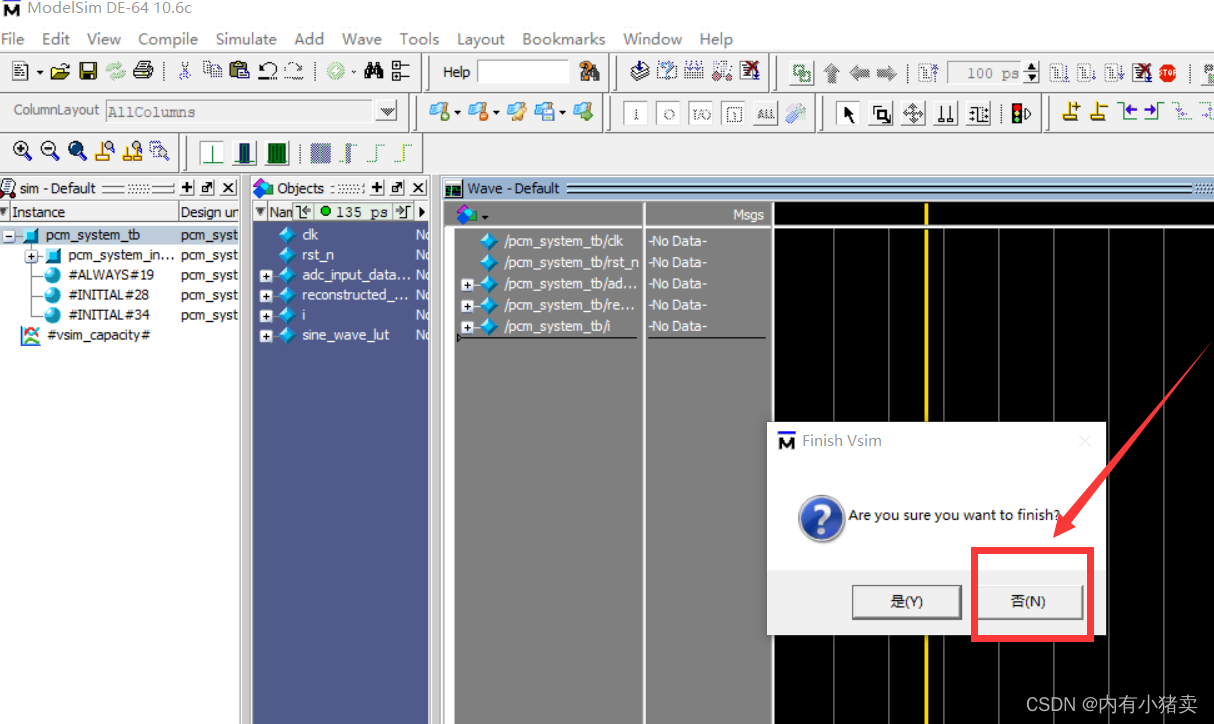

加载波形出来之前会有弹窗,点“否”。

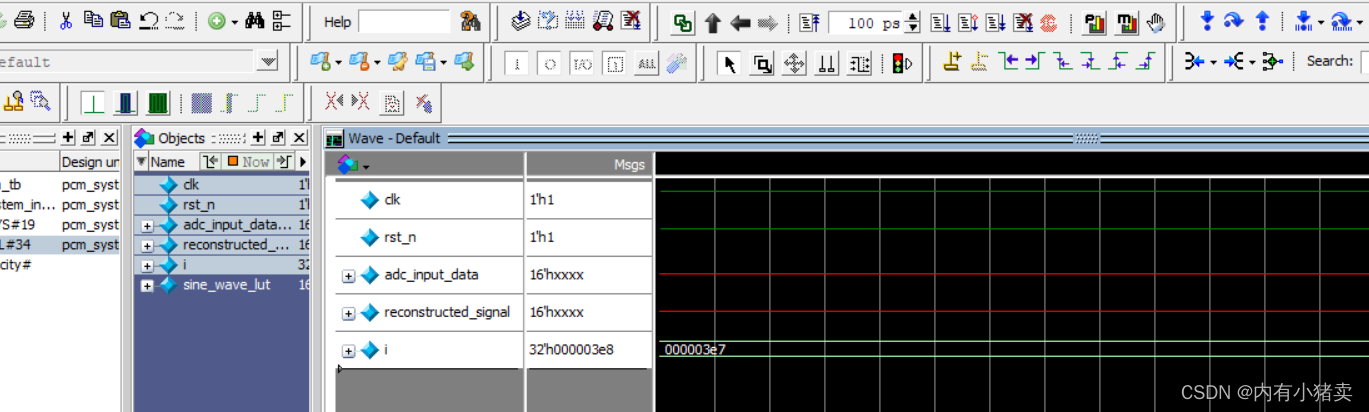

就会加载出来波形,如果波形有红色,说明为读取数据为x态。查看仿真文件中读取路径是否正确。

我们修改路径后,再次测试看波形。

12、正弦波形配置

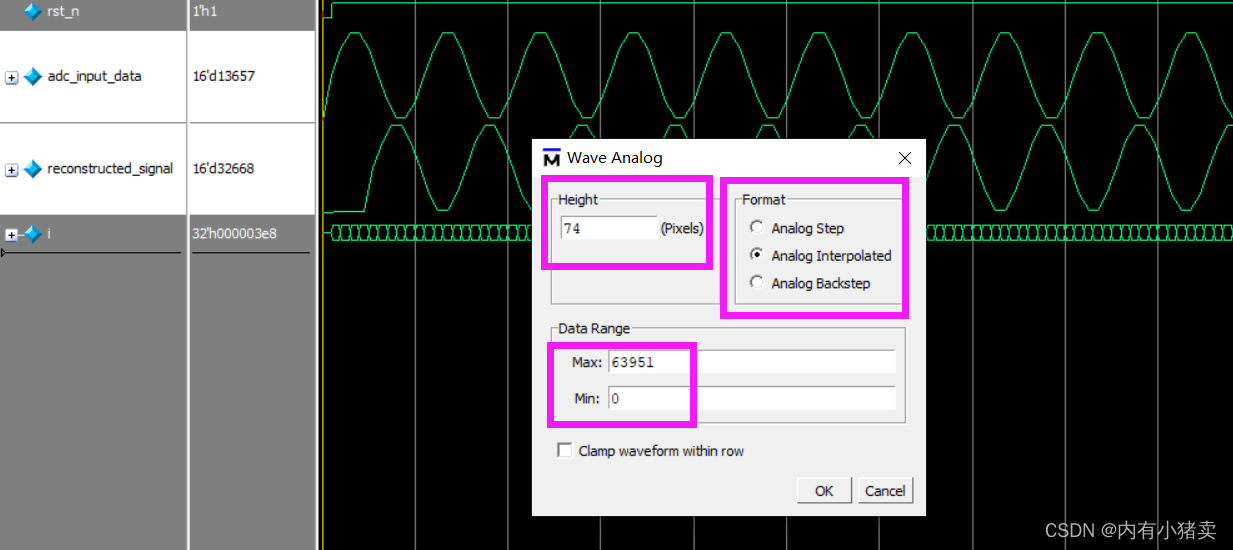

12.1 Radix配置

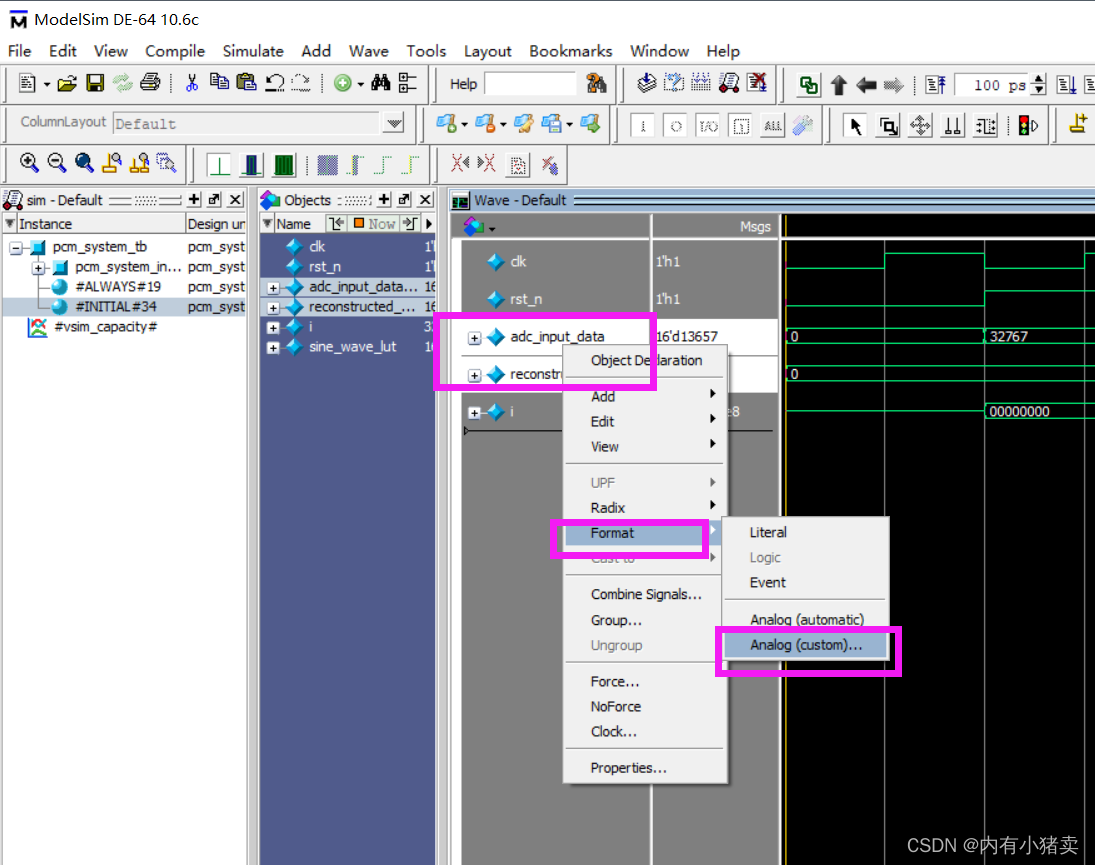

12.2 Format配置

参考文献:

FPGA学习笔记---Modelsim使用技巧总结_modelsim波形高度_嵌入式@hxydj的博客-CSDN博客

Quartus同Modelsim的联合仿真_quartus和modelsim联合仿真_1个程序源的博客-CSDN博客

![K8S管理系统项目实战[前端开发]-1](https://img-blog.csdnimg.cn/4c1121bf152d4b7285376480f4e2a850.png)