1 VCS介绍

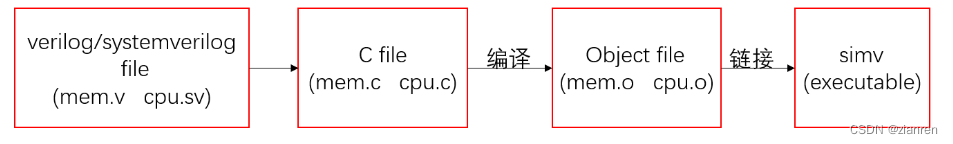

VCS的功能可以大致分为两个大类:编译和仿真。

VCS编译的过程,就是经过一系列的操作,将verilog代码转换为可执行文件(.svim),接下来就是用dve进行仿真过程生成.vpd波形文件。

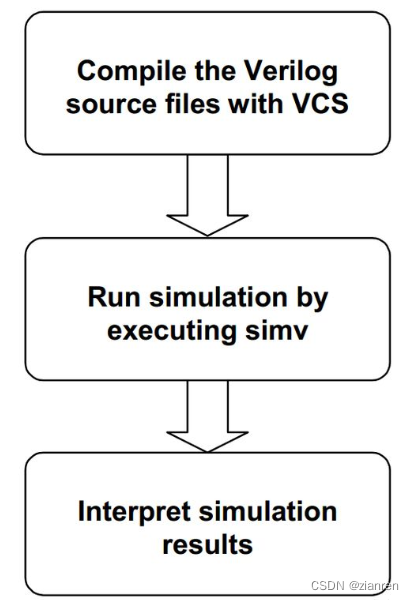

VCS是编译型verilog仿真器,处理verilog的源码过程如下:

VCS先将verilog/systemverilog文件转化为C文件,在linux下编译链接生成可执行文件,在linux下运行simv即可得到仿真结果。

VCS使用步骤,先编译verilog源码,再运行可执行文件:

编译命令的格式:vcs sourcefile [compile_time_option] (编译选项用来控制编译过程)

执行仿真命令格式:./simv [run_time_option]

传入命令参数时,一般 -为供工具直接解析的命令,+为供代码使用的命令,如 +define +indir +plusars。

带-号的,一般是编译时用的,编译工具自带的。

带+号的,一般是插件,环境,验证语言等加的,可扩展、自定义的。

2 VCS编译命令

命令格式为: vcs source_files switch_command

vcs 是启动VCS软件的命令,

source_files 可以扩一些需要编译文件例如:用户自定义的.v文件-testbench文件,用户自定义的DUT文件。

switch_command: 用于控制VCS编译源文件,对于优化性能有着关键性的作用。

可以将VCS工具的帮助文档重定向到一个文件中,方便我们查阅某个命令。

如:重定向帮助文档到vcs.help文件的命令如下:

vcs -full64 -help > help.vcs

然后使用gvim打开help.vcs文件,如果需要查阅某个关键字,可以直接使用/搜索。

脚本使用

-help:vcs帮助,有各编译选项意义;

-full64:以64位模式编译设计并创建64位可执行文件用于64位模式下的模拟;

-sverilog 支持systemverilog语法

工艺库可选项

vcs -v asic.v 在RTL中引用了一些module,如果从当前目录中找不到,就在asic.v中找。

-v lib_file :lib_file(工艺库名字) RTL代码里涉及到工艺库

vcs -y /usr/ 让vcs在目录中找module。在RTL中注明具体module的位置:`uselib directory = /usr/。在编译时,同时碰到-y和`uselib,以uselib为主。

-y lib_dir :告诉vcs到哪里找这个工艺库

+libext+lib_ext:当用到很多库,代替-v

vcs +libext+.bb+.v 在-y注明的文件夹中搜索.bb文件和.v作为module的来源。

vcs +incdir+inc_dir,在RTL中写了`include的话,使用这个命令告诉vcs包含文件的位置。“-incdir”用在库文件中,用来声明逻辑库.verilog代码里面写`include “filename.vh”

-debug_pp:允许转储到VPD并使用UCLI命令和DVE;

-debug:启用UCLI命令和DVE;

-debug_all:启用UCLI命令和DVE,也使线路步进;

-debug_acc+pp+fsdb -kdb -lca

debug_access

-debug_access同-debug_acc 。

VCS 2014 后加入了debug_access, 之前的-debug_pp, -debug, -debug_all不在建议使用。

为了更好的平衡仿真速度和debug功能,建议 配合-debug_region 使用,提供更精准的仿真控制。

vcs -debug_access 时,不需要再手动配置PLI的tab file verdi.tab 和静态库 pli.a,只需设置 $VERDI_HOME,vcs会自动查找所需文件,$fsdbDumpfile可以直接使用。

ibmap libmap

-top lib_cfg

**vcs WORK.tb_top指定elaboration从我们的默认库WORK的最顶层module tb_top开始。也可以写成vcs -top tb_top

https://blog.csdn.net/Holden_Liu/article/details/113761585**

-ignore unique_checks

-Ignore <keyword_argument>

- unique_checks priority_checks all

屏蔽SV中unique/priority型的if或case语句的告警信息,参数包括:unique_checks、priority_checks、all。

SV中priority case 和unique case的区别

https://zhuanlan.zhihu.com/p/477933396

+nospecify: 屏蔽specify块中的路径延时和时序检查

+notimingcheck:屏蔽specify块中的时序检查

define 一个宏

+define +<macro_name>= :macro_name 宏名;value 初始化值; 如+define+INCR_COUNTER

+define+VCS:定义全局的VCS,编译器在编译时如果源文件有类似`ifdef VCS等字样,那么会执行定义之后的代码。

-lca:vcs参数,表示使用vcs“用户限制使用”功能,即vcs提供的一些功能,但该功能还未经过充分验证。因为VCS 2008.9版本在做覆盖率的时候,是一种license受限的功能。加上-lca就行了。limited custom available. Synopsys的一些功能处于试用期,只有有限的客户可以使用,需要特别的license。

-cm < option>:指定覆盖率的类型,包括:line、cond、fsm、tgl、path、branch和assert

-cm_count:在统计是否覆盖的基础上,进一步统计覆盖的次数

-cm_dir < directory_path_name>:指定覆盖率统计结果的存放路径,默认是simv.cm

-cm_hier < filename>:指定覆盖率统计的范围,可以指定是module名、层次名和源文件等

-cm_log < filename>:指定保存覆盖率结果的文本文件的名称|

-cm obc:使能可观察覆盖率的编译

-comp64:在64-bit模式下编译设计,生成64-bit的可执行文件用于64-bit模式仿真

-f file :当有很多源代码时,将这些源代码整合到file里

VCS命令

vcs -licqueue 告诉VCS,当没有license时等待。

vcs -h 列出最常用的vcs编译和runtime选项

vcs -doc 在网页上显示vcs文档

vcs -ID 显示本机的一些信息以及VCS的版本信息

Vcs -Mupdate (增量编译):就是如果有很多个文件需要去验证和仿真,但是只有其中的几个文件需要修改,重新执行很费时间,这就是就可以使用他进行编译,可以避免重复编译

VCS -R 自动执行仿真,可实现编译仿真一体化。编译后立即运行,即编译完成后立即执行 ./simv

VCS -gui 进入图形界面,

Vcs -l 文件名,可以记录日志文件。例如 vcs -l complie.log

Vcs -sverilog 支持systemverilog语法。

Vcs -v2k 兼容verilog 2001以前的标准

Vcs -v lib_file 加入工艺库文件

Vcs -y lib_dir,在特定的路径中寻找工艺库文件。

Vcs -f file 可以用于添加文件目录表,指定一个文件,其中包含源文件和编译时选项的路径名列表;。

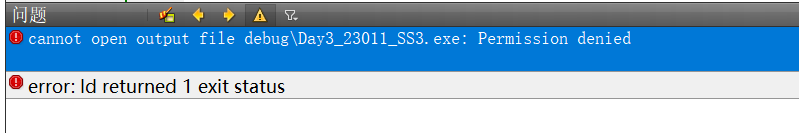

vcs -o flie_name 可以用该文件替代.simv可执行文件。

-debug_all用于产生debug所需的文件。

-Mupdate 源文件有修改时,只重新编译有改动的.v文件,节约编译时间。

-timescale=<time_unit>/<time_precision> 设置仿真精度

-o simv_file 编译默认产生的可执行文件为simv,可以使用 -o 更改可执行文件名。

(9)控制消息打印

vcs -notice,显示诊断消息

vcs -q,让vcs编译时进入“安静模式”

vcs -V,让vcs编译时进入“啰嗦模式”,verbose

vcs -l a.log,产生a.log文件。如果连-R共用,则编译内容和仿真内容都会显示在a.log中。

vcs +warn=noRWSI,编译时不打印warning信息

vcs +warn=noTFIPC,报告所有的warning,除了有关TFIPC的. TFIP和RWSI都是某种错误类型。

vcs +warn=all,报告所有的warning

vcs +warn=TFIPC:2 a.v,只显示关于a.v的TFIPC warning的前2个。

vcs -error=TFIPC,将TFIPC的错误爆出来

vcs +lint 报告lint消息。

vcs -suppress ,和vcs -q差不多,都是抑制消息用的。比如:vcs -suppress=warn

(10)在生成的simv中加入调试选项:

vcs -debug 或 -debug_all,其实-debug_pp不行。

debug模式可支持DVE, ucli, PLIs.

debug_pp是后处理模式(post-process)下的推荐选项。此模式也支持SVA,支持“时间断点”和“值断点”,但不支持“行断点”和“事件断点”。

debug功能与debug_pp一致,跑得更慢。

debug_all,允许逐行执行。

-vpi:允许使用vpi PLI访问例程;

-cpp:使用c++编译器;

-debug_pp:允许转储到VPD并使用UCLI命令和DVE;

-debug:启用UCLI命令和DVE;

-debug_all:启用UCLI命令和DVE,也使线路步进;

-notice:启用详细的诊断消息;

+lint=[no]ID|none|all,… 使能或者禁用verilog的lint消息;

+rad:对设计进行辐射技术优化;

+vcs+lic+wait:如果没有可用的通知,则告诉VCS等待网络许可证;

-o :指定输出可执行文件的文件名,默认为 simv, 如 -o my_simv;

-R:该选项告诉VCS在编译完后直接运行可执行程序,若没有该选项,那么vcs在编译后直接退出;

-l :(小写字母L)如果包含-R,-RI或-RIG选项,则指定VCS记录编译消息和运行时消息的日志文件;

-Mupdate[=0]:默认情况下,VCS会在编译之间覆盖Makefile。 如果希望在编译之间保存Makefile,请输入此内容选项与0参数。输入不带0参数的参数,指定默认情况下,增量编译和更新Makefile文件;

-CFLAGS :将选项传递给C编译器,允许多个-CFLAGS,允许传递C编译器优化级别。

-ucli:在运行时指定UCLI模式;

+incdir+:指定包含使用`include 编译器指令指定的文件的目录,可以指定多个目录,用+字符分隔每个路径名称;

+libext+:指定VCS仅在具有指定扩展名的Verilog库目录中搜索源文件,可以指定多个扩展名,用+字符分隔每个扩展名。例如+libext++.v指定搜索没有扩展名和库扩展名为.v的库文件。 输入-y选项时输入此选项。

+systemverilogext+:指定包含SystemVerilog源代码的源文件的文件扩展名;

-gui[=<dve|verdi>]:启动用户指定的图形用户界面,如果未提供参数,则在检测到有效的VCS_HOME环境变量时,VCS将启动Verdi。 否则DVE将默认启动;

-vcd :将输出VCD文件名设置为指定文件。默认文件名为verilog.dump。Verilog源代码中的$dumpfile系统任务将覆盖此选项;

-verdi:使用verdi图形界面;

+vcdfile+:指定想要用于后期处理的VCD文件;

-vpd_file :在运行时,定义VCS写入的VPD文件的替代名称,而不是缺省名称vcdplus.vpd;

+vcs+vcdpluson:编译选项,加入后会使能产生vpd文件,默认文件名vcdplus.vpd

3 VCS仿真命令

在进过编译操作后会发现目录下会有一个simv 可执行文件,这就就是仿真文件。

所以在命令行直接执行此文件就可以开启仿真。

仿真:编译后产生simv可执行文件。仿真用simv文件,分为2种仿真方式:

(1)交互模式:dve,ucli

(2)batch模式:直接执行simv即可

./simv

执行

$simv[run_tiime_options]

例如 ./sim -gui & (./指在当前文件,sim指编译得到的可执行文件,gui指打开vcs的gui界面-dve,&指后台执行)将会得到执行的PID值

-s 结束仿真时间

$plusargs() 动态接收参数

-E echo

-l logfile 把仿真信息写入logfile文件里

合并覆盖率文件

urg -full64 -dir ${db_file} -dbname ${path}/merged.vdb

将path目录下多个simv*.vdb下面的多个覆盖率文件merge成一个叫merge.vdb的文件

vcs/urg 进行覆盖率coverage merge及部分merge到整体: http://t.csdn.cn/0xtBl

vcs之urg脚本详解 http://t.csdn.cn/JbB44

4 dve查看波形

使用./simv -gui 命令打开图形化界面DVE,选中所有信号 --> 右键Add to Waves --> New Wave View

filelist 是包含其他仿真参数以及整个工程的文件列表,文件格式如下;

filelist 中的注释使用verilog中的 “//” 与 "/…/ "。

// compile options.

+v2k

-sverilog

-ntb_opts uvm-1.1 // 注意: 此编译命令只能使用-file选项指定的文件中

-timescale=1ns/10ps

// source file path.

+incdir+./src

+incdir+./test

// source files.

./src/demo.svh

./src/demo.sv

./test/tb_top.sv

https://blog.csdn.net/paultianke/article/details/103022656

https://ac.nowcoder.com/discuss/961531?type=0&order=3&pos=19&page=0&channel=-1&source_id=discuss_center_0_nctrack

https://blog.csdn.net/weixin_42640948/article/details/123185063

https://zhuanlan.zhihu.com/p/557078736

https://blog.csdn.net/weixin_45270982/article/details/104015733

逻辑仿真工具VCS的使用-Makefile

http://t.csdn.cn/WPJrt

Ubuntu下VCS安装记录

https://blog.csdn.net/Chi_Hong/article/details/86298048

Linux系统中VCS、Dve & Verdi的使用

https://blog.csdn.net/a_weiming/article/details/90741174

VCS常用仿真选项开关及步骤总结

https://blog.csdn.net/qq_41394155/article/details/81486760

IC-工具篇–VCS使用教程-卷一(20200328)

http://t.csdn.cn/CQgSh

VCS-bilibili教程篇1-Simulation Basics

https://blog.csdn.net/ciscomonkey/article/details/112253351

参考资料:

1.VCS User Guide

2. VCS labs

3. bilibili搜索VCS,有一些视频教程。

1是官方手册,

2是官方给出的几个实验,包涵源码和实验指导文档。

1, 2 均可在eetop上找到并下载。

VCS工具的安装是一个很头疼的事情。本人最开始查阅各种博客,花了两天时间才捣鼓好双系统,在Ubuntu上安装完VCS。到后来发现eetop上有人分享安装完各种EDA的Redhat系统,十分方便。有需要的同学可以去下载。 http://bbs.eetop.cn/thread-876507-1-1.html

12月15更新:上面我分享的虚拟机不知道怎么回事就挂了,现在推荐大家用 docker,和虚拟机一样用,放个贝塔的文章链接:

空白的贝塔君:Synopsys全套docker镜像使用指南zhuanlan.zhihu.com [https://zhuanlan.zhihu.com/p/266225644]

在linux下使用EDA需要有linux基础,ls,pwd,cd, touch等基本命令需要会用。还有vim编辑器的简单使用,b站上有许多教程。

https://www.bilibili.com/video/BV1ex411x7Em/?spm_id_from=333.788.videocard.0www.bilibili.com

https://www.bilibili.com/video/BV1Yt411X7mu?from=search&seid=77456085189****0211www.bilibili.com

第一个链接里的内容,挑前面讲Linux命令的看看即可。