每当信号遇到阻抗变化,就会出现反射现象,反射对信号质量影响很大。信号完整性工作最重要的部分之一就是预测不连续点对信号的影响,以及设计工程可接受的备选方案。

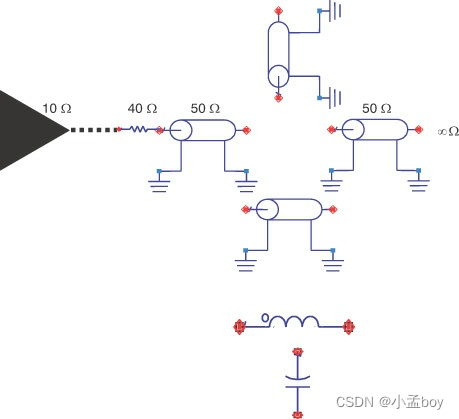

尽管电路板在设计上是可控阻抗互连,但是信号在以下结构中仍然会遇到阻抗不连续点:传输线末端、package引线、输入门电容、信号层之间的过孔、拐角、残桩、分支、测点、返回路径空隙、过孔区域的绕线以及交叉等。

在对这些影响建模的时候,我们可以使用三种常见的等效电路模型来电气描述不连续中断:一个理想电容、一个理想电感和一短截理想传输线。

影响不连续信号失真的两个最重要的参数是信号的上升时间和不连续的大小。对于电感器和电容器,它们的瞬时阻抗取决于电流变化或电压变化的瞬时速率以及 C 或 L 的值。

当信号通过元件时,电流和电压的斜率会随时间变化,元件的阻抗也会随时间变化。这意味着反射系数会随着时间变化,尤其是随着上升或下降时间的具体特征而变化。峰值反射电压将与信号的上升时间成比例。

通常,不连续的影响因驱动器的阻抗和影响多次反弹的初始传输线的特性阻抗而变得更加复杂。

这些因素以及不连续性本身的影响只能通过将产生不连续性的物理结构转换为其等效电路模型并执行仿真来充分考虑。经验法则估计只能提供工程洞察力,并为何时可能出现问题提供粗略的指导。

任何阻抗不连续都会引起信号的一些反射和失真。设计完全没有反射的互连并非不可能。我们可以忍受多少干扰,多少干扰太多了?这在很大程度上取决于干扰预算以及为每个干扰源分配了多少干扰电压。

除非另有规定,否则根据粗略的经验,反射噪声电平应保持在电压摆幅的 10% 以下。对于 3.3-v 信号,这是 330 mV 的噪声。一些噪声预算可能更保守,分配给反射噪声的比例不超过 5%。通常,噪声预算越严格,解决方案就越昂贵。通常,分配给一个源的噪声可能会收紧,因为纠正它的修复实施起来成本较低,而另一个可能会放松,因为修复它的成本更高。根据粗略的经验,如果反射噪声接近或超过信号摆幅的 10%,我们绝对应该担心反射噪声。在某些设计中,低于 5% 可能太多了。

通过评估几个简单的案例,我们可以了解哪些物理因素会影响信号失真,以及如何在它们成为问题之前将它们从设计中排除。最终,对设计是否可接受的最终评估必须来自仿真。这就是为什么每个关注信号完整性的执业工程师都可以轻松访问模拟器以评估特定情况如此重要的原因。

什么时候端接?

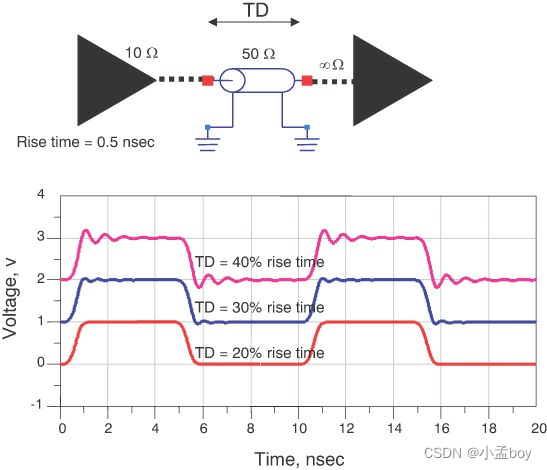

最简单的传输线电路中,一端有一个驱动器,中间是一小段受控阻抗线,末端是接收器。如前面所述,信号会在高阻开路的末端和低阻驱动器之间来回震荡。当传输线很长的时候,这些多重震荡会产生信号质量问题,我们会归入振铃范畴。但是如果传输线足够短,尽管依然会产生反射,但是可能会淹没在上升沿或下降沿中,可能不会产生问题。下图展示了当传输延时从上升时间的20%增加到30%再到40%过程中接收波形的变化。

内部互连的传输延时为0.1ns时,产生的反射每 0.2 纳秒(往返飞行时间)来回振荡一次。如果和上升时间比起来很短,多重震荡将会被上升时间覆盖,几乎看不出来,不会引发潜在问题。粗略估计,当传输时延小于上升时间的20%,反射可以忽略,但如果传输时延大于20%上升时间,振铃就会变得重要起来。

对于一个未端接的传输线,我们可以使用阈值20%来粗略估计是否需要关注振铃噪声,如果传输延时大于上升时间的20%,我们必须要关注振铃问题,如果小于上升时间的20%,振铃噪声可能不是个问题,传输线可以不端接。

举个栗子,如果上升时间是1ns,传输线不用端接的最大时延就是20%*1ns=0.2ns,FR4板材中,信号传输速度是6inch/ns,对应的物理长度就是6inch/ns*0.2ns=1.2inch。我们可以得出一个公式,传输线不用端接的最大长度大概就是:

![]()

其中Lenmax是无需端接的最大传输线长度,RT表示信号的上升时间。

这是一个非常有用且好记的规则:传输线不用端接的最大时延就是信号的上升时间。

如果上升时间为 1 纳秒,则最大未端接长度约为 1 英寸。如果上升时间为 0.1 纳秒,则最大未端接长度为 0.1 英寸。正如我们将看到的,这是确定振铃噪声何时会发挥重要作用的最重要的一般经验法则。这也是为什么信号完整性近年来成为一个重要问题,而在老一代技术中可能已经避免了。

当时钟频率为 10 MHz 时,时钟周期为 100 纳秒,上升时间约为 10 纳秒。最大不端接线为 10 英寸。这比典型主板上的几乎所有走线都长。回到 10 MHz 时钟时代,尽管互连始终表现得像传输线,但反射噪声从未造成问题,并且互连对信号是“透明的”。我们永远不必担心阻抗匹配、端接或传输线效应。

然而,产品的外形尺寸保持不变,互连长度保持不变,但上升时间却在减少。因此,我们不可避免地会达到足够高的时钟频率和足够短的上升时间,以至于电路板上几乎所有的互连都将比最大可能的未端接长度长,端接将很重要。

如今,信号的上升时间短至 0.1 纳秒,在振铃噪声变得重要之前,传输线的最大未端接长度约为 0.1 英寸。几乎 100% 的互连都比这更长。端接策略是当今和未来所有产品的必需品。

点对点拓扑中最常见的端接策略

我们已经验证了振铃的根源是源端和末端的阻抗不连续以及来回的多重反射,如果我们消除至少一端的反射,那就可以减小振铃。

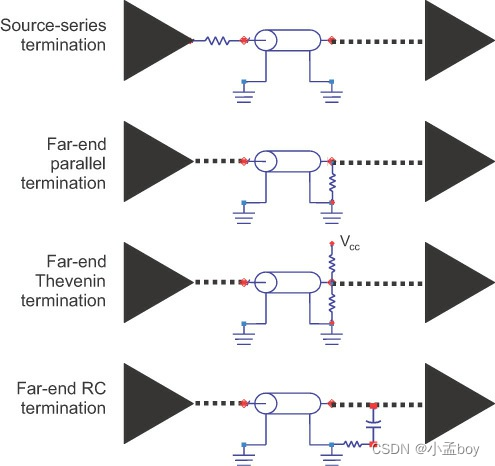

管理传输线一端或两端的阻抗来消除反射称为端接,典型做法是在某一位置放置一个或多个电阻。

一个驱动器驱动一个接收器时,我们称之为点对点拓扑。下图展示了四种点对点拓扑的端接技术。最常见的做法是在驱动器位置串联一个电阻器,这就是源端端接。端接电阻和驱动器的源端阻抗应该添加到传输线的特性阻抗里。

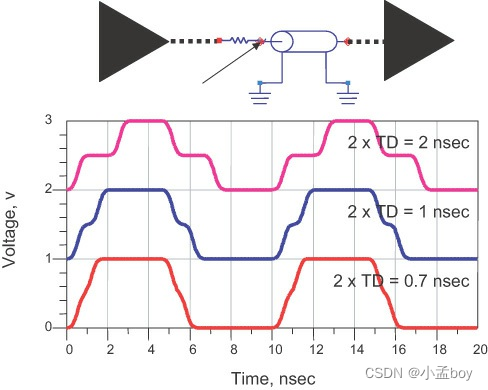

如果驱动器源端阻抗是10Ohm,传输线的特性阻抗是50Ohm,那么端接电阻应该是40Ohm,从驱动器出来的1V信号会遇到由50欧姆总电阻和50欧姆传输线组成的分压器,这样,0.5V的电压将会加载到传输线上。

猛一瞅,一半的电压似乎并不足以影响任何触发,然而,当0.5V的电压抵达传输线的末端开路,又会遇到阻抗不连续,开路反射比率为1,0.5V的输入信号就会以同样幅度反射回源端。在末端,开路端接的电压应该是0.5V输入电压加上0.5V反射电压,一共是1V。

0.5V的反射信号返回源端后,在串联端接电阻位置,信号感知到的阻抗就是40Ohm的端接阻抗加上10Ohm的源端阻抗,共50Ohm,仍然相当于是50Ohm的传输线,因此,信号将不会感知到阻抗变化,也不会有反射,信号仅仅被端接电阻和源端电阻吸收。

在末端,我们只看到1V的信号,并没有振铃。

在传输线近端,就是从源端出来经过端接电阻之后,我们测试的初始电压就是输入到传输线的电压,就是一半的信号电压。往源端看,必须等待反射波形到达,使得总的电压达到全电压摆动。

对于等于往返传输时间的时间,源端的电压,在串联电阻器之后,将遇到搁置。与上升时间相比,传输线的往返时间延迟越长,搁置将持续的时间越长,反映到波形上就是台阶。这是源系列端接线路的基本特征。下图 显示了源端测量电压的示例。

只要靠近源端的位置没有其他接收器可以感知到台阶,就不会造成问题,如果需要在靠近源端位置连接其他设备,就需要另外的拓扑或者端接来避免台阶造成的问题。