1、About Clocks

在数字设计中,时钟代表了从寄存器到寄存器可靠传输数据的时间基准。Xilinx®Vivado®集成设计环境(IDE)时序引擎使用时钟特性来计算时序路径要求,并通过松弛计算报告设计时序裕度。必须正确定义时钟,以便以最佳精度获得最大定时路径覆盖范围。

以下特性定义了时钟:

•它定义在其树根的驱动引脚或端口上,称为源点。

•其边沿由周期和波形特性的组合来描述。

•周期以纳秒为单位指定。它对应于波形重复的时间。

•波形是时钟周期内上升沿和下降沿绝对时间的列表,单位为纳秒。该列表必须包含偶数个值。第一个值总是对应于第一个上升沿。除非另有规定,否则占空比默认为50%,相移默认为0ns。

1.1、Propagated Clocks(传播的时钟)

周期和波形特性代表时钟的理想特性。当进入FPGA并通过时钟树传播时,时钟边沿被延迟,并受到噪声和硬件行为引起的变化的影响。这些特性被称为时钟网络延迟和时钟不确定性。

时钟不确定性包括:

•时钟抖动(请参阅Clock Jitter)

•相位误差

•您指定的任何额外不确定性(请参阅Additional Clock Uncertainty)

默认情况下,Vivado IDE总是将时钟视为传播时钟,即非理想时钟,以便提供准确的slack,其中包括时钟树插入延迟和不确定性。

1.2、Dedicated Hardware Resources(专用硬件资源)

Xilinx FPGA的专用硬件资源有效地支持大量的设计时钟。这些时钟通常由板上的外部组件生成。它们通常通过输入端口进入设备。它们也可以由称为时钟修改块的特殊基元生成,例如:

• MMCM

• PLL

• BUFR

它们也可以通过诸如LUT和寄存器之类的常规单元进行转换。以下部分介绍了如何根据时钟的来源来最好地定义时钟。

2、Primary Clocks(主时钟)

主时钟是通过输入端口或千兆收发器输出引脚进入设计的板时钟(例如,恢复时钟)。主时钟只能通过create_clock命令来定义。

注意:只有Xilinx 7系列FPGA才能在千兆收发器输出上定义主时钟。对于UltraScale™ 和UltraScale+™ 计时器自动导出GT输出端口上的时钟。

主时钟必须附加到网表对象。此网表对象表示设计中的点,所有时钟边沿都源自该点并在时钟树上向下游传播。换句话说,主时钟的源点定义了Vivado IDE在计算slack方程中使用的时钟延迟和不确定性时使用的时间零点。

Vivado IDE忽略来自位于主时钟定义点上游的单元的所有时钟树延迟。如果在设计过程中在管脚上定义主时钟,则其延迟的一部分将用于时序分析。如果该时钟与设计中的其他相关时钟通信,这可能是一个问题,因为时钟之间的偏斜以及因此产生的slack值可能是不准确的。

必须首先定义主时钟,因为其他时序约束通常会引用它们。

2.1、Primary Clocks Examples

2.1.1、普通时钟

如下图所示,板时钟通过端口sysclk进入设备,然后通过输入缓冲器和时钟缓冲器传播,然后到达路径寄存器。

•其周期为10 ns。

•其占空比为50%。

•其相位没有偏移。

建议:在输入端口上定义板时钟,而不是在时钟缓冲器的输出上。

相应的Xilinx设计约束(XDC):

create_clock -period 10 [get_ports sysclk] 2.1.2、相位偏移时钟

与sysclk类似,板时钟devclk通过端口ClkIn进入设备。

•其周期为10 ns。

•其占空比为25%。

•相位偏移90度。

对应的XDC:

create_clock -name devclk -period 10 -waveform {2.5 5} [get_ports ClkIn]2.1.3、通过MMCM的时钟

下图显示了一个收发器gt0,它从板上的高速链路恢复时钟rxclk。时钟rxclk具有3.33ns的周期,50%的占空比,并且被路由到MMCM,它为设计生成几个补偿时钟。当在GT0的输出驱动引脚上定义rxclk时,由MMCM驱动的所有生成的时钟都有一个公共源点,即GT0/RXOUTCLK。

它们之间的路径上的slack计算使用适当的时钟延迟和不确定性值。

create_clock -name rxclk -period 3.33 [get_pins gt0/RXOUTCLK]

2.1.4、差分时钟

在下图中,差分缓冲器驱动PLL。在这种情况下,主时钟必须仅在差分缓冲器的正输入上创建。在缓冲器的每个正/负输入上创建主时钟将导致不切实际的CDC路径。例如:

create_clock -name sysclk -period 3.33 [get_ports SYS_CLK_clk_p]

2.3、Virtual Clocks

虚拟时钟是指在设计中没有物理连接到任何网表元素的时钟。虚拟时钟是通过create_clock命令定义的,而不指定源对象。在以下情况之一中,虚拟时钟通常用于指定输入和输出延迟约束:

•外部设备I/O参考时钟不是设计时钟之一。

•FPGA输入/输出路径与内部生成的时钟有关,该时钟无法根据其派生的板时钟正确计时。

注意:当两个周期之间的比率不是整数时,就会发生这种情况。这导致了非常紧凑和不切实际的时序路径要求。

•希望仅为与I/O延迟限制相关的时钟指定不同的抖动和延迟,而不修改内部时钟特性。

例如,时钟clk_virt的周期为10ns,并且不附加到任何网表对象。未指定[<objects>]参数。在这种情况下,-name选项是强制性的。

create_clock -name clk_virt -period 10在被输入和输出延迟约束使用之前,必须定义虚拟时钟。

2.4、Generated Clocks(生成的时钟)

生成的时钟在设计内部由称为时钟修改块的特殊单元(例如,MMCM)或一些用户逻辑驱动。生成的时钟与主时钟相关联。create_generated_clock命令考虑主时钟的起始点。主时钟可以是主时钟或另一个生成的时钟。生成的时钟特性直接从其主时钟派生而来。您必须描述修改电路如何转换主时钟,而不是指定它们的周期或波形。

主时钟和生成的时钟之间的关系可以是以下任意一种:

•简单的分频

•简单的倍频

•倍频和分频的组合,以获得非整数比(通常由MMCM和PLL完成)

•相移或波形反转

•占空比转换

•以上所有内容的组合

建议:首先定义所有主时钟。它们是定义生成的时钟所必需的。

注:为了计算生成时钟的延迟,该工具跟踪生成时钟的源引脚和主时钟的源极引脚之间的时序和组合路径。在某些情况下,可能希望仅通过组合路径进行跟踪,以计算生成的时钟延迟。您可以使用-combinational命令行选项来完成此操作。

2.4.1、用户定义的生成时钟(User Defined Generated Clocks)

用户定义的生成时钟是:

•由create_generated_clock命令定义。

•连接到网表对象,最好是时钟树根引脚。

使用-source选项指定主时钟。这表示设计中的引脚或端口,主时钟通过该引脚或端口传播。通常使用主时钟源点或生成的时钟源单元的输入时钟引脚。

注意:-source选项只接受一个pin或端口网表对象。它不接受时钟对象。

2.4.1.1、Example One: Simple Division by 2

主时钟clkin具有10ns的周期。它被驱动其他寄存器时钟引脚的寄存器REGA除以2。相应生成的时钟称为clkdiv2。以下提供了两个等效的约束条件:

create_clock -name clkin -period 10 [get_ports clkin]

# Option 1: master clock source is the primary clock source point

create_generated_clock -name clkdiv2 -source [get_ports clkin] -divide_by 2

\[get_pins REGA/Q]

# Option 2: master clock source is the REGA clock pin

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -divide_by 2

\ [get_pins REGA/Q]

2.3.1.2、Example Two: Division by 2 With the -edges Option

可以使用-edges选项来直接描述基于主时钟边缘生成的时钟的波形,而不是使用-divide_by选项。自变量是主时钟边缘索引的列表,用于定义生成的时钟边缘的时间位置,从上升时钟边沿开始。以下示例等效于中定义的生成时钟

Example One: SimpleDivision by 2.

# waveform specified with -edges instead of -divide_by

create_generated_clock -name clkdiv2 -source [get_pins REGA/C] -edges {1 3

5} \ [get_pins REGA/Q] 2.4.1.3、:带-edges和-edge_shift选项的占空比变化和相移

通过使用-edge_shift选项,生成的时钟波形的每个边沿也可以单独偏移正值或负值。仅当需要相移时才使用此选项。-edge_shift选项不能与以下任何选项同时使用:

• -divide_by

• -multiply_by

• -invert

考虑具有10ns周期和50%占空比的主时钟clkin。它到达单元mmcm0,该单元生成一个占空比为25%、偏移90度的时钟。生成的时钟定义指的是主时钟边沿1、2和3。这些边沿分别出现在0ns、5ns和10ns处。为了获得所需的波形,将第一边沿和第三边沿偏移2.5ns。

create_clock -name clkin -period 10 [get_ports clkin]

create_generated_clock -name clkshift -source [get_pins mmcm0/CLKIN] -edges

{1 2 3} \

-edge_shift {2.5 0 2.5} [get_pins mmcm0/CLKOUT] # First rising edge: 0ns

+ 2.5ns = 2.5ns

# Falling edge: 5ns + 0ns = 5ns

# Second rising edge: 10ns + 2.5ns = 12.5ns注意:-edge_shift值可以是正的,也可以是负的。

Example Three: Duty Cycle Change and Phase Shift with -edges and -edge_shift Options

2.4.1.4、Example Four: Using Both -divide_by and -multiply_by at the Same Time(同时使用-divide_by和-multiply_by)

Vivado IDE允许您同时指定-divide_by和-multiply_by。这是对标准Synopsys设计约束(SDC)支持的扩展。这对于手动定义MMCM或PLL实例生成的时钟特别方便,尽管Xilinx建议让引擎自动创建这些约束。有关详细信息,请参见 Automatically Derived Clocks。

考虑上面示例三中的mmcm0单元:具有-edges和-edge_shift选项的占空比变化和相移,并假设它将主时钟的频率乘以4/3。相应生成的时钟定义为:

create_generated_clock -name clk43 -source [get_pins mmcm0/CLKIN] -

multiply_by 4 \

-divide_by 3 [get_pins mmcm0/CLKOUT]如果在MMCM或PLL的输出上创建生成的时钟约束,最好验证波形定义是否与MMCM或锁相环的配置匹配。

2.4.1.5、Example Five: Tracing the Master Clock through Combinational Arcs Only(仅通过组合弧跟踪主时钟)

在该示例中,假设主时钟驱动基于寄存器的二分频时钟和时钟复用器两者,时钟复用器可以从寄存器时钟分频器中选择主时钟或二分频时钟。在这种情况下,从主时钟到生成的时钟有两条路径,分别是通过时序弧和组合弧。您希望在多路复用器输出上创建一个生成的时钟,反映从主时钟到多路复用器的组合路径的延迟。这是通过使用-combinational命令行选项来完成的:

create_generated_clock -name clkout -source [get_pins mmcm0/CLKIN] -

combinational [get_pins MUX/O]2.4.1.6、Example Six: Forwarded Clock Driven by ODDR

在本例中,在ODDR单元驱动的输出端口上创建转发时钟。转发时钟参考驱动ODDR/CLKDIV引脚的主时钟,并且具有与主时钟相同的周期(-divide_by 1):

create_generated_clock -name ck_vsf_clk_2 \

-source [get_pins ODDRE1_vsfclk2_inst/CLKDIV] -divide_by 1 [get_ports

vsf_clk_2]

2.4.2、Automatically Derived Clocks(自动派生时钟)

自动派生的时钟也称为自动生成的时钟。Vivado IDE在时钟修改块(CMB)的输出引脚上自动创建这些约束,前提是已经定义了相关的主时钟。在Xilinx 7系列设备系列中,CMB包括:

• MMCM*/ PLL*

• BUFR

• PHASER*

在Xilinx UltraScale中™ 设备系列,CMB是:

• MMCM* / PLL*

• BUFG_GT / BUFGCE_DIV

• GT*_COMMON / GT*_CHANNEL / IBUFDS_GTE3

• BITSLICE_CONTROL / RX*_BITSLICE

• ISERDESE3

如果用户定义的时钟(主时钟或生成时钟)也定义在同一网表对象上,即在同一定义点(网络或引脚)上,则不会创建自动生成时钟。自动派生时钟是用连接到定义点的网络最顶层中的段名称命名的。

2.4.2.1、自动派生始终示例(Automatically Derived Clock Example)

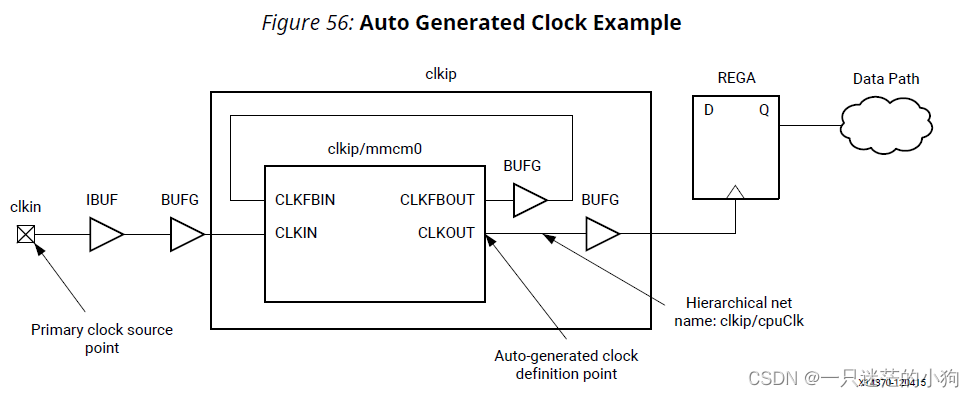

以下自动导出的时钟示例是由MMCM生成的时钟。主时钟clkin驱动MMCME2实例clkip/mmcm0的输入clkin。自动生成的时钟的名称为cpuClk,其定义点为clkip/mmcm0/CLKOUT。

技巧: 使用get_clocks -of_objects <pin/port/net>命令查询自动生成的时钟,而不知道其名称。

这将使您的约束或脚本独立于时钟名称的更改。

2.4.2.2、 Local Net Names(局部网络名称)

如果CMB实例位于设计的层次结构中,则局部网络名称(即没有其父单元名称的名称)将用于生成的时钟名称。(如上面图56,与CLKOUT连接的网络名称是cpuClk,所以生成时钟的名称就是cpuClk)

例如,对于名为clkip/cpuClk的分层网络:

•父单元名称为clkip。

•生成的时钟名称为cpuClk。

2.4.2.3、 Name Conflicts(命名冲突)

如果两个自动生成的时钟之间存在名称冲突,Vivado IDE会添加唯一的后缀来区分它们,例如:

• usrclk

• usrclk_1

• usrclk_2

• ...

要强制生成时钟的名称,请执行以下操作:

•在RTL中选择唯一且相关的网络名称,或

•使用create_generated_clock强制生成时钟的名称。

2.5、重命名自动衍生时钟(Renaming Auto-Derived Clocks)

可以重命名工具自动创建的生成时钟。重命名过程包括使用有限数量的参数调用create_generated_clock命令:

create_generated_clock -name new_name [-source master_pin] [-master_clock

master_clk] source_object 必须指定的参数是新生成的时钟名称和生成的时钟的源对象。生成的时钟的源对象是创建自动派生时钟的对象(用于UltraScale的CMB输出引脚、GT输出引脚等)。只有当多个时钟通过源引脚传播时,才能使用-source和-master参数,以消除任何歧义。

重要提示:如果-edges/-edge_shift/-divide_by/-multiply_by中的任何一个/-combinational/-duty_cycle/-inverse选项被传递给create_generated_clock命令,生成的时钟不会被重命名。取而代之的是创建具有指定特性的新生成的时钟。

重要提示:当一个模块(IP/BD/DFx/…)在上下文之外综合时,当综合顶层并且模块内部引脚和时钟名称不再可访问时,该模块被推断为黑盒。在这种情况下,用于综合的顶级XDC约束不能引用时钟名称,也不能重命名模块内部生成的自动派生时钟。对于OOC综合,顶级时序约束必须指向通过传播这些时钟的模块端口的OOC时钟。这可以使用一些查询来完成,例如'get_clocks-of_objects[get_pins<OOC_MODULE_OUTPUT_CLOCK_PORT>]。用于实现的XDC约束不具有此限制,因为在应用XDC约束之前重建了整个设计。

2.5.1、Limitations

•自动衍生时钟只能在其产生的引脚处重命名,例如在时钟修改块(PLL、MMCM…)的输出处。例如,自动派生的时钟不能在BUFG的输出端重命名,即使它在其中传播。

•主时钟或用户定义生成的时钟不能重命名。只有自动派生的时钟才能使用此机制重命名。

•source_object必须与创建自动派生时钟的对象相匹配。

如果工具无法重命名生成的时钟,则返回错误。在进行重命名时,主时钟也必须存在。自动派生的时钟可以在XDC内的任何时候重命名,即使在它们被一些定时约束引用之后也是如此。

例如,以下是MMCM输出引脚处生成的时钟的report_clocks摘要:

====================================================

Generated Clocks

====================================================

Generated Clock : clkfbout_clk_core

Master Source : clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1 Master

Clock : clk_pin_p

Multiply By : 1

Generated Sources : {clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKFBOUT}

Generated Clock : clk_rx_clk_core

Master Source : clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1 Master

Clock : clk_pin_p

Multiply By : 1

Generated Sources : {clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT0}

Generated Clock : clk_tx_clk_core

Master Source : clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1 Master

Clock : clk_pin_p

Edges : {1 2 3}

Edge Shifts : {0.000 0.500 1.000}

Generated Sources : {clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT1}下面的三个命令说明了必须指定的命令行选项,以重命名MMCM输出端的三个自动派生时钟:

create_generated_clock -name clk_rx [get_pins clk_gen_i0/clk_core_i0/inst/

mmcm_adv_inst/CLKOUT0]

create_generated_clock -name clk_tx [get_pins clk_gen_i0/clk_core_i0/inst/

mmcm_adv_inst/CLKOUT1]

create_generated_clock -name clkfbout [get_pins clk_gen_i0/clk_core_i0/inst/

mmcm_adv_inst/CLKFBOUT]重命名后,以下是report_clocks的摘要:

====================================================

Generated Clocks

====================================================

Generated Clock : clkfbout

Master Source : clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1 Master

Clock : clk_pin_p

Multiply By : 1

Generated Sources : {clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKFBOUT}

Generated Clock : clk_rx

Master Source : clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1 Master

Clock : clk_pin_p

Multiply By : 1

Generated Sources : {clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT0}

Generated Clock : clk_tx

Master Source : clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKIN1 Master

Clock : clk_pin_p

Edges : {1 2 3}

Edge Shifts : {0.000 0.500 1.000}

Generated Sources : {clk_gen_i0/clk_core_i0/inst/mmcm_adv_inst/CLKOUT1}2.5、Clock Groups

2.5.1、About Clock Groups

默认情况下,Vivado IDE会对设计中所有时钟之间的路径进行时序分析,除非您使用时钟组或错误路径约束另行指定。set_clock_groups命令禁用您标识的时钟组之间的时序分析,而不是同一组内的时钟之间的时序分析。与set_false_path约束不同,时钟之间的两个方向上的计时都被忽略。

可以多次使用-group选项指定多组时钟。如果设计中的时钟组中不存在任何时钟,则该组将变为空。只有当至少有两个组有效且不为空时,set_clock_groups约束才会保持有效。如果只有一个组保持有效,而所有其他组都为空,则不应用set_clock_groups约束,并生成错误消息。

使用 schematic viewer或“Clock Networks Report ”来可视化时钟树的拓扑结构,并确定哪些时钟不能一起时序分析。您还可以使用“Clock Networks Report ”来查看两个时钟之间的现有约束,并确定它们是否共享相同的主时钟——也就是说,它们具有已知的相位关系——或者识别没有公共周期的时钟(不可扩展)。

小心:忽略两个时钟之间的时序分析并不意味着它们之间的路径将在硬件中正常工作。为了防止亚稳态,您必须验证这些路径是否具有适当的同步电路或异步数据传输协议。

2.5.2 Clock Categories

本节讨论同步、异步和不可扩展的时钟。

2.5.2.1 Synchronous Clocks

当两个时钟的相对相位可预测时,它们是同步的。当它们的树源于网表中的同一根,并且它们有一个公共周期时,通常会出现这种情况。例如,周期比为2的生成时钟及其主时钟是同步的,因为它们通过相同的网表资源传播到生成时钟源点,并且具有2个周期的公共周期。它们可以安全地进行定时。

2.5.2.1.2 Asynchronous Clocks

当无法确定两个时钟的相对相位时,它们是异步的。例如,由板上单独的振荡器生成并通过不同的输入端口进入FPGA的两个时钟没有已知的相位关系。因此,它们必须被视为异步的。如果它们是由板上的同一个振荡器产生的,那就不是真的了。在大多数情况下,主时钟可以被视为异步时钟。当与它们各自生成的时钟相关联时,它们形成异步时钟组。

2.5.2.1.3 Unexpandable Clocks(不可扩展时钟)

当时序引擎无法确定超过1000个循环的共同周期时,两个时钟是不可扩展的。在这种情况下,在时序分析过程中使用了1000个循环中最差的设置关系,但时序引擎无法确保这是最悲观的情况。这通常是在具有奇数分数周期比的两个时钟之间的情况。例如,考虑由共享相同主时钟的两个MMCM生成的两个时钟clk0和clk1:

• clk0 has a 5.125 ns period.

• clk1 has a 6.666 ns period.

在两个时钟之间的定时路径上需要0.01ns。即使这两个时钟在其时钟树根处具有已知的相位关系,它们的波形也不允许在它们之间进行安全的时序分析。与异步时钟一样,松弛计算正常出现,但该值不可信。由于这个原因,不可扩展的时钟通常被同化为异步时钟。对于约束电路和跨时钟域电路,必须以相同的方式处理这两种时钟类别。

2.5.3Asynchronous Clock Groups(异步时钟组)

异步时钟和不可扩展的时钟无法安全计时。在分析过程中,可以使用set_clock_groups命令忽略它们之间的时序路径。

重要提示:set_clock_groups命令的优先级高于常规时序异常。如果需要约束和报告异步时钟之间的某些路径,则必须仅使用时序异常,而不能使用set_clock_groups。

2.5.3.1 Asynchronous Clock Groups Examples

•主时钟clk0在输入端口上定义,并到达生成时钟usrclk和itfclk的MMCM。

•第二主时钟clk1是在GTP实例的输出上定义的恢复时钟,并到达生成时钟gtclkrx和gtclktx的第二MMCM。

2.5.3.1.1 Creating Asynchronous Clock Groups

使用-asynchronous选项可以创建异步组。

set_clock_groups -name async_clk0_clk1 -asynchronous -group {clk0 usrclk

itfclk} \

-group {clk1 gtclkrx gtclktx}如果无法提前预测生成的时钟的名称,请使用get_clocks-include_generated_clocks动态检索它们。-include_generated_clocks选项是一个SDC扩展。前面的例子也可以写成:

set_clock_groups -name async_clk0_clk1 -asynchronous \

-group [get_clocks -include_generated_clocks clk0] \

-group [get_clocks -include_generated_clocks clk1]2.5.3.2 Exclusive Clock Groups(专用时钟组)

一些设计具有几种需要使用不同时钟的操作模式。时钟之间的选择通常由诸如BUFGMUX和BUFGCTRL之类的时钟多路复用器或LUT来完成。

建议:尽可能避免在时钟树中使用LUT。

由于这些单元是组合单元,Vivado IDE将所有输入时钟传播到输出。使用Vivado IDE,时钟树上可以同时存在多个定时时钟,这便于同时报告所有操作模式,但在硬件中是不可能的。

这种时钟被称为专用时钟。通过使用的选项对其进行约束set_clock_groups:

• -logically_exclusive

• -physically_exclusive

2.5.3.2 .1Exclusive Clock Groups Example

MMCM实例生成clk0和clk1,它们连接到BUFGMUX实例clkmux。clkmux的输出驱动设计时钟树。默认情况下,Vivado IDE会分析clk0和clk1之间的路径,即使这两个时钟共享同一时钟树并且不能同时存在。必须输入以下约束才能禁用两个时钟之间的分析:

set_clock_groups -name exclusive_clk0_clk1 -physically_exclusive \

-group clk0 -group clk1以下选项在Xilinx FPGA的上下文中是等效的:

• -logically_exclusive

• -physically_exclusive

物理和逻辑标签指的是ASIC技术中的各种信号完整性分析(串扰)模式,Xilinx FPGA不需要这些模式。

2.6 Clock Latency, Jitter, and Uncertainty(时钟延迟,抖动,和不确定性)

除了定义时钟波形外,还必须指定与操作条件和环境相关的可预测和随机变化。

2.6.1 Clock Latency

在板上和FPGA内部传播后,时钟边沿以一定的延迟到达目的地。这种延迟通常表示为:

•源延迟(通常在设备外部时钟源点之前的延迟)•网络延迟

由网络延迟引入的延迟(也称为插入延迟)是自动估计的(路由前设计)或精确计算的(路由后设计)。

2.6.2 Clock Uncertainty

2.6.1 Clock Jitter

对于ASIC器件,时钟抖动通常用时钟不确定性特性来表示。然而,对于Xilinx FPGA,抖动特性是可以预测的。它们可以由时序分析引擎自动计算,也可以单独指定。

2.6.2.1 Input Jitter

输入抖动是连续时钟边沿之间相对于标称或理想时钟到达时间的变化的差异。输入抖动是一个绝对值,表示时钟边沿每一侧的变化。使用set_input_jitter命令分别指定每个主时钟的输入抖动。不能直接在生成的时钟上指定输入抖动。Vivado IDE时序引擎自动计算生成的时钟从其主时钟继承的抖动。

•对于生成的时钟由MMCM或PLL驱动的情况,输入抖动将替换为计算的离散抖动。

•如果生成的时钟是由组合或时序单元创建的,则生成的时钟抖动与其主时钟抖动相同。

2.6.2.2System Jitter

系统抖动是由于电源噪声、板噪声或系统的任何额外抖动引起的整体抖动。

2.6.3Additional Clock Uncertainty

根据需要,使用set_clock_uncretainty命令为不同的角点、延迟或特定的时钟关系定义额外的时钟不确定性。这是一种从时序角度为设计的一部分添加额外裕度的方便方法。无论约束的顺序如何,时钟间的不确定性总是优先于简单的时钟不确定性。在下面的示例中,尽管在时钟clk1上最后定义了1.0ns的简单时钟不确定性,但是从时钟clk1到时钟clk2的时序路径受到2.0ns时钟不确定性的约束。

set_clock_uncertainty 2.0 -from [get_clocks clk1] -to [get_clocks clk2]

set_clock_uncertainty 1.0 [get_clocks clk1]当在两个时钟域之间定义时钟间不确定性时,请确保约束时钟域的所有可能交互:

• clk1 to clk2

• clk2 to clk1