牛客网Verilog刷题——VL12

- 题目

- 答案

题目

4bit超前进位加法器的逻辑表达式如下:

G

i

G_i

Gi=

A

i

A_i

Ai

B

i

B_i

Bi,

P

i

P_i

Pi=

A

i

A_i

Ai

⊕

\oplus

⊕

B

i

B_i

Bi

和:

S

i

S_i

Si=

P

i

P_i

Pi

⊕

\oplus

⊕

C

i

−

1

C_{i-1}

Ci−1

进位:

C

i

C_i

Ci=

G

i

G_i

Gi +

P

i

P_i

Pi

C

i

−

1

C_{i-1}

Ci−1

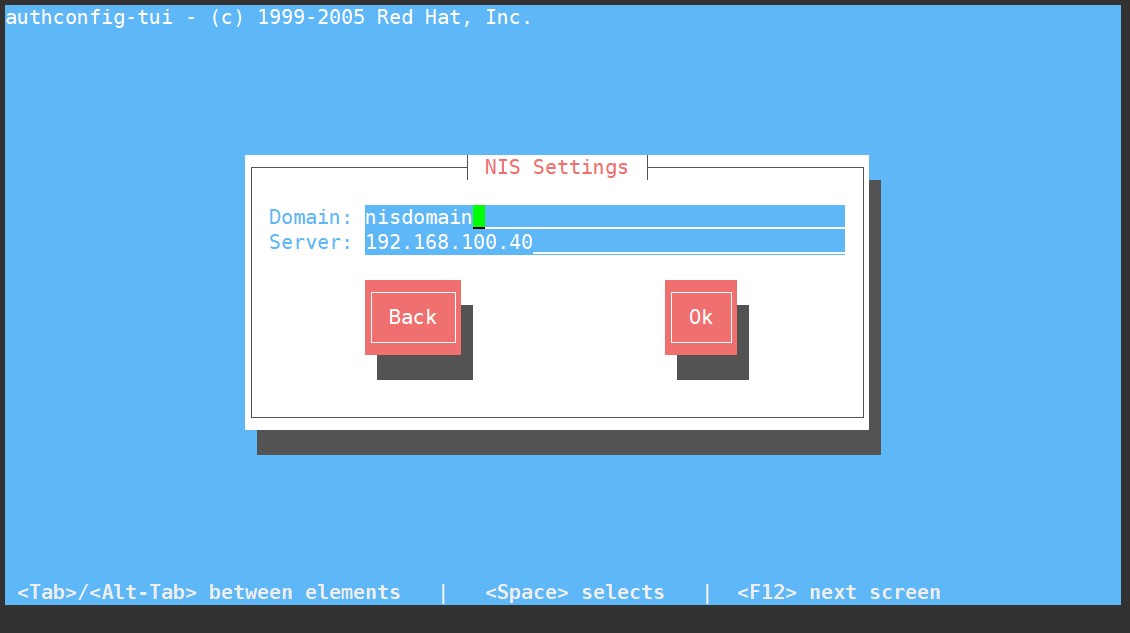

请用Verilog语言采用门级描述方式,实现此4bit超前进位加法器,接口电路如下:

| 信号 | 类型 | 输入/输出 | 位宽 |

|---|---|---|---|

| A_in | wire | Intput | 4 |

| B_in | wire | Intput | 4 |

| C_1 | wire | Intput | 1 |

| CO | wire | Output | 1 |

| S | wire | Output | 4 |

答案

`timescale 1ns/1ns

module lca_4(

input [3:0] A_in ,

input [3:0] B_in ,

input C_1 ,

output wire CO ,

output wire [3:0] S

);

wire [3:0] G;

wire [3:0] P;

wire [3:0] C;

assign G = A_in & B_in;

assign P = A_in ^ B_in;

assign C[0] = G[0] | P[0] & C_1;

assign C[1] = G[1] | P[1] & C[0];

assign C[2] = G[2] | P[2] & C[1];

assign C[3] = G[3] | P[3] & C[2];

assign CO = C[3];

assign S[0] = P[0] ^ C_1;

assign S[1] = P[1] ^ C[0];

assign S[2] = P[2] ^ C[1];

assign S[3] = P[3] ^ C[2];

endmodule

![[比赛简介]AMP®-Parkinson‘s Disease Progression Prediction](https://img-blog.csdnimg.cn/48fe5ea8a2a943e6ab3af2aeb50f9b7a.png)