第一章 从PCB开始研究FPGA设计问题

一、PCB布线

1、要求

·对所有器件进行电源滤波,均匀分配电源,降低系统噪声。

·匹配信号线,减小信号反射。

·降低并行走线之间的串扰。

·减小地反弹效应。

·进行阻抗匹配。

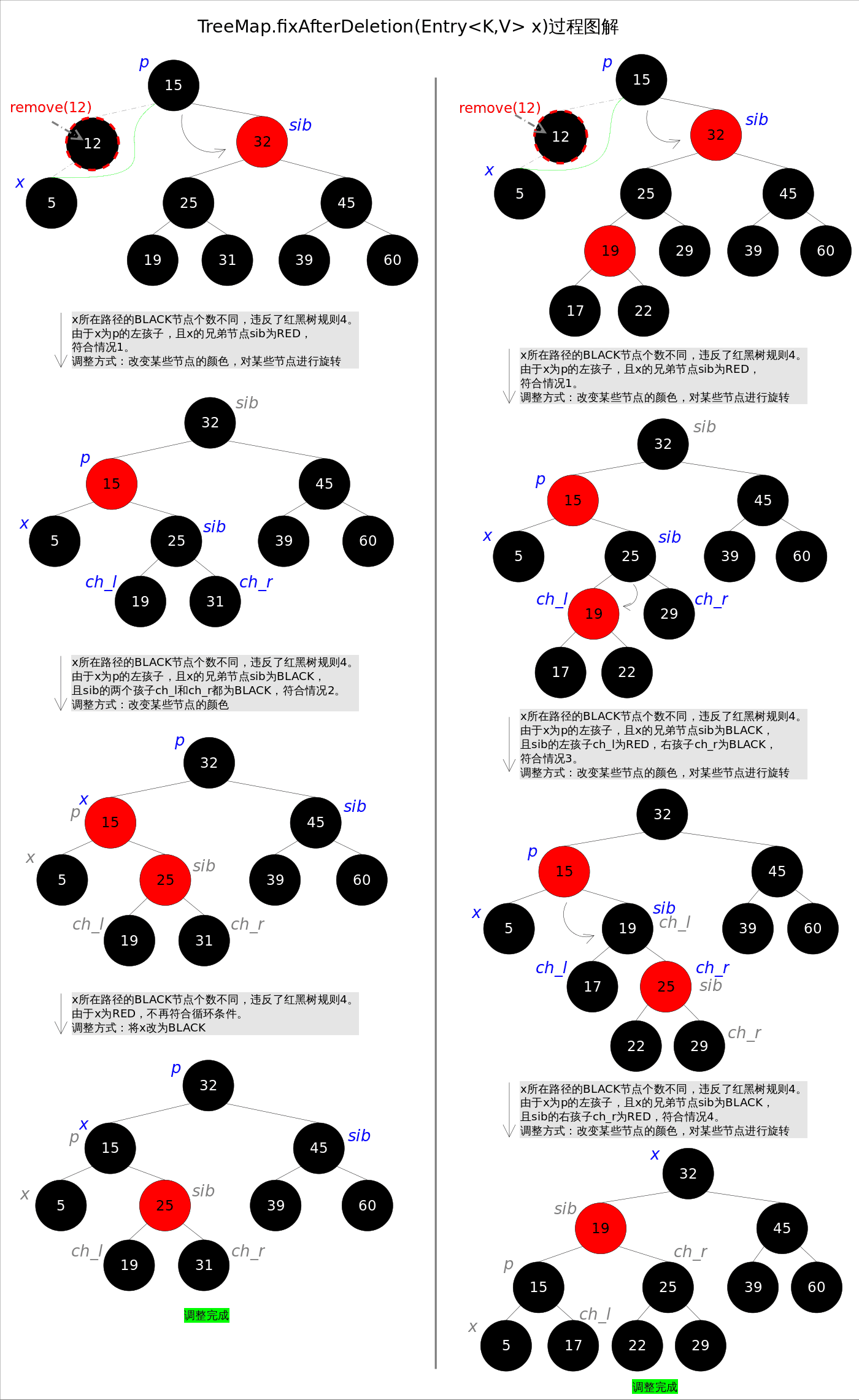

2、微带传输布局,走线在PCB的顶层或底层,只有一个参考平面

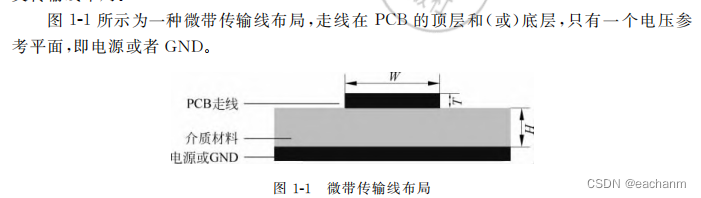

3、带状传输线布局,走线在PCB内层,有两个电压参考平面

4、阻抗控制原则:单端走线控制阻抗为50Ω;差分走线控制阻抗为100Ω。生产厂家阻抗控制的偏差范围一般为正负5%左右。

5、减小微带线或带状线布局串扰的方法是:

·在布线要求允许的范围内,尽可能地加宽信号线之间的距离。走线之间尽量不要靠

近,距离保持在介质高度的3倍以上。

·传输线设计要使导体尽可能靠近地平面。这一方法使得传输线能够与地平面紧耦

合,有助于和邻近信号去耦合。

·尽可能使用差分布线方法,特别是关键网络(例如匹配长度以及每条走线串通回

转等)。

·如果存在明显的耦合,应在不同层之间布设互相垂直的单端信号。

·减小单端信号之间并行走线的长度,以较短的并行走线布线,以减小网络之间的长

耦合走线。

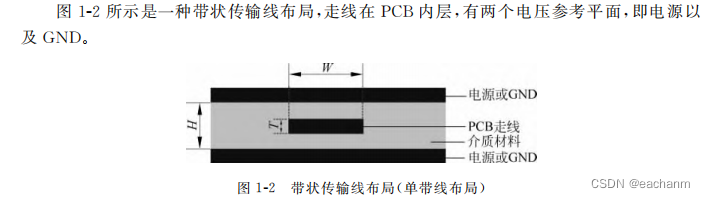

6、差分走线

二、FPGA供电

1、单调性(或线性)要求,是指在上电过程中,电源轨是单调爬升而不会掉头往下掉(也称

单调非负特性)。也就是说,电源必须始终具有正斜率(或零斜率)。

2、给电源供电设计加入电压上电顺序和电源跟踪。这来源于FPGA的I/O电压必需要在核心电压上电以后才能上电的基本规律。

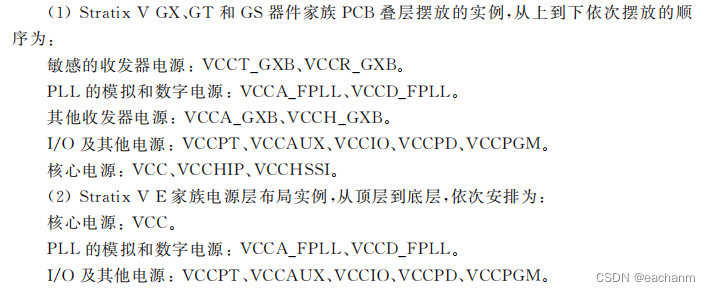

3、电源和地叠层分布

三、退耦电容

1、退耦电容可以在电源轨波动时为其提供少量的瞬态能量。

2、为何需要退耦电容?

可以将一个退耦电容看做是一组电阻(R)、电感(L)和电容(C)的串联组合,根据真实的RLC模型可知,电容也将在某个频率点上容抗和感抗分量彼此有效抵消。所以说,一个真实的电容将会在某个频点时阻抗最小,这个阻抗最小的点被称为电容的谐振频率,在这个点上退耦电容可以提供最佳的滤除供电干扰的能力。

第二章 如何处理逻辑设计中的时钟域

1、单比特信号跨时钟域的同步处理

1、跨时钟域(Clock Domain Crossing,CDC)是指设计中存在着两个或两个以上异步时钟

域,跨时钟域设计问题目前是逻辑设计者经常面临的问题,解决这类问题的方法被称为

CDC技术,即跨时钟域技术。

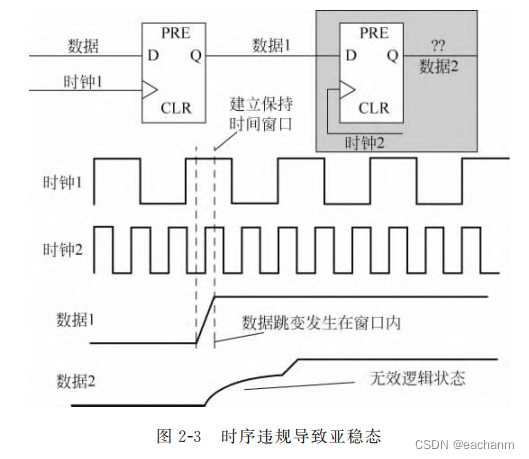

2、产生压稳态的原因:

触发器的建立时间和保持时间在时钟上升沿左右定义了一个时间窗口,如果触发器

数据输人端口上的数据在这个时间窗口内发生变化(或者数据更新),那么就会产生时序违

规。存在这个时序违规是因为建立时间要求和保持时间要求被违反了,此时触发器内部的

某个节点可能会在一个电压范围内浮动,无法稳定在逻辑0或者逻辑1状态。换句话说,如

果数据在上述窗口中被采集,触发器中的晶体管不能可靠地设置为逻辑0或者逻辑1对应

的电平上。

3、处理亚稳态的方法

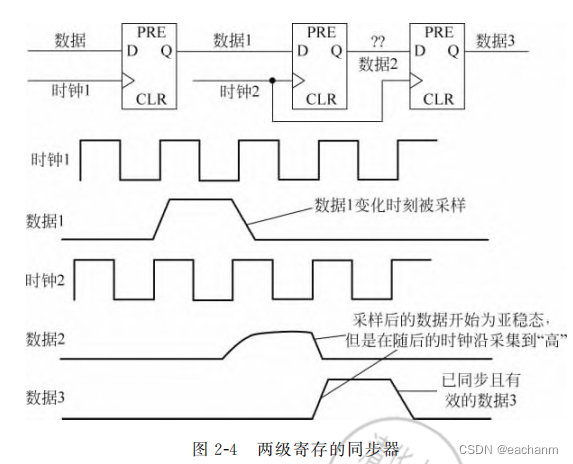

1、双触发

a、 最常见的同步器就是使用两级寄存器,即使用寄存器打两拍的方式进行同步。

应遵循原则:

级联的寄存器必须使用同一个采样时钟。

发送端时钟域寄存器输出和接收端异步时钟域级联寄存器输入之间不能有任何其他组合逻辑。

同步器中级联的寄存器中除了最后一个寄存器外所有的寄存器只能有一个扇出,即其只能驱动下一级寄存器的输入。

b、使用三级触发器对亚稳态进行同步处理

平均故障间隔时间(MTBF),对于前面讨论到的亚稳态同步器来说,这里的故障是指一个

被传输到同步触发器的信号,当它经过第一级同步触发器时处于亚稳态,在随后的一个时钟

周期内持续保持亚稳态并被采样到第二级同步器触发器, MTBF大好,所以一般在在高速设计中使用三级触发器同步。

4、同步快速信号到慢速时钟域

1、信号可能会丢失

如果丢失信号采样值对于设计来说是不允许的,那么有两种通用的应对方法可以解决这个问题:一个是开环解决方案,确保信号在无须确认的情况下可以被采集;另一个是闭环解决方案,即在跨时钟域边界时,信号需要接收端的反馈确认。

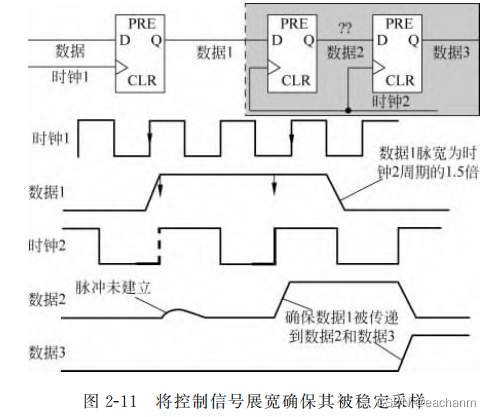

1、开环解决方案:

图2-11所示,需要将目标信号展宽到至少超过接收时钟域的时钟周期。前文提到,最佳的脉宽是至少为采样时钟周期的1.5倍,这样跨时钟域信号将会被接收时钟域的时钟至少稳定地采样一次。

2、闭环解决方案:

在发送时钟域将控制信号当使能信号传递,并将其同步到接收时钟域,然后接收时钟域收到使能控制信号之后,将同步的控制信号反馈到发送时钟域,发生时钟域通过另外一个同步器接收此反馈回来的控制信号,并以它作为信号正确接收的握手信号。

缺点:延迟大

5、多比特信号跨时钟域同步处理

1、在接收时钟域有一个寄存器,它需要一个加载(Load)信号和一个使能(Enable)信号来加载一个数值到寄存器。如果加载和使能信号在发送时钟域的同一个时钟沿被驱动有效(即两个控制信号需要同时有效),那么这两个控制信号之间就有可能存在产生一个小歪斜的机会,这就可能导致在接收时钟域中这两个信号被同步到不同的时钟周期。在这种情况下,数据是不能被加载到寄存器的。

解决:将加载和使能两个控制信号融合成一个单比特控制信号

2、用多周期路径规划来处理

多周期路径规划是一种通用的安全传递多比特跨时钟域信号技术。多周期路径规划是指在传输非同步数据到接收时钟域时配上一个同步的控制信号,数据和控制信号被同时发送到接收时钟域,同时控制信号在接收时钟域使用两级寄存器同步到接收时钟域,使用此同步后的控制信号来加载数据,这样数据就可以在目的寄存器被安全加载。

3、使用FIFO结构来处理多比特时钟域信号

1、FIFO在FPGA内一般是通过封装一个双口RAM来实现。

2、用格雷码做状态机

4、多时钟域设计分区划分

1、在时钟边界划分分区

2、多时钟域分区划分后的静态时序分析

3、设计中的门控时钟行波时钟的处理

行波时钟(Ripple Clock):行波时钟是指任何由寄存器驱动的时钟,常见的行波时钟为

利用逻辑(如计数器)进行时钟分频产生的时钟。

门控时钟:Altera给出的定义是,任何由非寄存器逻辑功能驱动的时钟都是门控时钟,

这些非寄存器资源大部分是FPGA内LAB里的LUT或ALUT。门控时钟可以提供一个

时钟开关功能,当然有时候门控时钟也可以是由其他组合逻辑驱动的时钟,比如时钟多路选

择器等。

5、衍生时钟处理指导原则

1、第一个指导原则是尽量不要使用行波或门控时钟,取而代之的是使用时钟使能或

PLL。时钟分频以及逻辑门开关时钟这类技术通常都是可以使用时钟使能和PLL来替

换的。

2、如果确实需要使用派生时钟,那么建议设计中不要有跨派生时钟域的同步数据路径。

3、如果使用Altera器件,那么在跨时钟域路径上遇到保持时间时序问题时,可以在

QuartusⅡ软件中将Optimize Hold Timing选项设置到All Paths.。具体设置方法是选择

Assignments→Settings--Fitter Settings。