WARNING:

本题为开放性题目,所设计的也仅仅是一个可能的模型而已,再考虑到个人水平有限。在呈现效果上难免会有缺漏以及可行性的缺陷。故请批判性地接收!

所以如果知识有错误或者缺漏,请一定要指出,您的建议这对于我的改进有很大帮助!

小组选题:第二题

所有题目:

第一题:

(1) 以VS-CPU为例,ALU单元中不用多路选择器如何实现,比较其优劣。

(2) 以RS-CPU为例,DR寄存器是否一定必要?如非必要,去除DR对设计有何变化?比较保留与去除的优劣。

(3) 除了四种常用方法下址产生方法外(当前地址加1、绝对地址、映射逻辑、微子程序返回地址),还有什么下址产生方法,试说明如何实现。

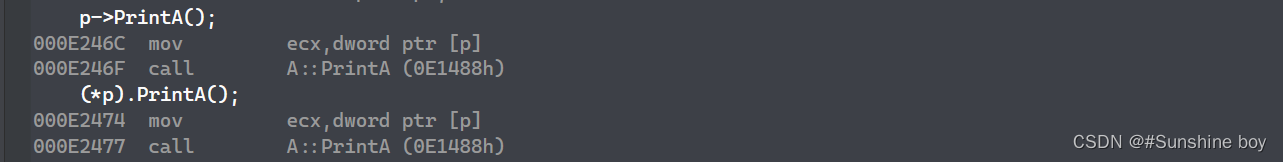

(4) 在分析VS-CPU的JMP指令RTL描述时,如果用PC←AR代替PC←DR[5..0],会对后继设计带来哪些影响?

第二题:

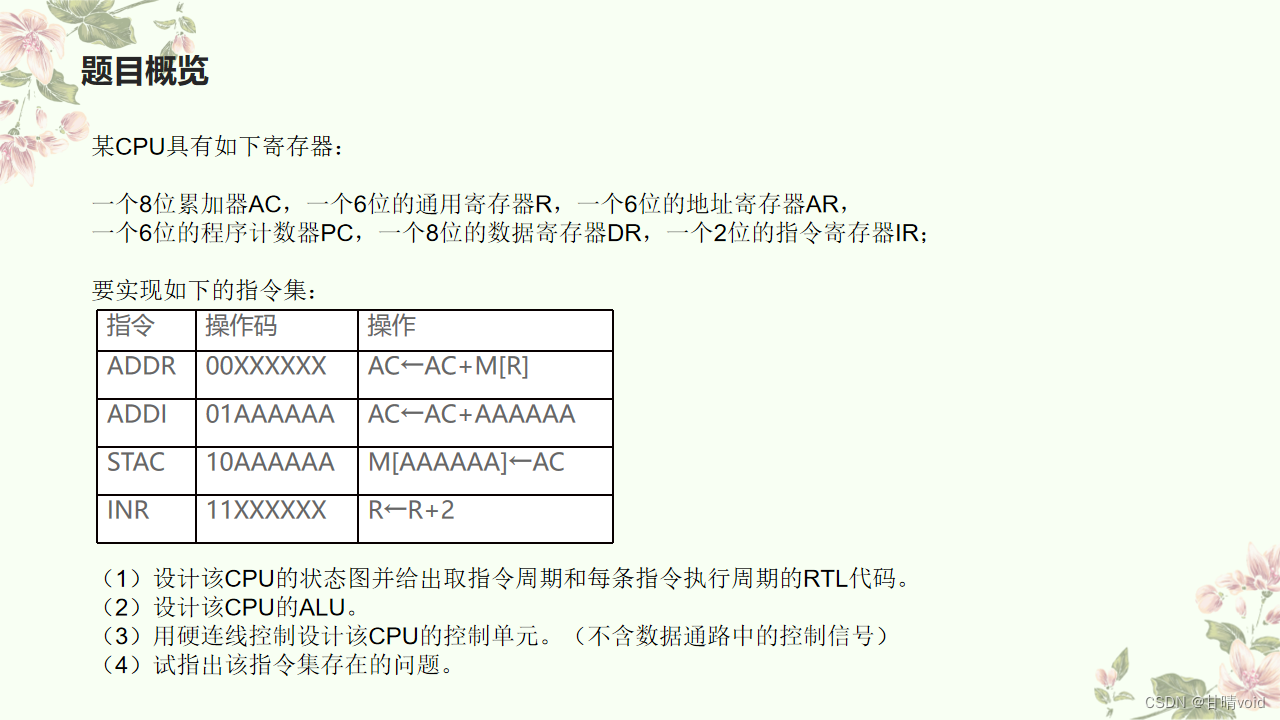

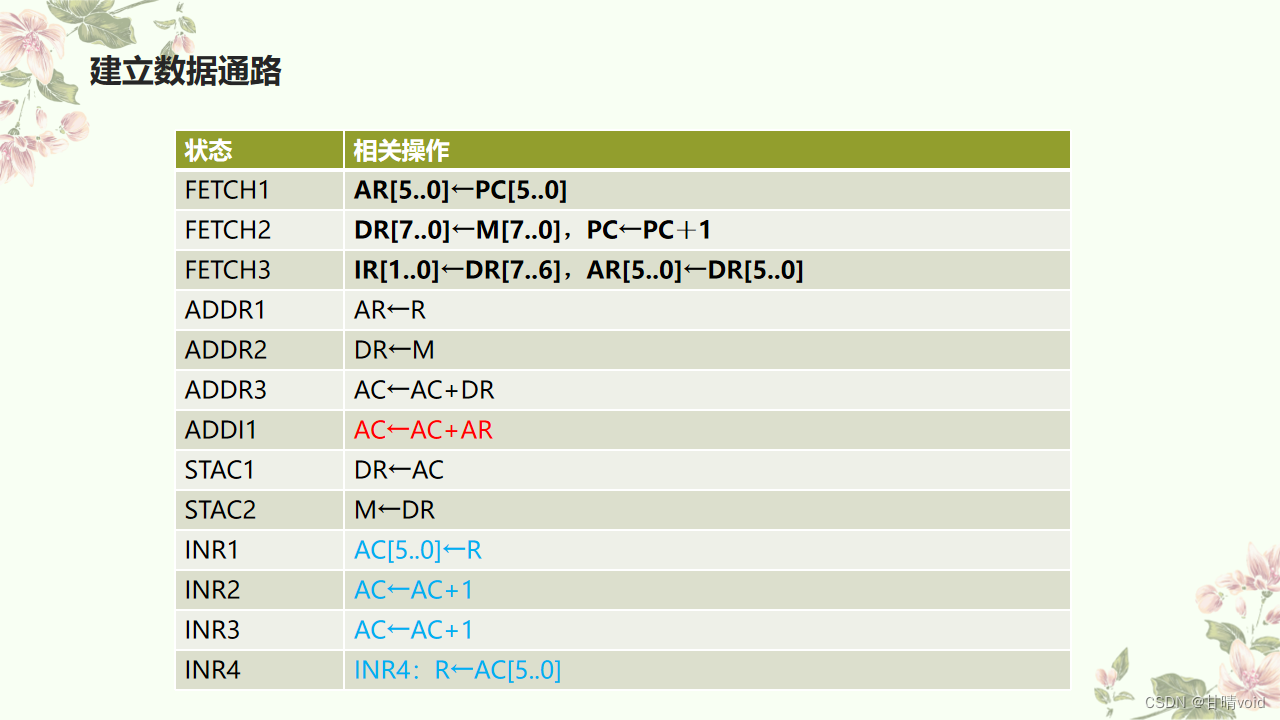

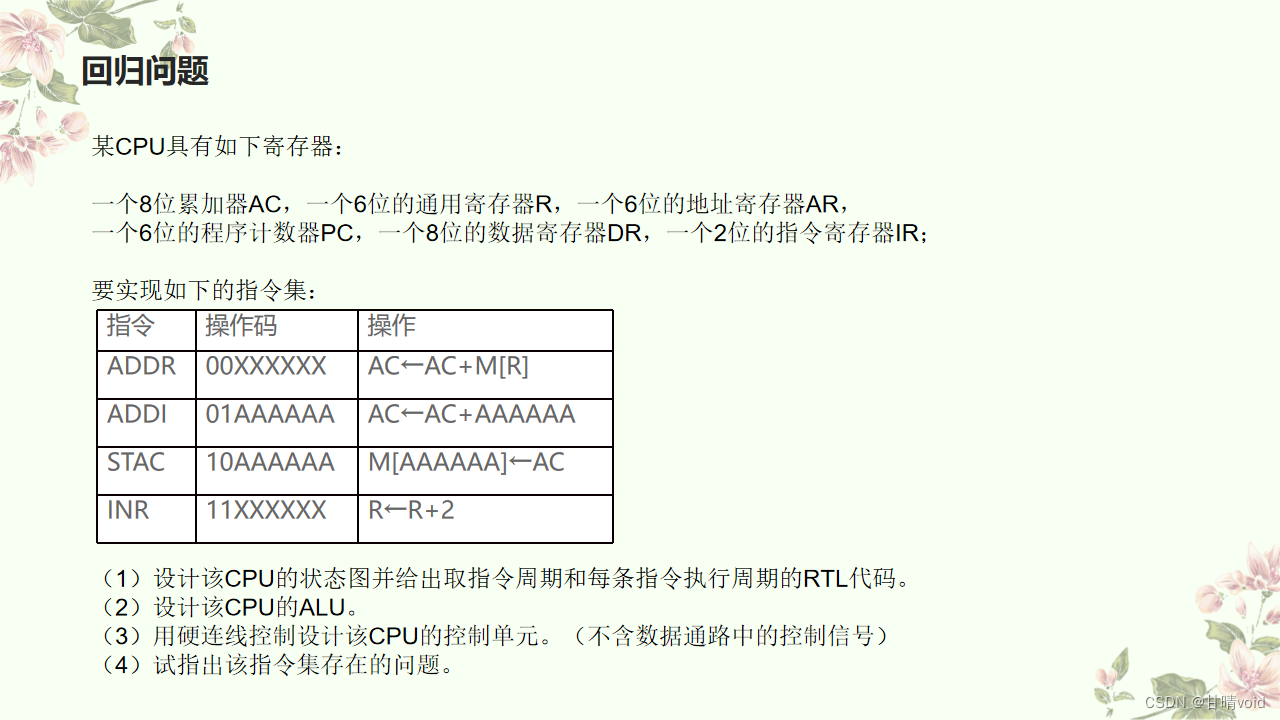

| 指令 | 操作码 | 操作 |

| ADDR | 00XXXXXX | AC←AC+M[R] |

| ADDI | 01AAAAAA | AC←AC+AAAAAA |

| STAC | 10AAAAAA | M[AAAAAA]←AC |

| INR | 11XXXXXX | R←R+2 |

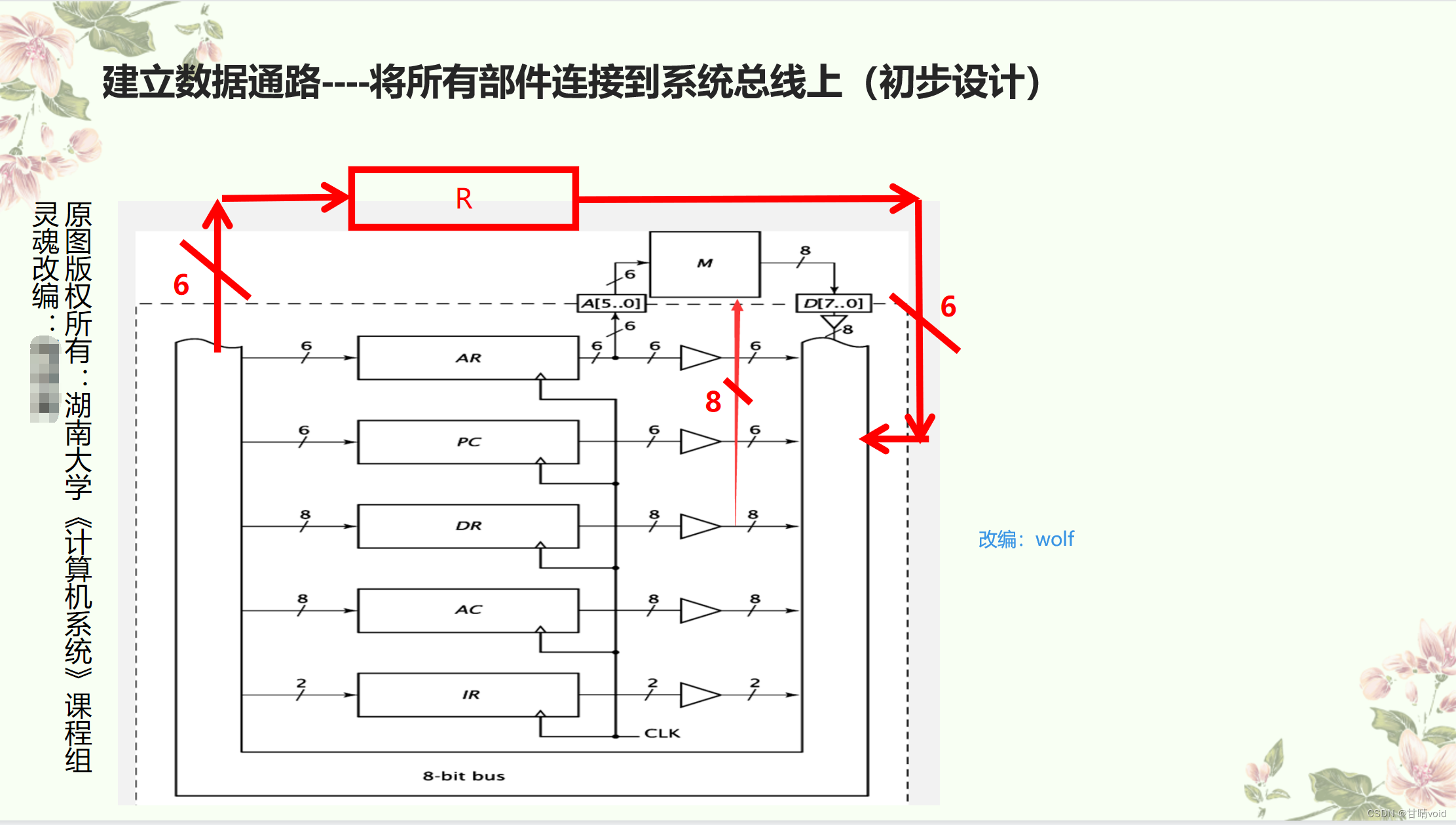

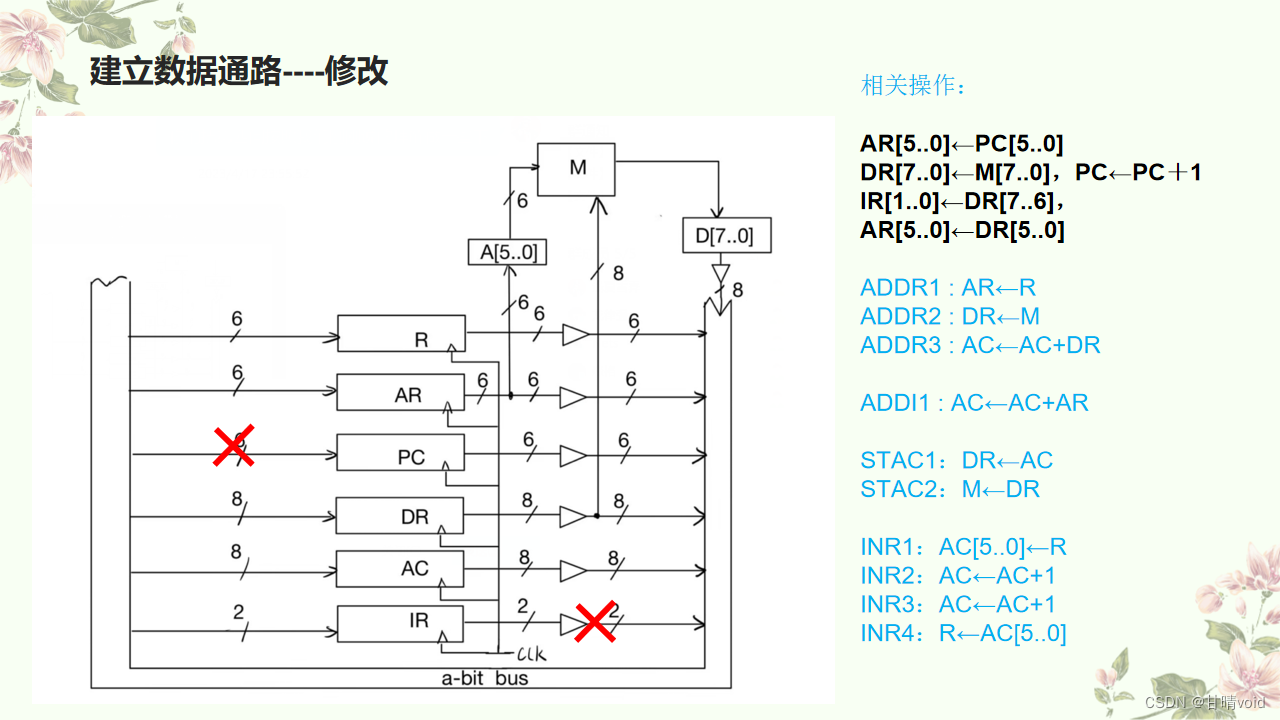

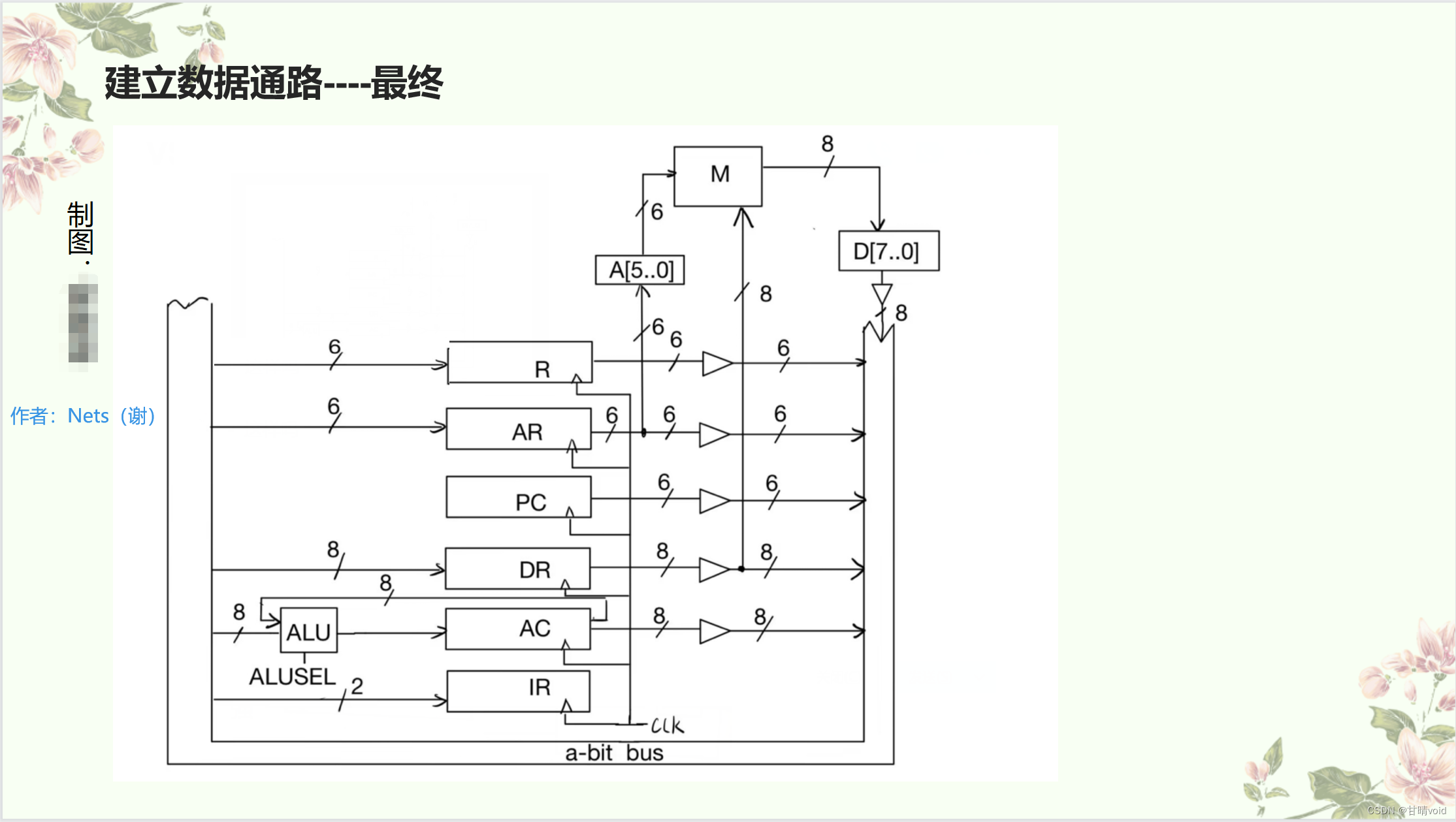

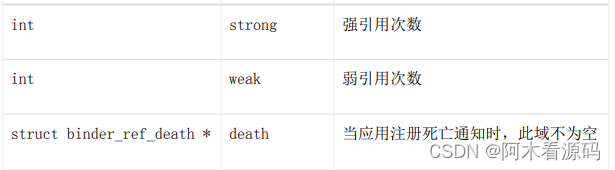

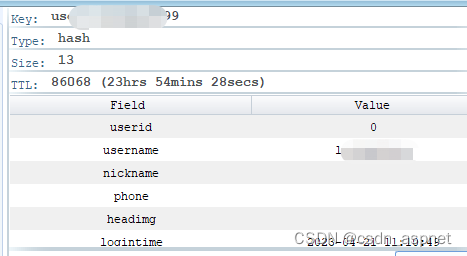

某CPU具有如下寄存器:一个8位累加器AC,一个6位的通用寄存器R,一个6位的地址寄存器AR,一个6位的程序计数器PC,一个8位的数据寄存器DR,一个2位的指令寄存器IR;要实现如下的指令集:

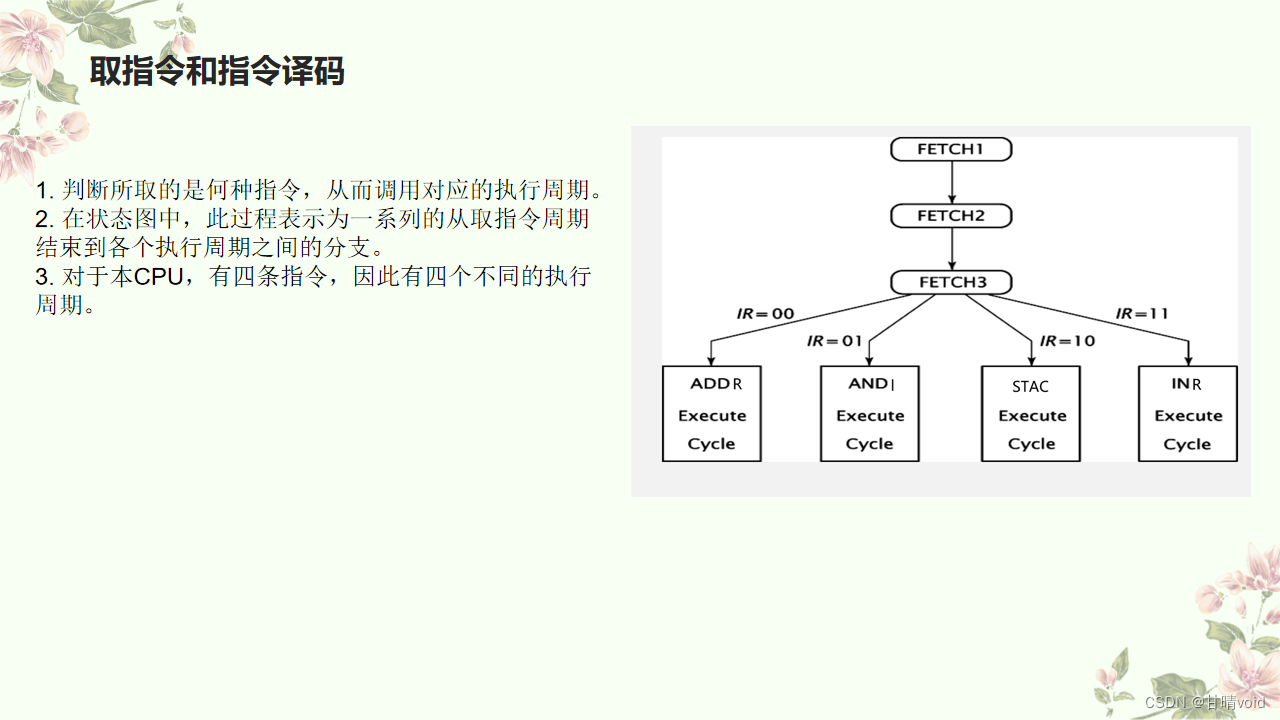

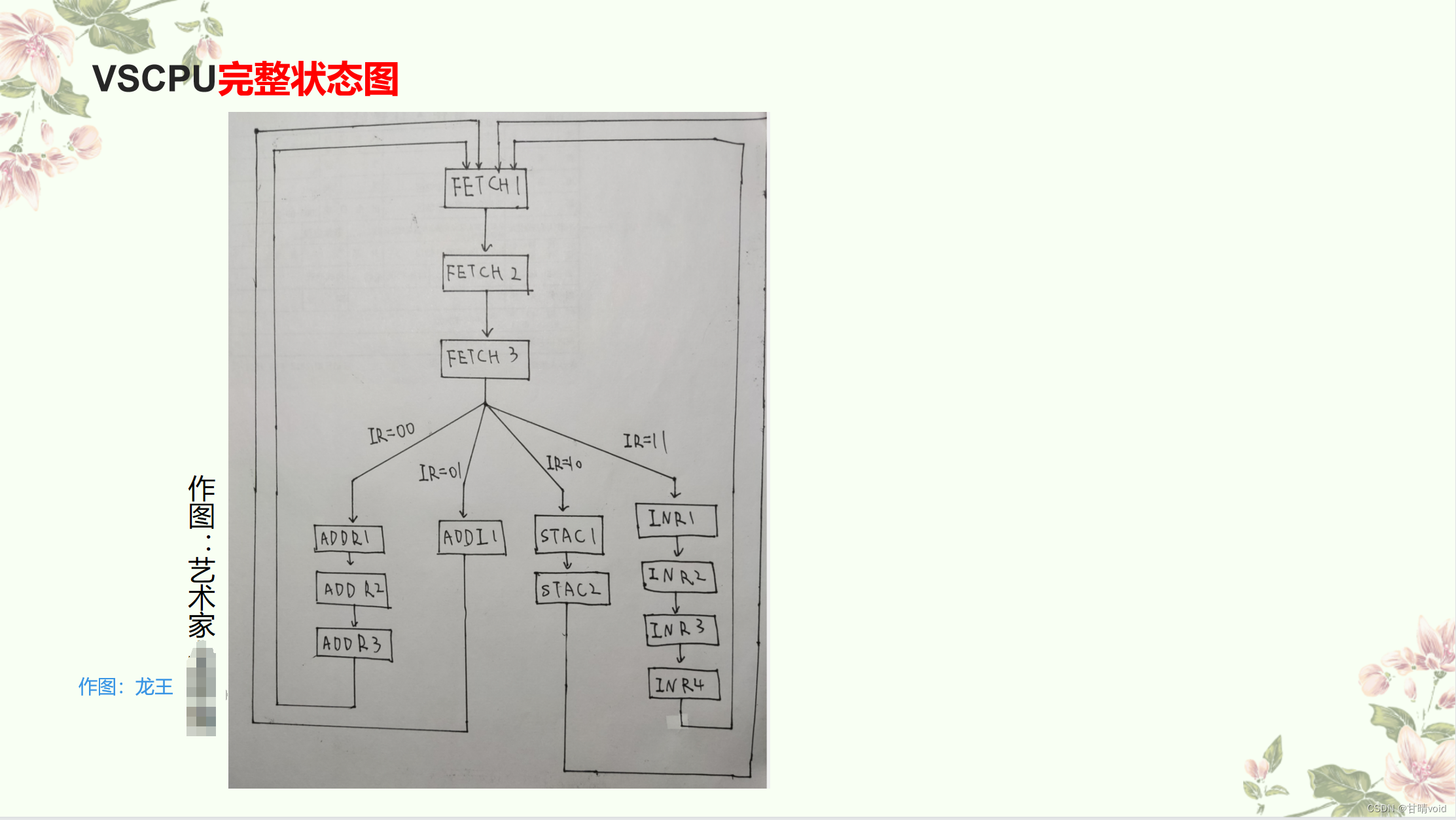

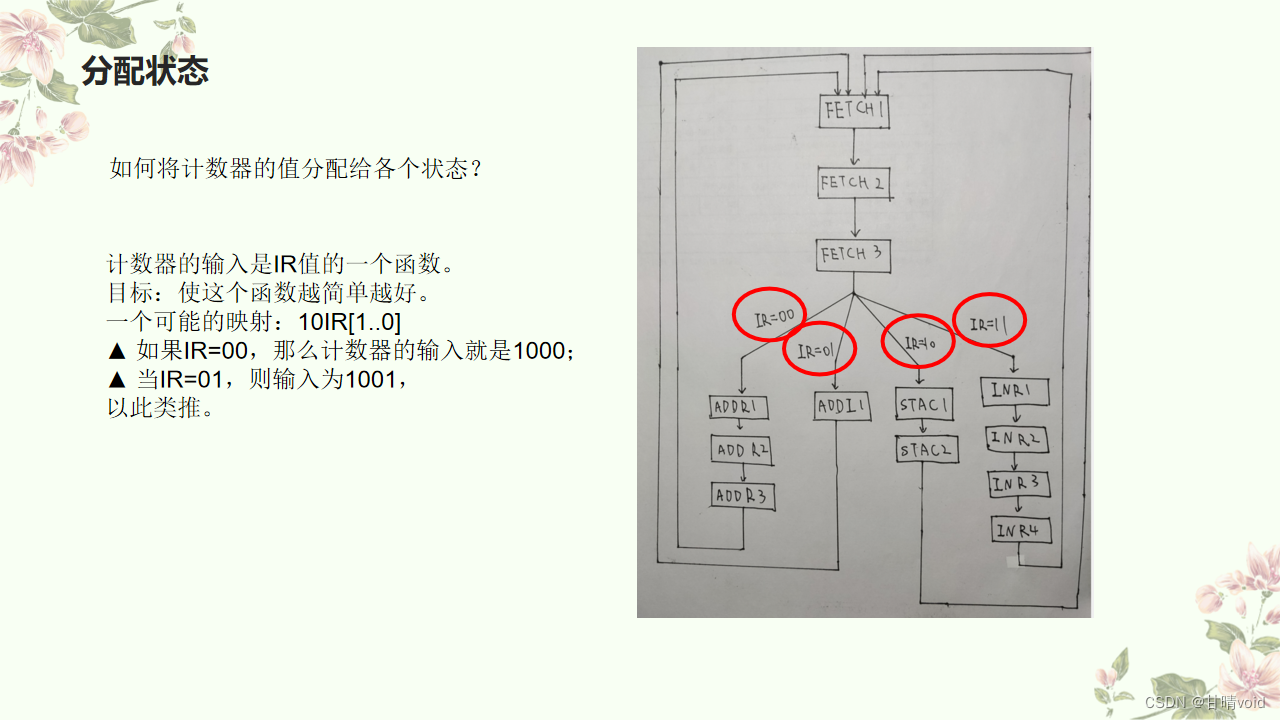

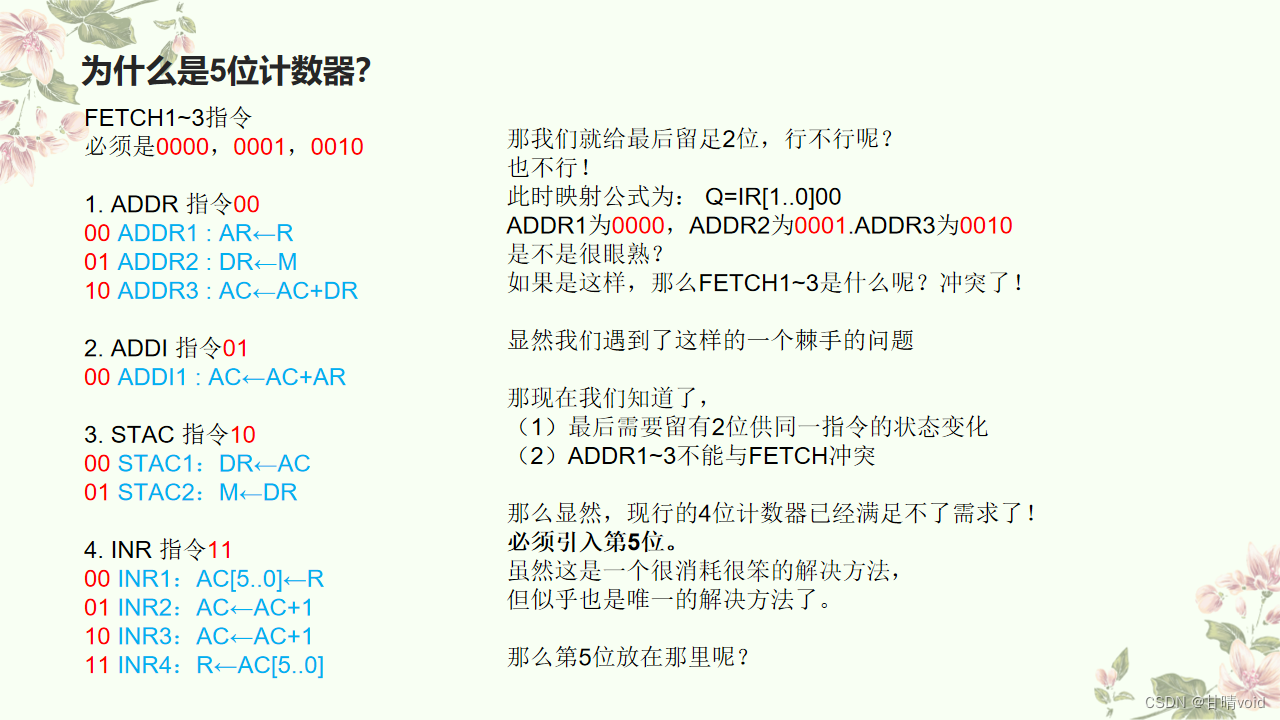

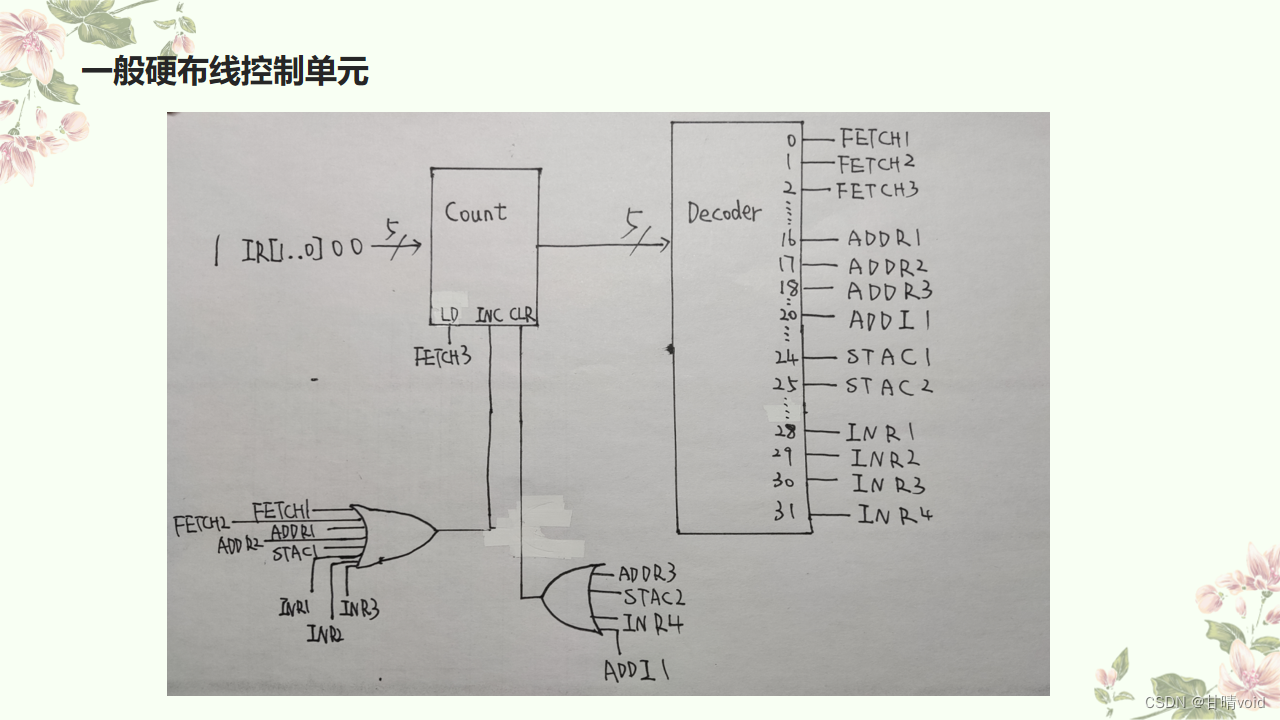

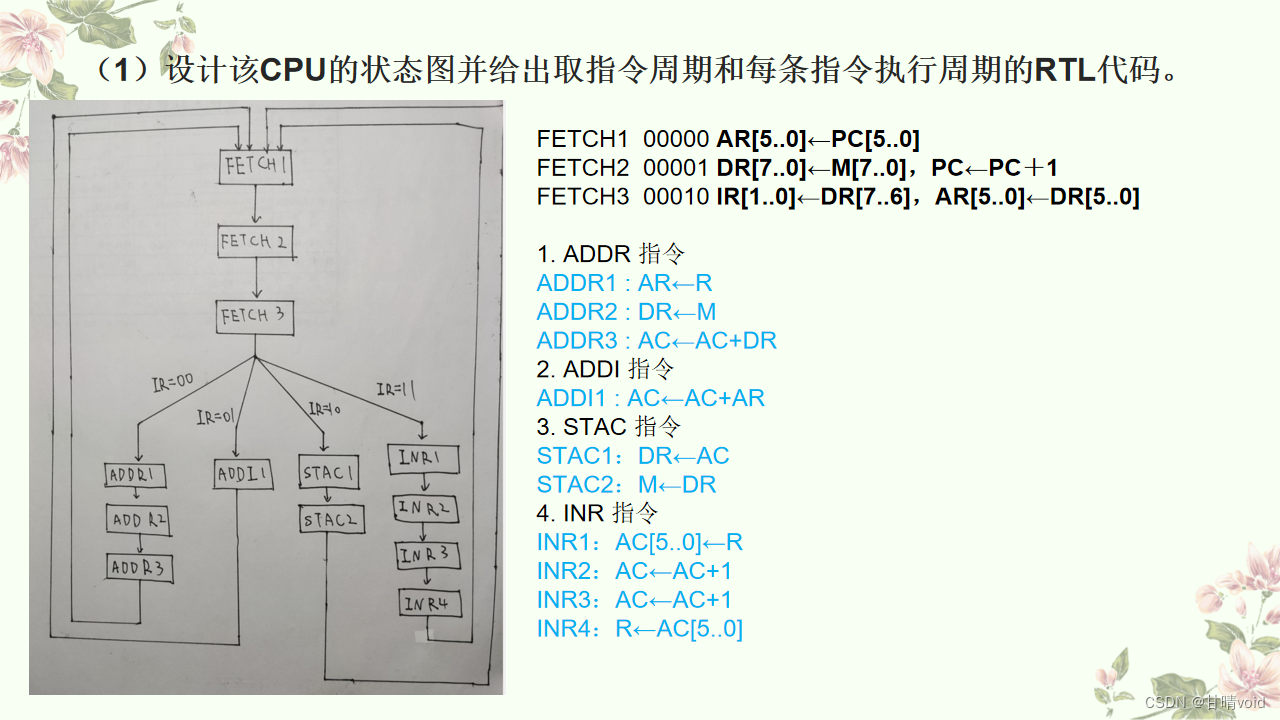

(1)设计该CPU的状态图并给出取指令周期和每条指令执行周期的RTL代码。

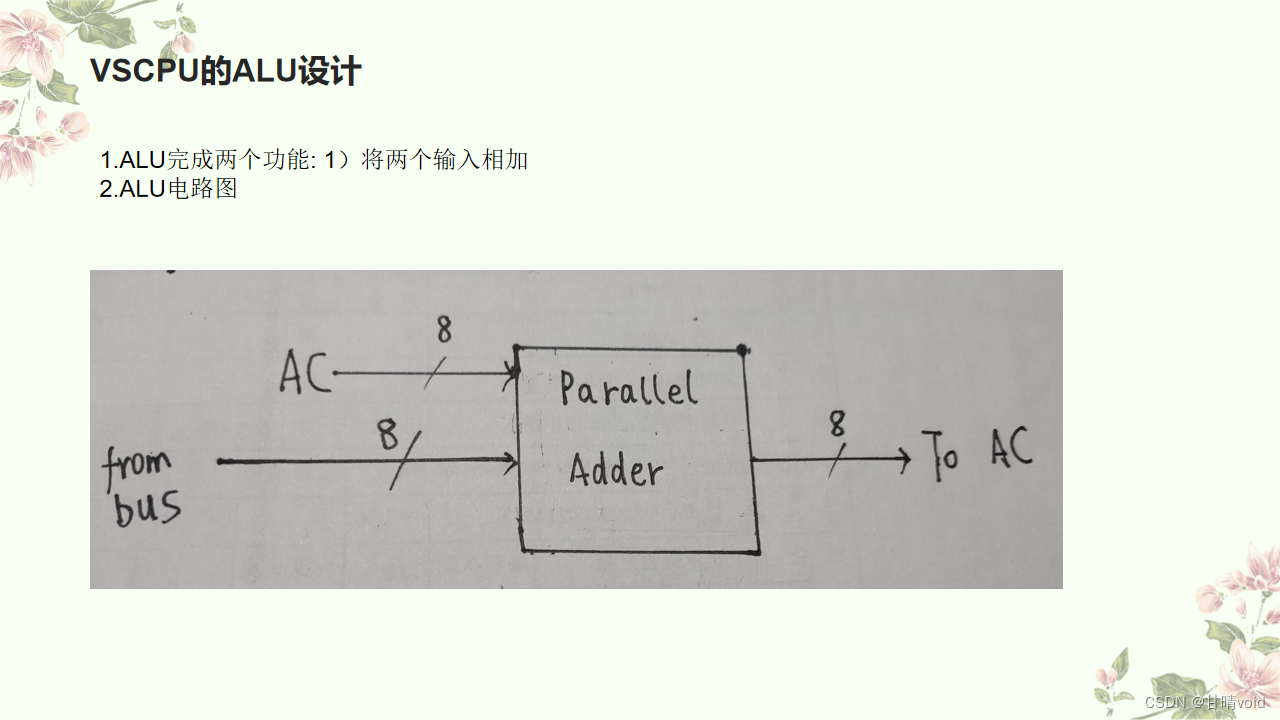

(2)设计该CPU的ALU。

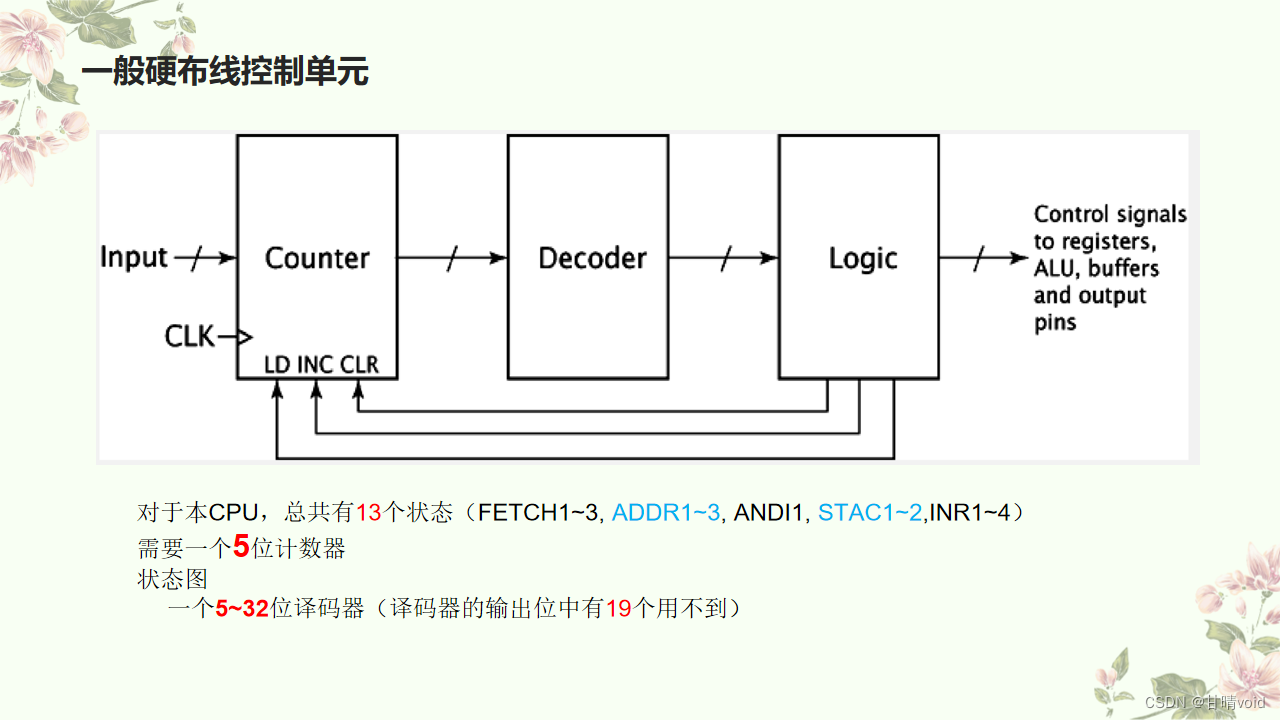

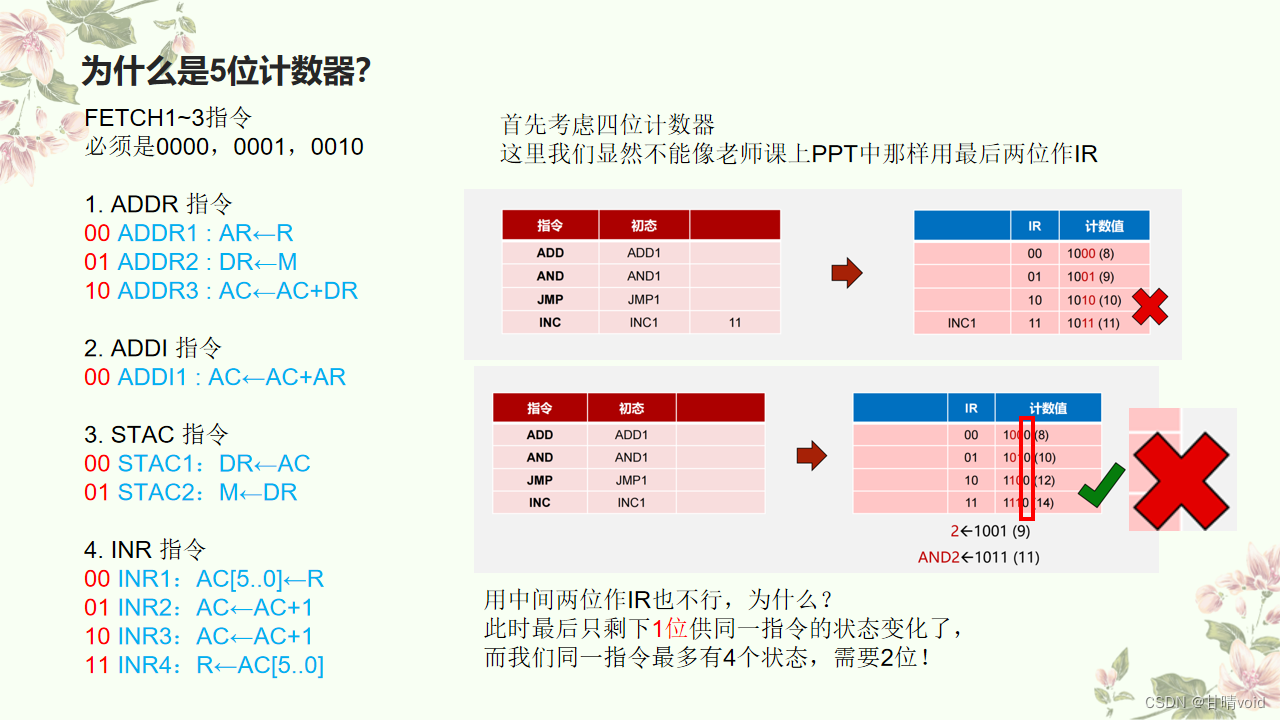

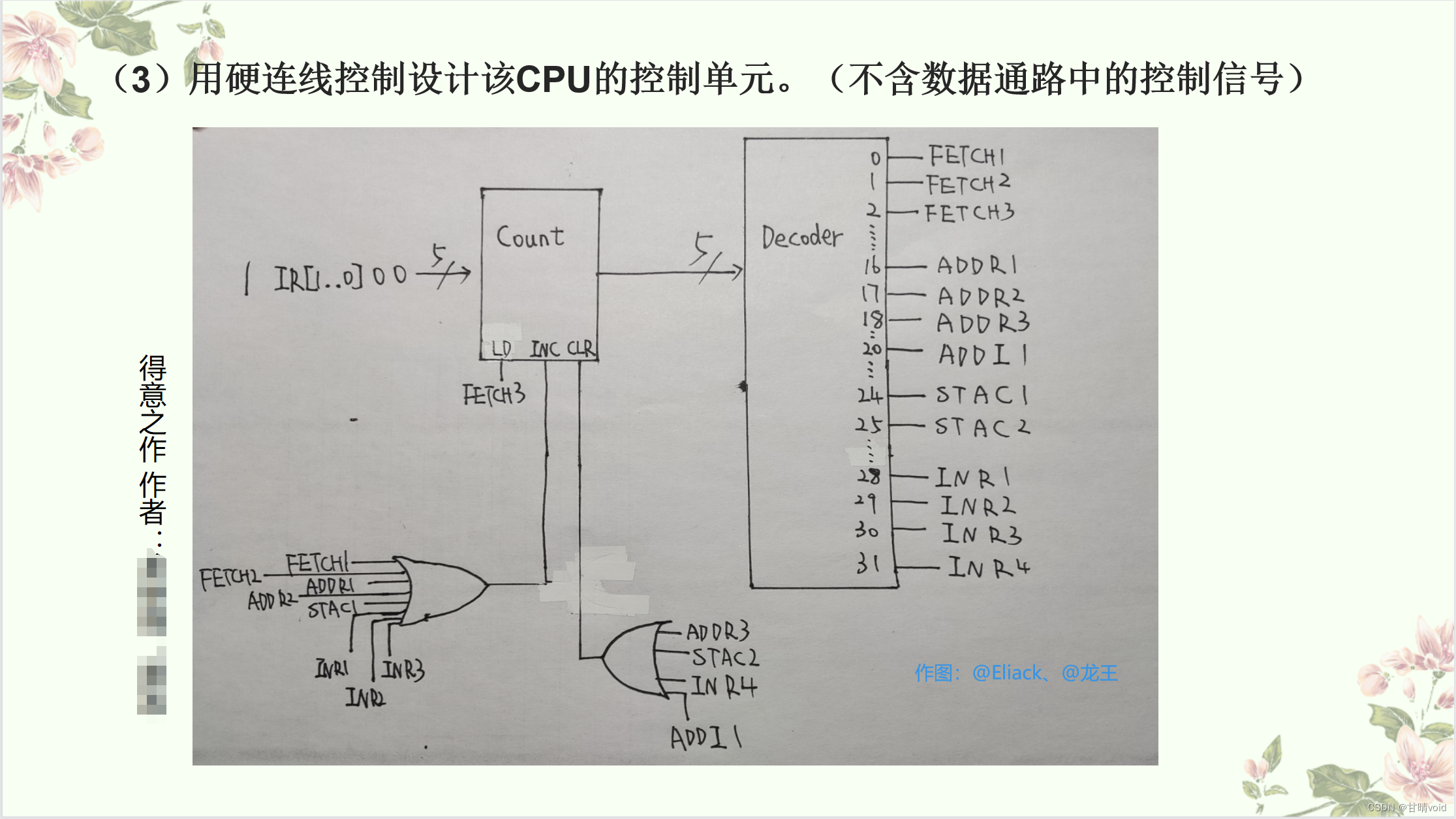

(3)用硬连线控制设计该CPU的控制单元。(不含数据通路中的控制信号)

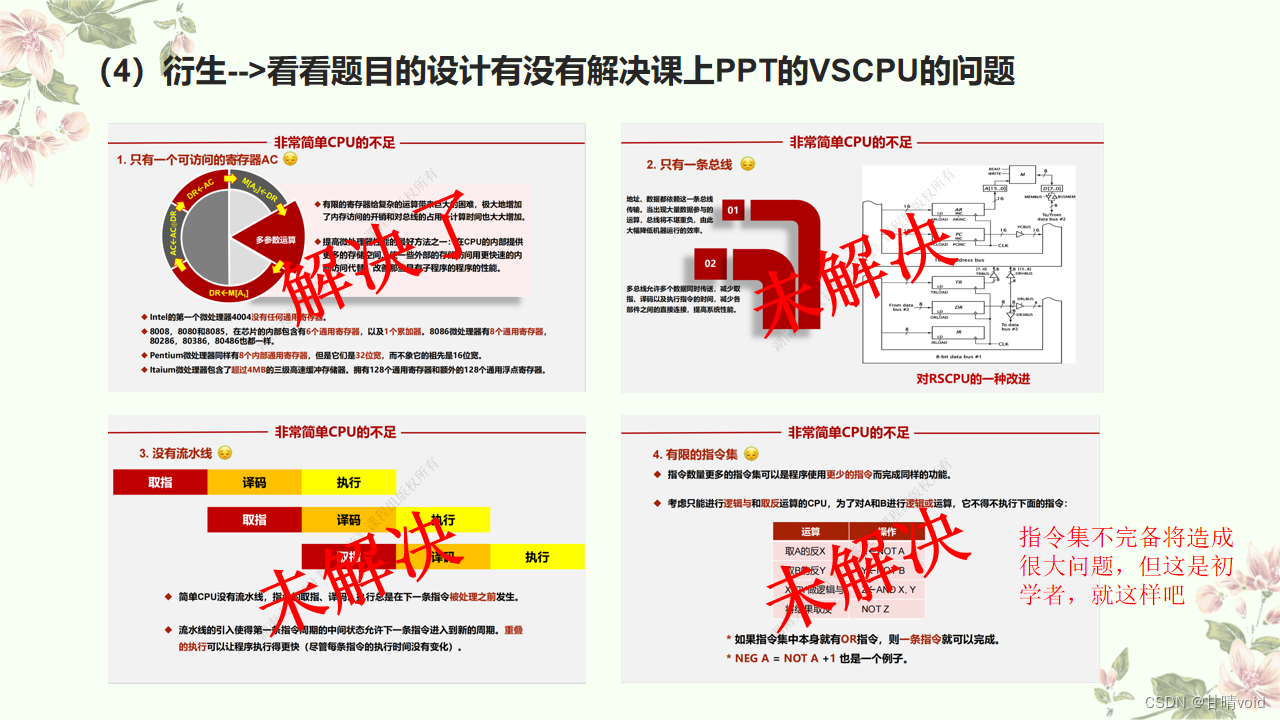

(4)试指出该指令集存在的问题。

第三题:

试设计一台有一个16位CPU,两个内存储器的计算机,该计算机可以同时从两个内存储器各读入一个8bit数据放入CPU的寄存器。画出其总线结构图(控制总线,数据总线,地址总线),简要解释其工作方法,并举例说明这样的体系结构在什么应用场景下能发挥其独特的优势。