📜 本章目录:

0x00 动态功耗(Dynamic Power)

0x01 集成电路成本(Integrated Circuit Cost)

0x02 基准测试(SPEC CPU Benchmark)

0x03 SPEC功率基准测试(SPEC Power Benchmark)

0x04 Pitfall:Amdahl’s 定律

0x05 Pitfall:将 MIPS 作为性能指标

0x00 动态功耗(Dynamic Power)

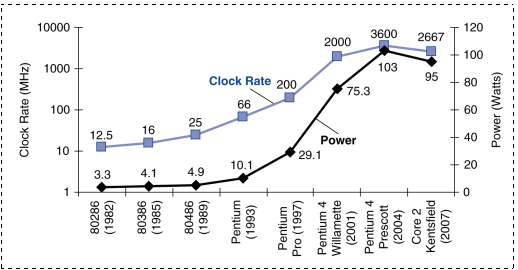

电力趋势(Power Trends)

芯片在工作时晶体管处于跳变状态所产生的功耗,我们称之为 动态功耗 (Dynamic Power)。

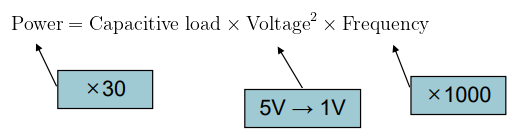

在 CMOS 集成电路技术方中,动态功耗计算:功率 = 电容性负载 × 电压^2 × 频率

Capacitive load 为电容性负载,当 Frequency 增大时,可以减少 Voltage 降低功耗。

然而,当 Voltage 持续减小到一定程度,再减小将会导致静态功耗增大,无法有效散热。

The power wall:我们无法进一步降低电压,我们无法消除更多的热量。

⚡ 简化记忆:

Reducing Power:我们假设一个新的 CPU ,比旧 CPU 的 85% 的电容性负载 (capacitive load),

电压 (voltage) 降低15%,频率 (frequency) 降低 15。那么 根据公式

Suppose a new CPU has 80% of capacitive load of old CPU and 10% valtage reduction. How much power reduction with new CPU?

Old CPU Voltage: 5.3V ClockRate 1GHz

New CPU Voltage: 3V ClockRate 2GHz

动态功耗主要包括两部分,即动态开关功耗()和短路功耗(

)。

动态开关功耗是在逻辑门进行开关事件时产生的功耗,即在 CMOS 逻辑门输出节点电压在逻辑转换过程中由于充电和放电引起的功耗。

在充电过程中,输出节点电压从 0 到 完全转换,其中一半的能量会以热的形式在 PMOS 管导通时被消耗,从而形成动态开关功耗。因此,动态功耗主要由逻辑门的输出电容引起。

另一方面,当 CMOS 逻辑门在有限的上升沿和下降沿(slew)输入电压的驱动下进行开关时,PMOS 和 NMOS 晶体管会在短时间内同步导通,从而在电源和地之间形成一条直流通路,产生短路功耗,这部分功耗被称为短路功耗(PSC)。

需要注意的是,这只是计算 CPU 动态功耗的一个简化公式,实际情况可能会更加复杂,因为现代CPU在设计上会包含更多的功耗管理技术和优化措施,例如动态电压频率调整(DVFS)、体系结构层面的功耗优化等。因此,在实际应用中,需要考虑更多因素来准确估计 CPU 的动态功耗。

0x01 集成电路成本(Integrated Circuit Cost)

与面积和缺陷率的非线性关系:晶片成本和面积是固定的,缺陷率由制造工艺决定,晶片面积由结构和电路设计决定。

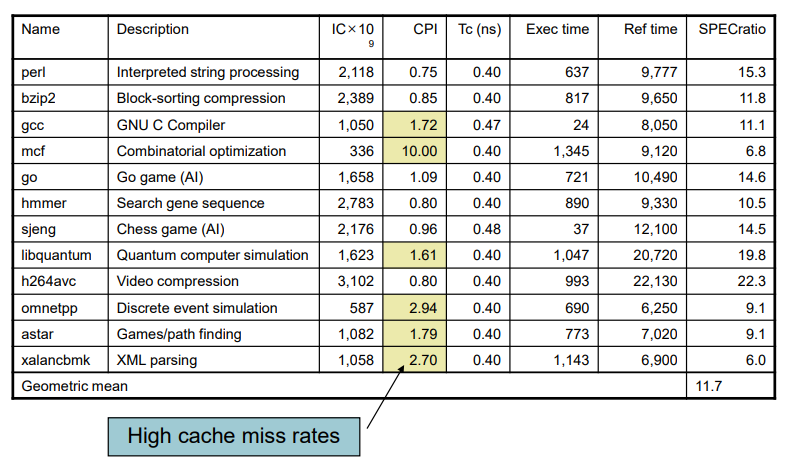

0x02 基准测试(SPEC CPU Benchmark)

用来衡量性能的程序,是实际工作负荷的典型代表。标准性能评估公司(SPEC):开发CPU、I/O、网络等方面的基准。SPEC CPU2006:

- 执行部分程序所需的时间

- 可忽略I/O,因此重点关注CPU性能

- 相对于参考机器进行归一化

- 总结为性能比的几何平均值

- CINT2006(整数)和CFP2006(浮点)

用于 Opteron X4 2356 的 CINT2006:

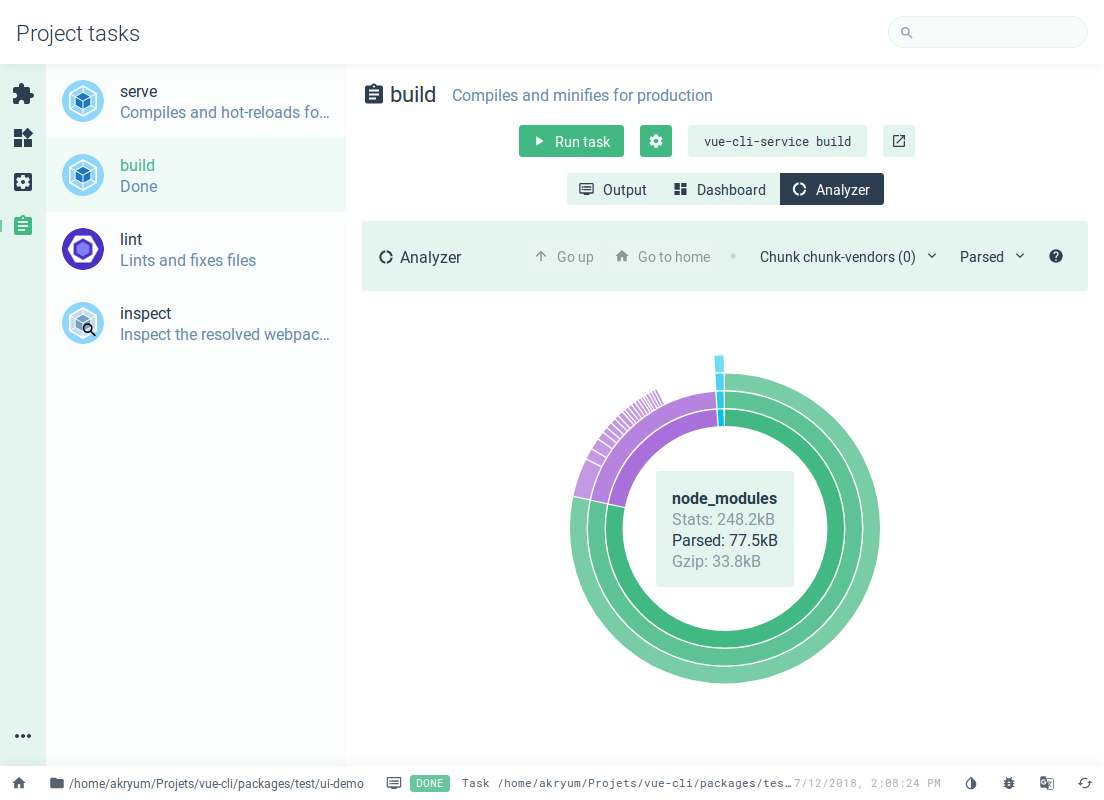

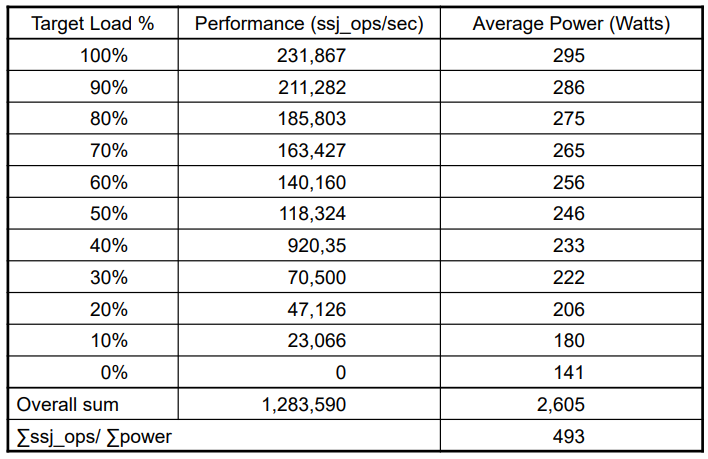

0x03 SPEC功率基准测试(SPEC Power Benchmark)

不同工作负荷水平下的服务器耗电量,性能:ssj_ops / sec,功率: 瓦特 (焦耳/秒)

X4 的 SPEC power_ssj2008:

0x04 Pitfall:Amdahl’s 定律

Amdahl's Law(阿姆达尔定律)是一种计算性能的定律,用于衡量在提升计算系统性能时,对某一部分进行优化的效果。它由计算机科学家 Gene Amdahl 在1967年提出,被广泛应用于计算系统的设计和性能优化。

改进计算机的一个方面,并期望在整体性能上有相应的改善:

💬 例子:multiply accounts for 80s/100s,How much improvement in multiply performance to get 5× overall?

Can't be done!

谬误: 闲置时的低功率

回顾一下X4的功率基准:在100%的负载下: 295W,在50%的负载下: 246W (83%),在10%的负载下: 180W (61%)。

谷歌数据中心:大多在10%-50%的负载下运行,在100%的负载下,不到1%的时间。

考虑设计处理器以使功率与负载成正比

0x05 Pitfall:将 MIPS 作为性能指标

在计算机体系结构和处理器设计中,MIPS(Million Instructions Per Second)是一种常用的性能指标,用于衡量处理器的性能。MIPS表示在一秒钟内能够执行的百万条指令数,因此MIPS值越高,表示处理器在单位时间内执行的指令越多,性能越高。

MIPS: 百万条指令每秒(Millions of Instructions Per Second)

不考虑:计算机之间ISA的差异、指令之间的复杂性差异。

(在一个特定的 CPU 上,不同的程序的 CPI 是不同的)

然而,需要注意的是,MIPS并不是唯一的性能指标,它只关注处理器执行指令的速度,而忽略了其他因素,如处理器的微架构、流水线深度、缓存层次结构、并行度等对性能的影响。因此,在实际应用中,综合考虑多个性能指标,如 IPC(Instructions Per Cycle)、CPI(Cycles Per Instruction)、时钟频率、功耗等,可以更全面地评估处理器的性能。

📌 [ 笔者 ] 王亦优

📃 [ 更新 ] 2022.3.

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,

本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 C++reference[EB/OL]. []. http://www.cplusplus.com/reference/. Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. 比特科技. Linux[EB/OL]. 2021[2021.8.31 xi |