2022王道计组 chap1计算机系统概述

1.1 计算机发展历程

本节思维导图

知识点

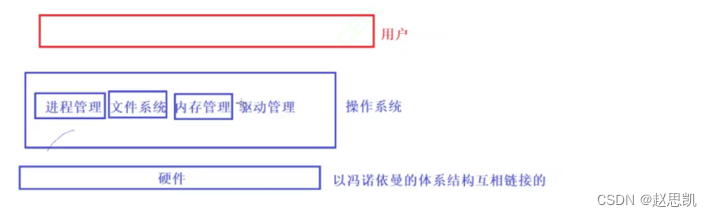

[计算机系统]

-

计算机系统 = 硬件 + 软件

- 计算机性能的好坏取决于“软”“硬”件功能的总和

- 硬件:计算机的实体,如主机、外设等

- 发展变化:见思维导图

- 软件:由具有各类特殊功能的程序组成

- 系统软件

- 用来管理整个计算机系统

- 应用软件

- 按任务需要编制成的各种程序

- 系统软件

- 硬件:计算机的实体,如主机、外设等

- 计算机性能的好坏取决于“软”“硬”件功能的总和

-

发展趋势

- 微型计算机

- 向着更微型化、网络化、高性能、多用途方向发展

- 巨型机

- 向着更巨型化、超高速、并行处理、智能化方向发展

- 微型计算机

重点总结

一些word转markdown的教程和工具

一键!将 Word 转换为 Markdown - 连玉君的文章 - 知乎 https://zhuanlan.zhihu.com/p/30891168

https://blog.csdn.net/weixin_43314519/article/details/106766817

https://www.52txr.cn/2021/md2word.html

https://products.aspose.app/words/conversion

1.2 计算机系统的层次结构

本节思维导图

知识点

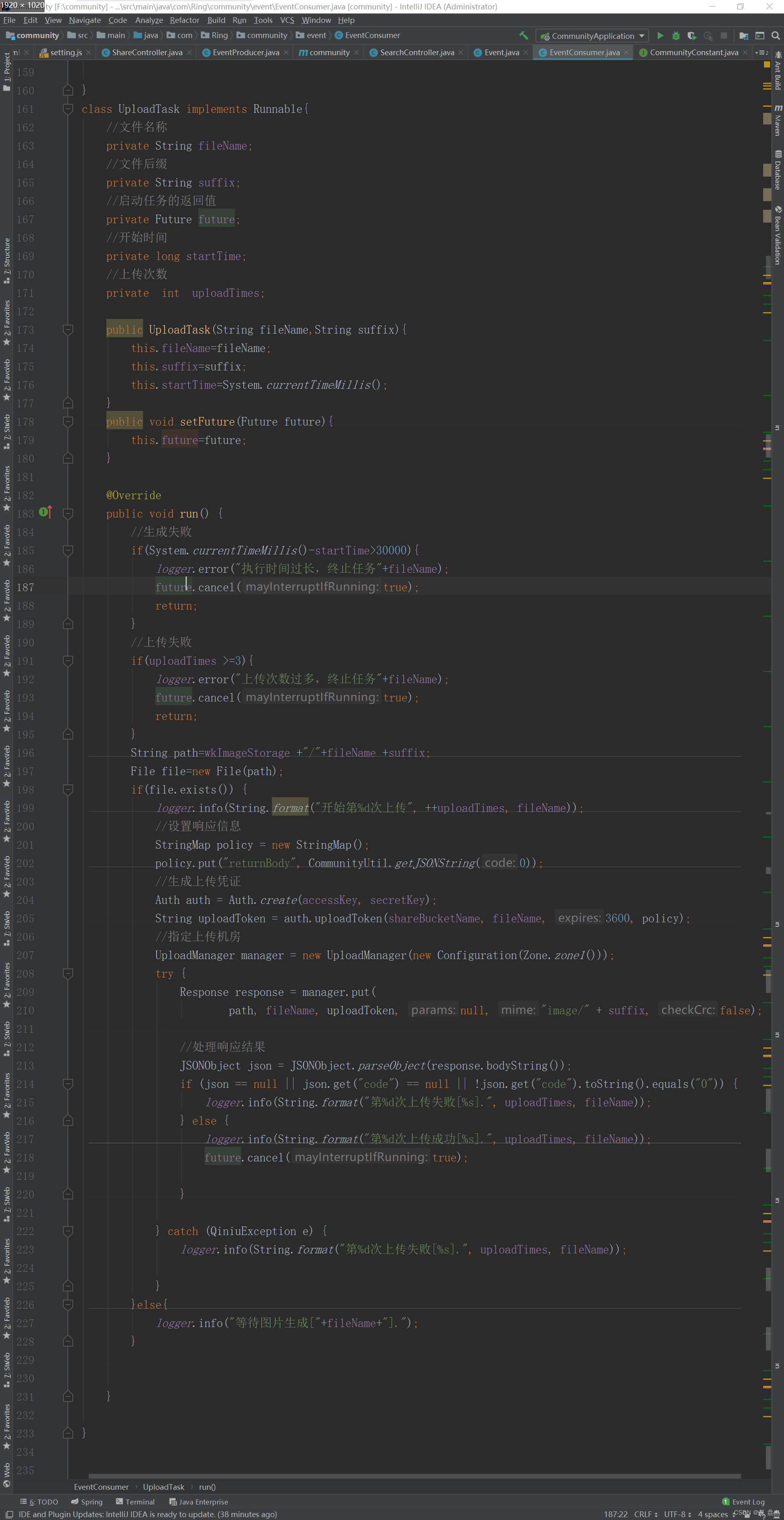

[计算机硬件的基本组成]

早期冯诺依曼机

-

“存储程序”概念

-

将指令以二进制代码的形式事先输入计算机的主存储器,然后按其在存储器中的首地址执行程序的第一条指令,以后就按该程序的规定顺序执行其他指令,直至程序执行结束。

-

冯诺依曼机硬件结构

-

特点

-

由五大部件组成

-

指令和数据以同等地位存于存储器,可按地址寻访

-

指令和数据用二进制表示

-

指令由操作码和地址码组成

-

“存储程序”

-

以运算器为中心

冯诺依曼结构中,数据传送都必须经过运算器

-

这样会导致运算效率降低(本来是可以直接放到存储器里面的,非要经过职能主要是对数据做运算的运算器,就加重了运算器的负担,运算效率就变低了)

-

打个比方

-

采购部门明明可以直接放入仓库,

-

销售部门明明可以从仓库取货,但是非多了一个中间步骤

-

-

-

-

思维导图

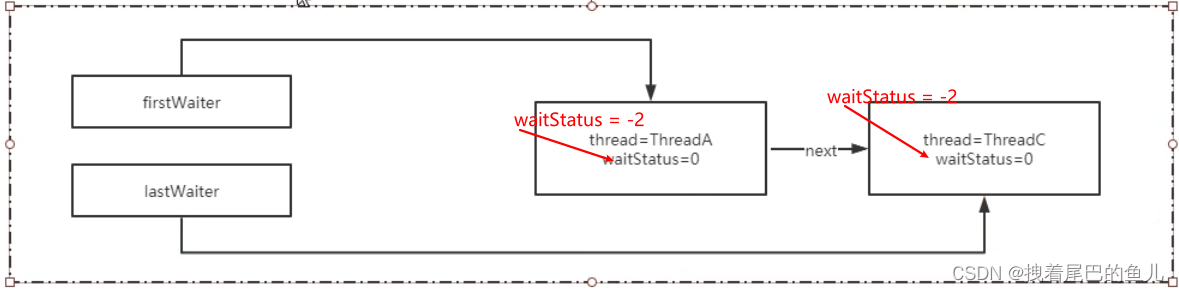

现代计算机结构

-

硬件结构框图

-

实线:数据线 虚线:控制线和反馈线

-

-

简化结构框图

-

实线:数据线 虚线:控制线和反馈线

-

CPU = 控制器 + 运算器

-

[各硬部件]

主存储器的基本组成

存储体

- 存储体会分成很多个存储单元,每一个存储单元会存放一串二进制代码

- 存储单元由存储元构成,存储元是存储二进制的电子元件,由电容构成,每个存储元可存1bit

MAR 地址寄存器

- MAR的位数反映了存储单元的个数

- Eg

- MAR = 4位,总共有2的4次方个存储单元

- Eg

MDR 数据寄存器

- MDR位数 = 存储字长

- Eg

- MDR = 16位,则每个存储单元可存放16bit,1个字(word)= 16bit

- Eg

运算器的基本组成

-

由核心部件算术逻辑单元**ALU(arithmetic and logic unit)**和用于存放数据的寄存器组成

-

ALU

- 通过内部复杂的电路实现算术运算和逻辑运算

-

存放数据的寄存器有

- ACC(accumulator):累加器,用于存放操作数或运算结果

- MQ(mutiple-quotient register):乘商寄存器,在乘除运算时,用于存放操作数或运算结果

- X:通用寄存器,用于存放操作数

-

进行各运算时各寄存器的作用

加 减 乘 除 ACC 被加数、和 被减数、差 乘积高位 被除数、余数 MQ 乘数、乘积低位 商 X 加数 减数 被乘数 除数

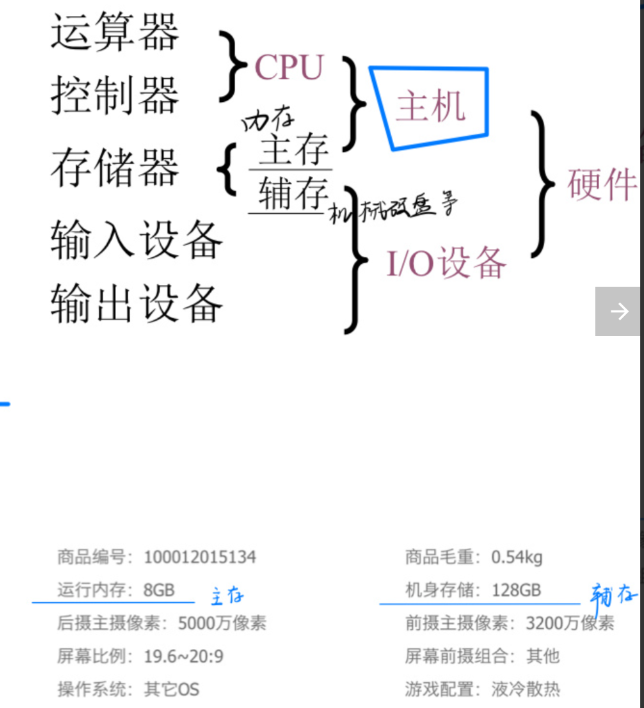

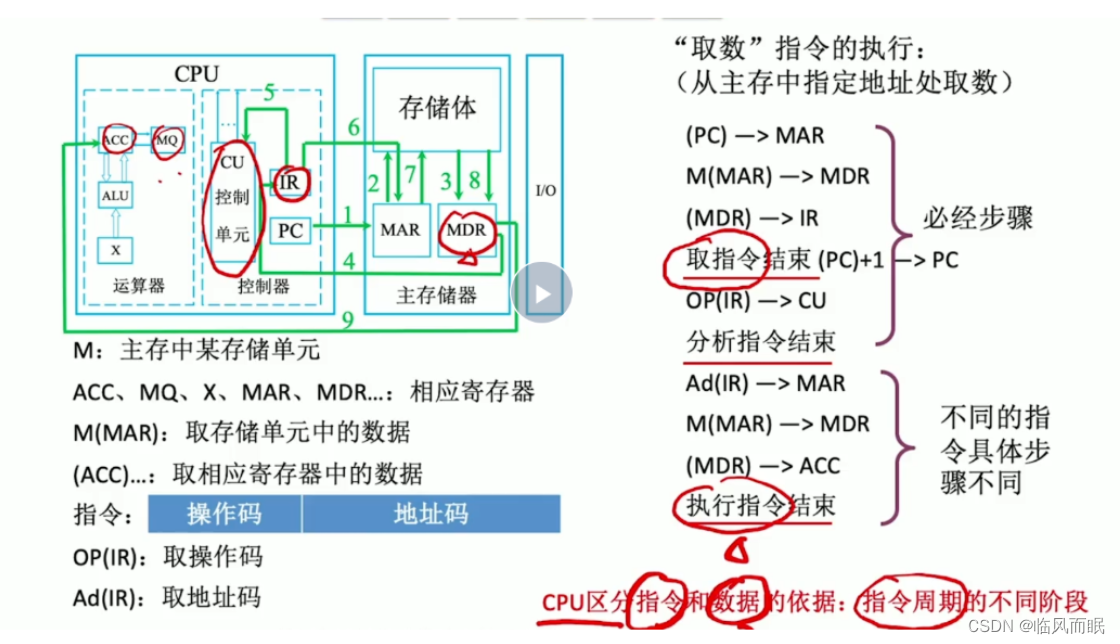

控制器的基本组成

-

三个部件

- CU(control unit):控制单元,分析指令,给出控制信号

- 控制器的核心部件

- IR(instruction register):指令寄存器,存放当前执行的指令

- PC(program counter):程序计数器,存放下一条指令地址,有自动加1功能

- CU(control unit):控制单元,分析指令,给出控制信号

-

在计算机完成一条指令的过程中,首先要进行取指令,会根据PC所记录的指令地址,从内存中取出指令放入IR中,CU便可分析该指令的作用,分析完后,CU就会控制其他部件来配合指令的具体执行

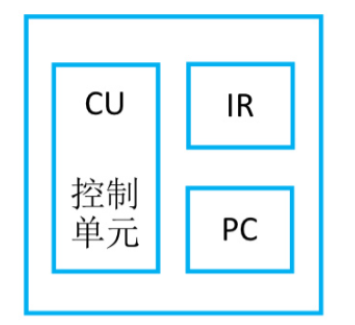

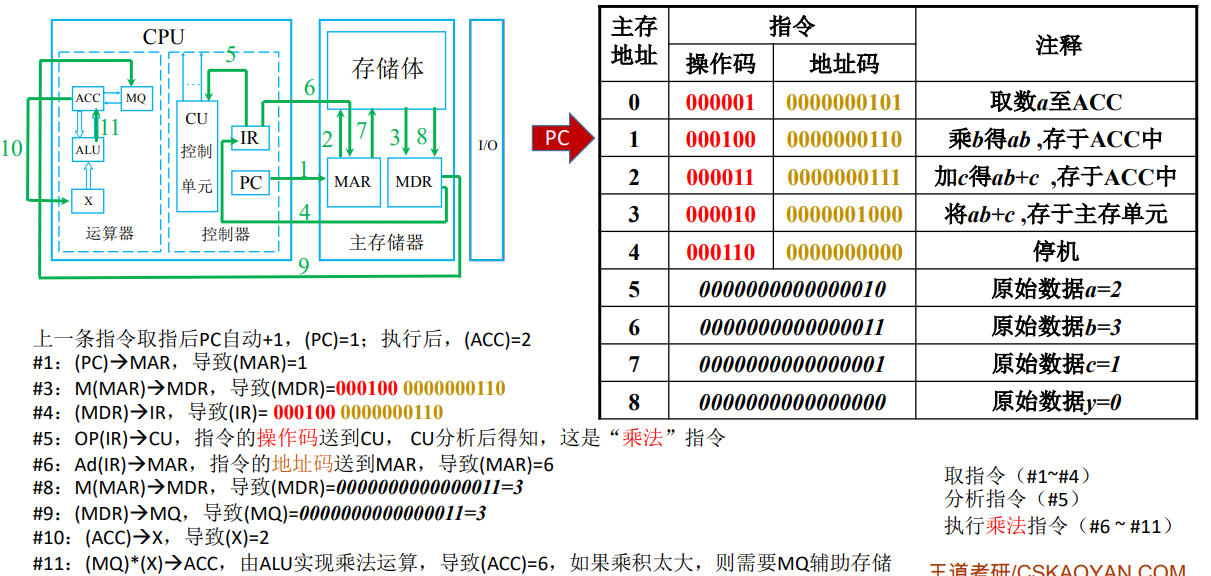

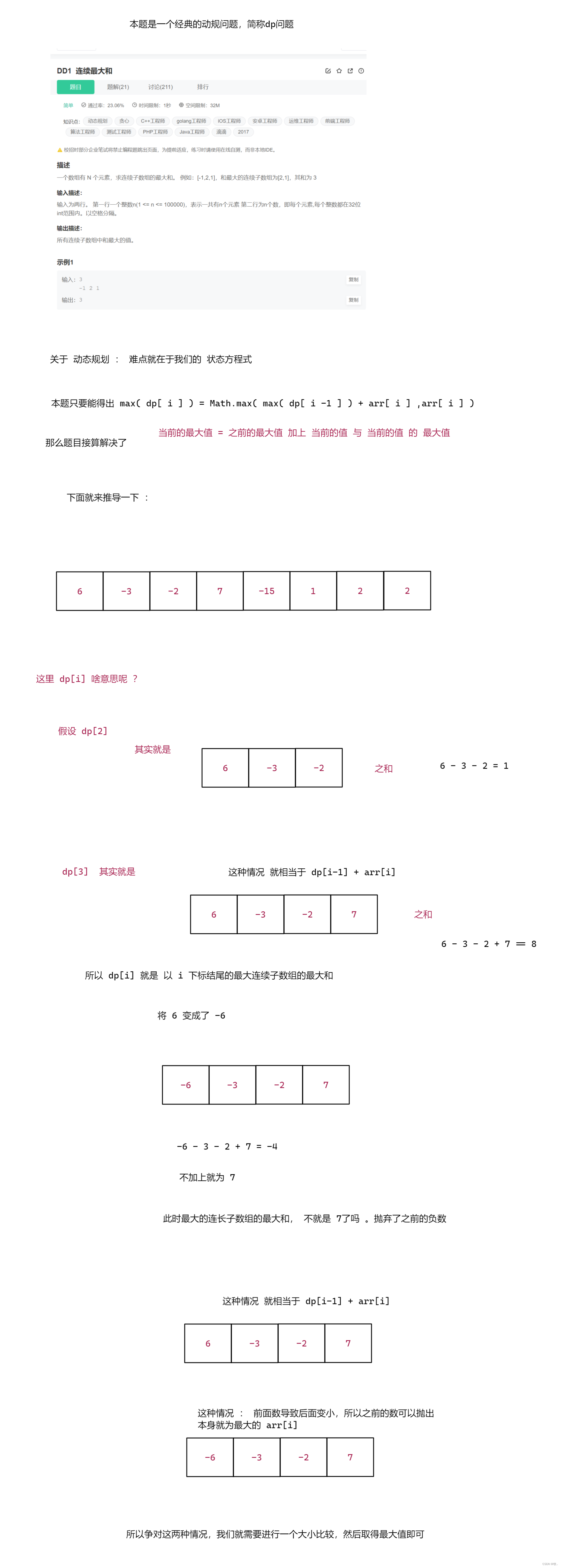

[计算机工作过程]

下面主要树立大局观

-

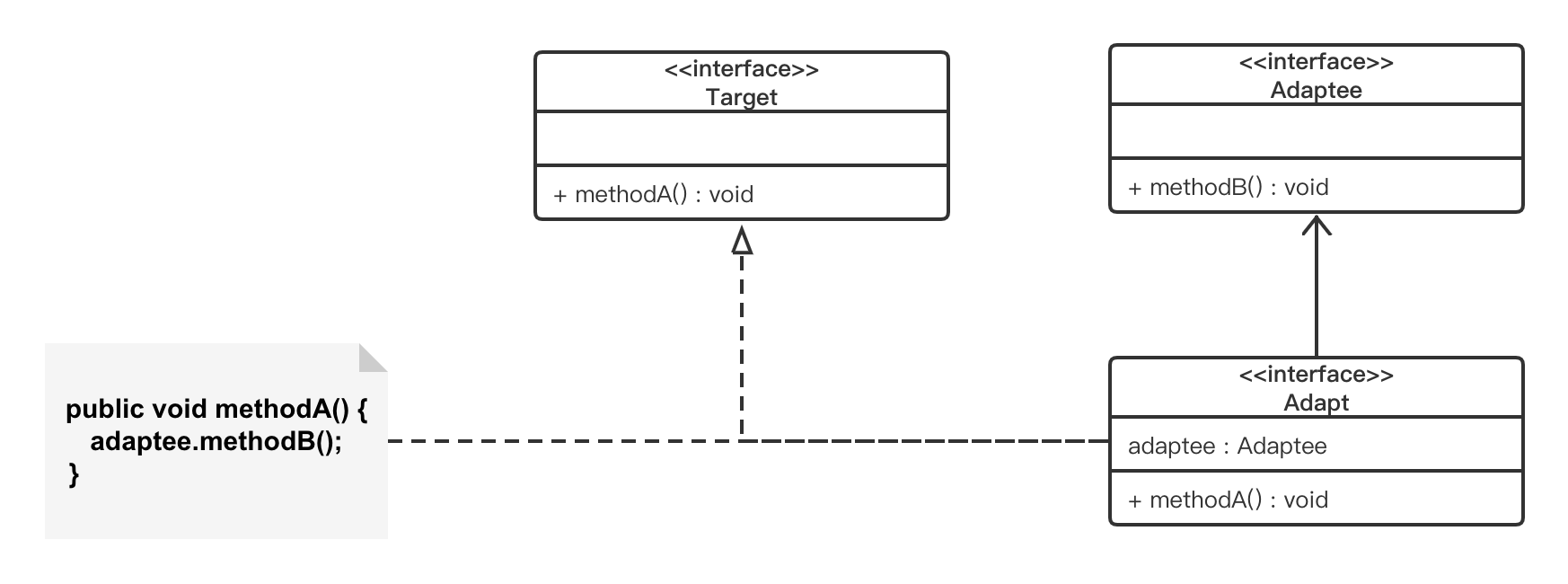

例子:这段C语言代码是如何跑起来的

-

int a = 2, b = 3, c = 1, y = 0; int main() { y = a * b + c; } -

高级语言会经过一系列操作被翻译成能被读懂的机器语言,同时会把这段程序装入主存,在主存中就是下面这个样子

-

先来看第一步取数 a 至 ACC 发生了什么

-

第二步 乘b得ab,存于ACC中

-

第三步 加c得ab+c,存于ACC中

-

第四步 将ab+c,存于主存单元

-

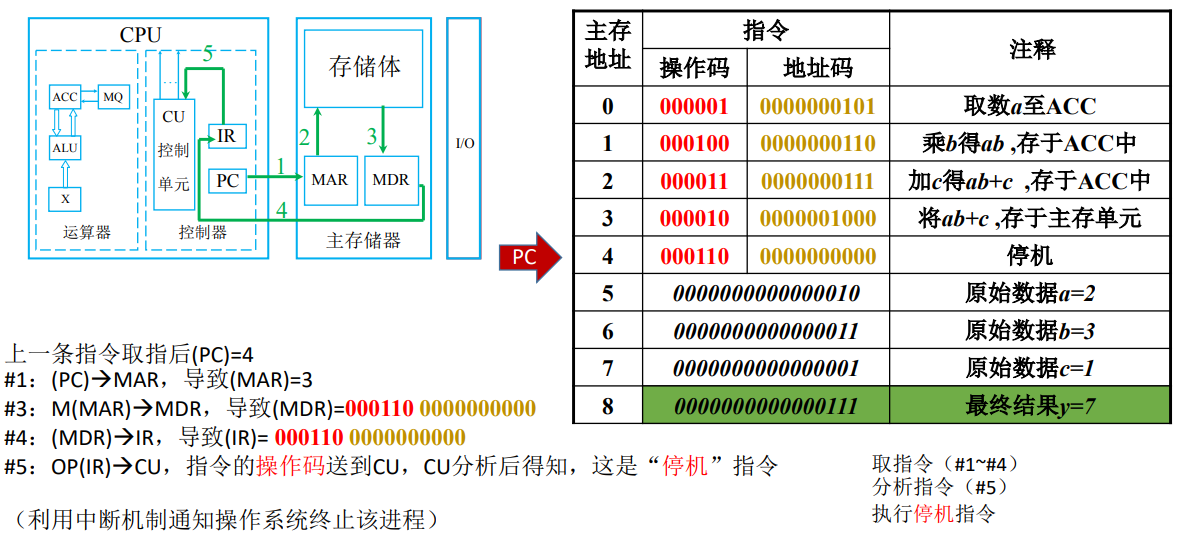

第五步 停机

-

-

总结

-

关于cpu区分指令和数据的依据 这句话:

比如说,取值阶段 , MDR是把整个指令放入CPU中的IR;执行指令阶段 , MDR是把数据放入运算器中的ACC或MQ或其他

-

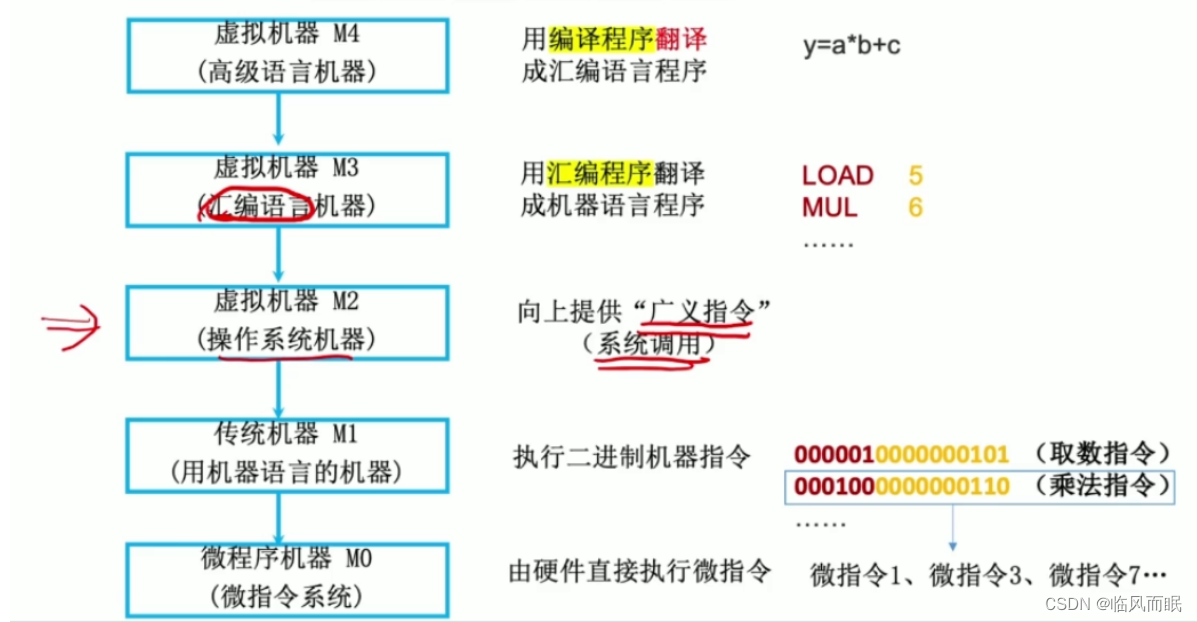

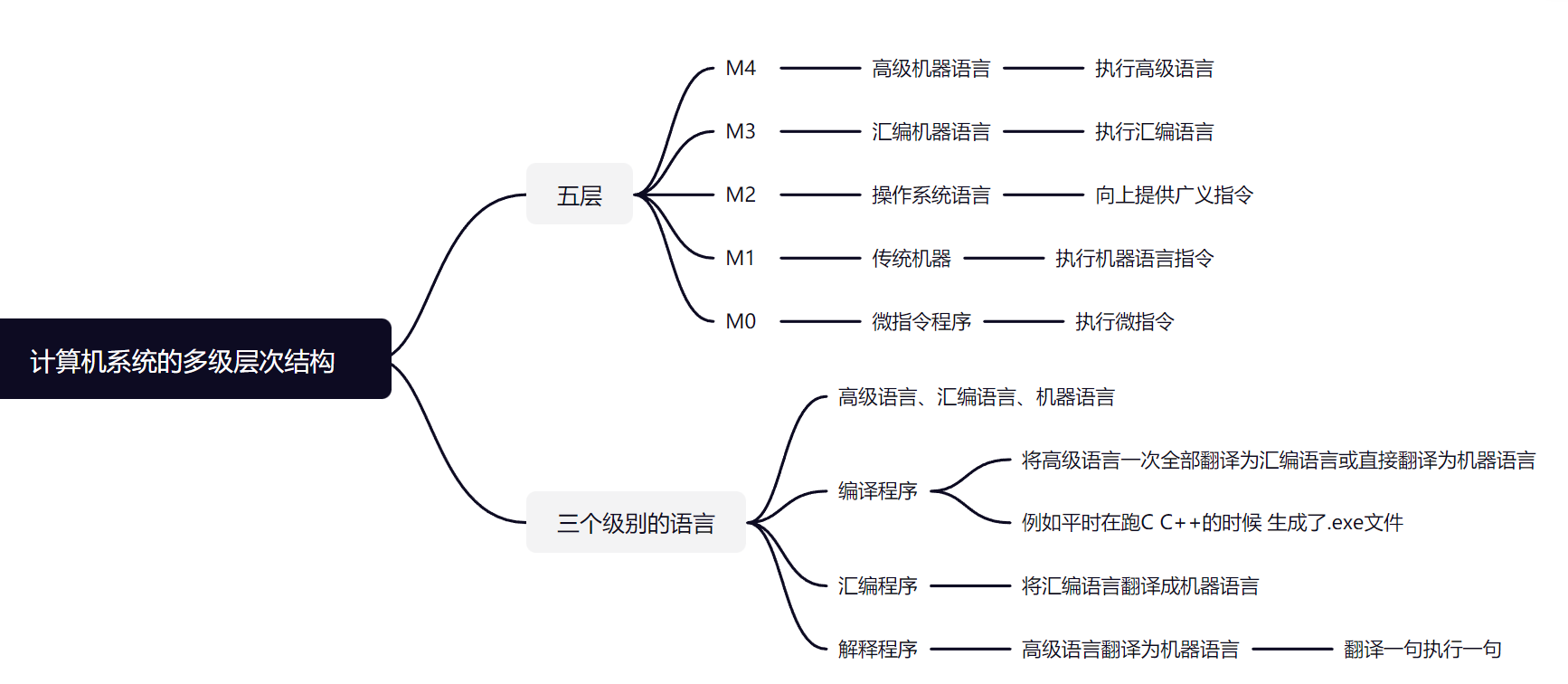

[计算机系统的多级层次结构]

机器层次结构

-

下层是上层的基础,上层是下层的扩展

-

其中的微指令可以理解为上面分析计算机工作工程里面每一个步骤里面的小步骤

-

为什么说是

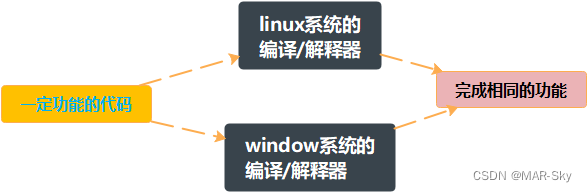

虚拟机器呢- 因为在汇编程序员看来,好像机器是直接识别的汇编语言,但实际上还是要转换为机器语言

- 同样,高级语言也需要先翻译成汇编语言,再翻译成机器语言,实际上机器识别的是机器语言

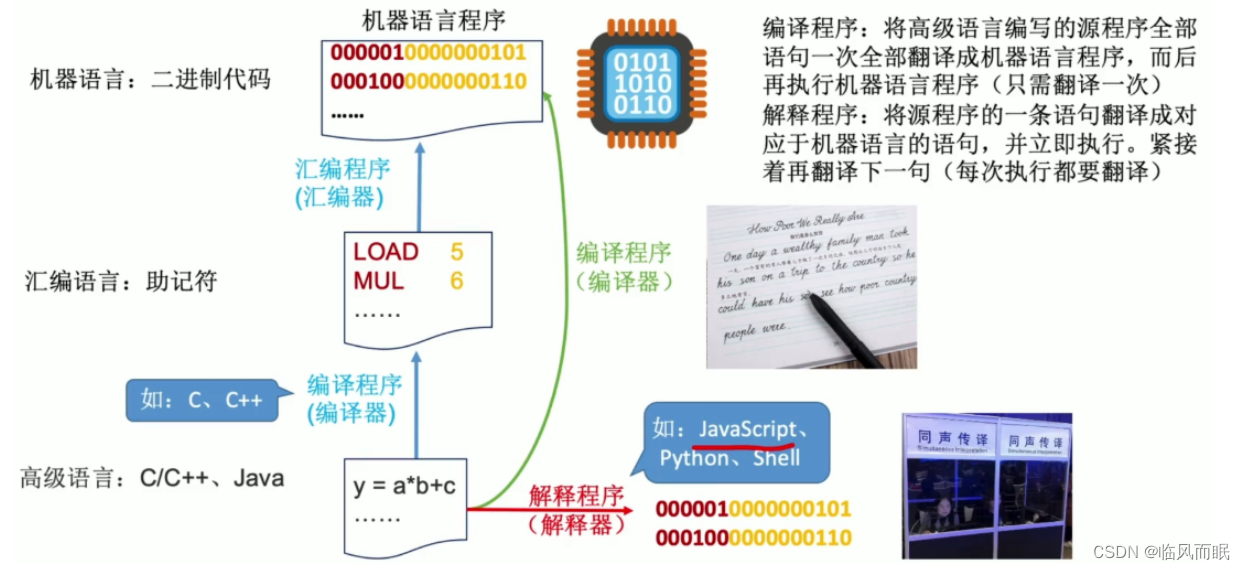

三种级别的语言

-

编译、汇编、解释程序,可统称“翻译程序”

- 都是把高级语言翻译为低级语言

-

解释程序可以看成同声传译

重点总结

-

计算机硬件的基本组成

-

各硬件部件

- 此时再来回顾一下冯诺依曼机的特点,感觉明朗多了

- 计算机由五大部件组成

- 指令和数据以同等地位存于存储器,可按地址寻访

- 指令和数据用二进制表示

- 指令由操作码和地址码组成

- 存储程序

- 以运算器为中心(现在一般以存储器为中心)

- 此时再来回顾一下冯诺依曼机的特点,感觉明朗多了

-

计算机系统的多级层次结构

1.3 计算机的性能指标

本节思维导图

知识点

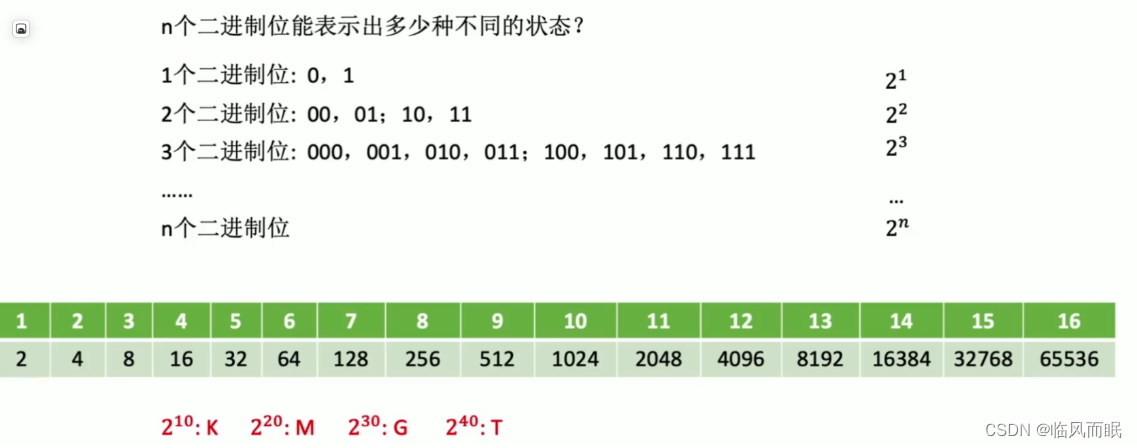

- 二进制数基础知识

[存储器的性能指标]

-

MAR位数

- 反映存储单元的个数(最多支持的存储单元个数,实际可能会偏小)

-

MDR位数

- MDR位数=存储字长=每个存储单元的大小

-

总容量 = 存储单元个数×存储字长 bit = 存储单元个数×存储字长/8 Byte

-

1Byte = 8 bit

-

例

-

MAR为32位,MDR为8位,

则总容量 = 2 32 × 8 b i t = 4 G B 2^{32} \times 8bit = 4GB 232×8bit=4GB

-

-

[CPU的性能指标]

突然发现自己忘了啥叫脉冲…

https://www.bilibili.com/video/BV1oJ411c7jX?spm_id_from=333.337.search-card.all.click&vd_source=0e8431ba6fd78bb2215c36307a75ac1a

-

CPU时钟周期

讲了这么多年的CPU频率,到底是什么? - 超能网的文章 - 知乎 https://zhuanlan.zhihu.com/p/30582175

机器内部的时钟周期就是机器世界的时间单位。比如我们现实世界的时间单位是分钟、秒、毫秒等。只不过机器世界就一个时间单位叫时钟周期,而为了人类更方便理解这个指标就用现实世界的秒来表示,即每秒多少时钟周期,即多少HZ。

-

CPU主频(时钟频率)

-

CPU内数字脉冲信号震荡的频率

-

等于 CPU时钟周期的倒数

-

单位:赫兹,Hz

-

例

- 主频为10Hz:每秒有10个脉冲信号

-

-

CPI(Clock cycle Per Instruction)

- 执行一条指令所需的时钟周期数

- 不同的指令,CPU不同,甚至相同的指令,CPU也可能有变化

-

执行一条指令的耗时 = CPI × CPU时钟周期

执行一条指令所需的时钟周期数 x CPU时钟周期

-

CPU执行时间(整个程序的耗时)

-

= CPU时钟周期数/主频 = (指令条数×CPI)/主频

-

IPS(Instructions Per Second):每秒执行多少条指令

例如说性能2MIPS:平均每秒可以执行两百万条指令

主频:每秒时钟周期数

平均CPI:平均每个指令需要的时钟周期数

相除就是每秒执行的指令数

或者这样理解:1s/(平均每个指令需要的时钟周期数 x 时钟周期) = 1s/ 1个指令需要的时间 = 1s执行多少条指令 -

浮点运算

[系统整体的性能指标]

-

数据通路带宽

- 数据总线一次所能并行传送信息的位数(各硬件部件通过数据总线传输数据)

-

吞吐量

-

指系统在单位时间内处理请求的数量

它取决于信息能多快地输入内存,CPU能多快地取指令,数据能多快地从内存取出或存入,以及所得结果能多快地从内存送给一台外部设备。这些步骤中的每一步都关系到主存,因此,系统吞吐量主要取决于主存的存取周期

-

-

响应时间

-

指从用户向计算机发送一个请求,到系统对该请求作出相应并获得它所需要的结果的等待时间

通常包括CPU时间(运行一个程序所花费的时间) 与等待时间(用于磁盘访问、存储

器访问、I/O操作、操作系统开销等时间)

-

重点总结

![[Linux] 常用命令--文件操作grep/nl/more/less/head tail/set](https://img-blog.csdnimg.cn/30c1faf3321545a093b9bb5acbca263f.png)