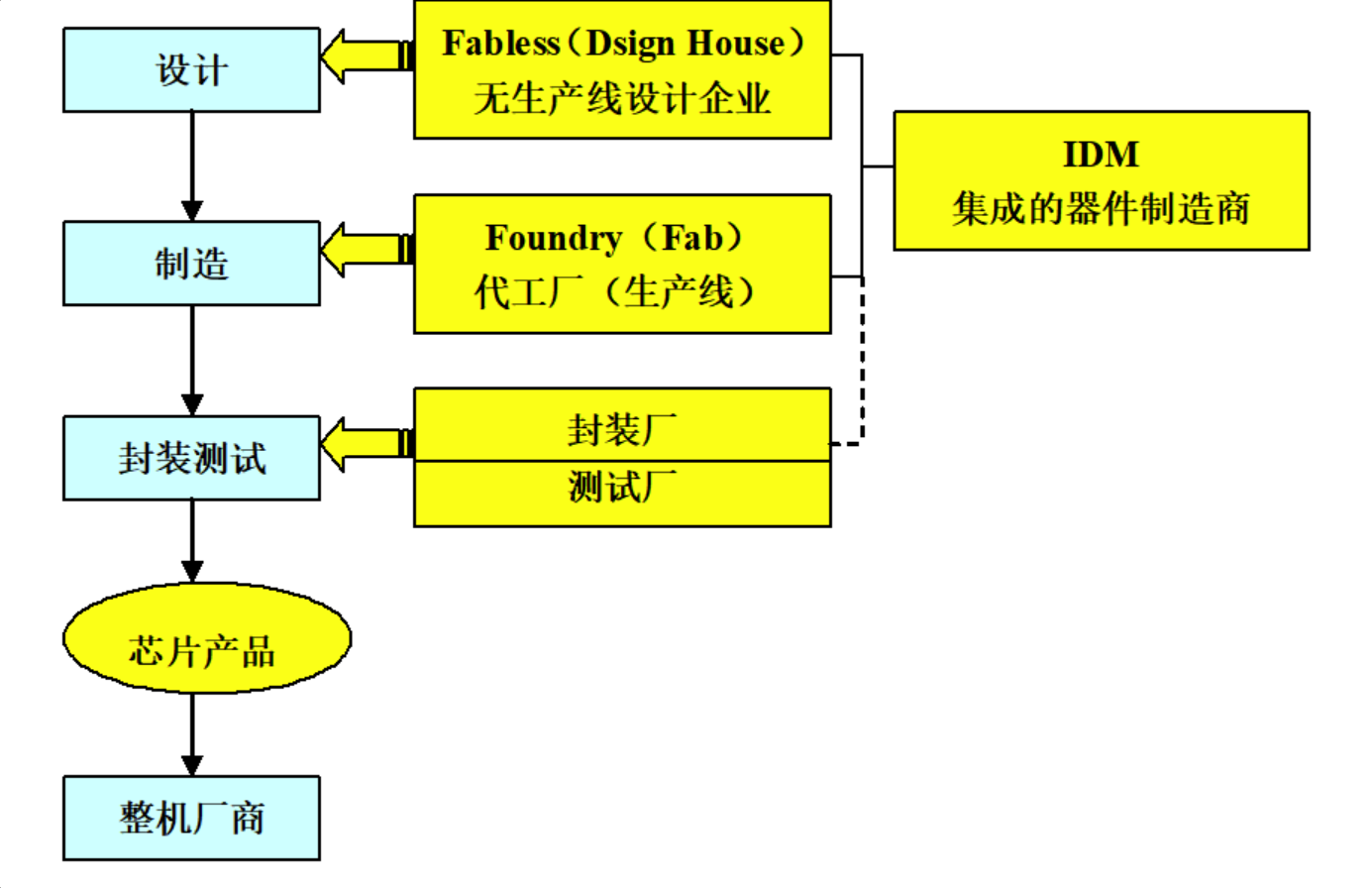

先来看张图,本图体现出了集成电路产业链:设计业、制造业、封测业。

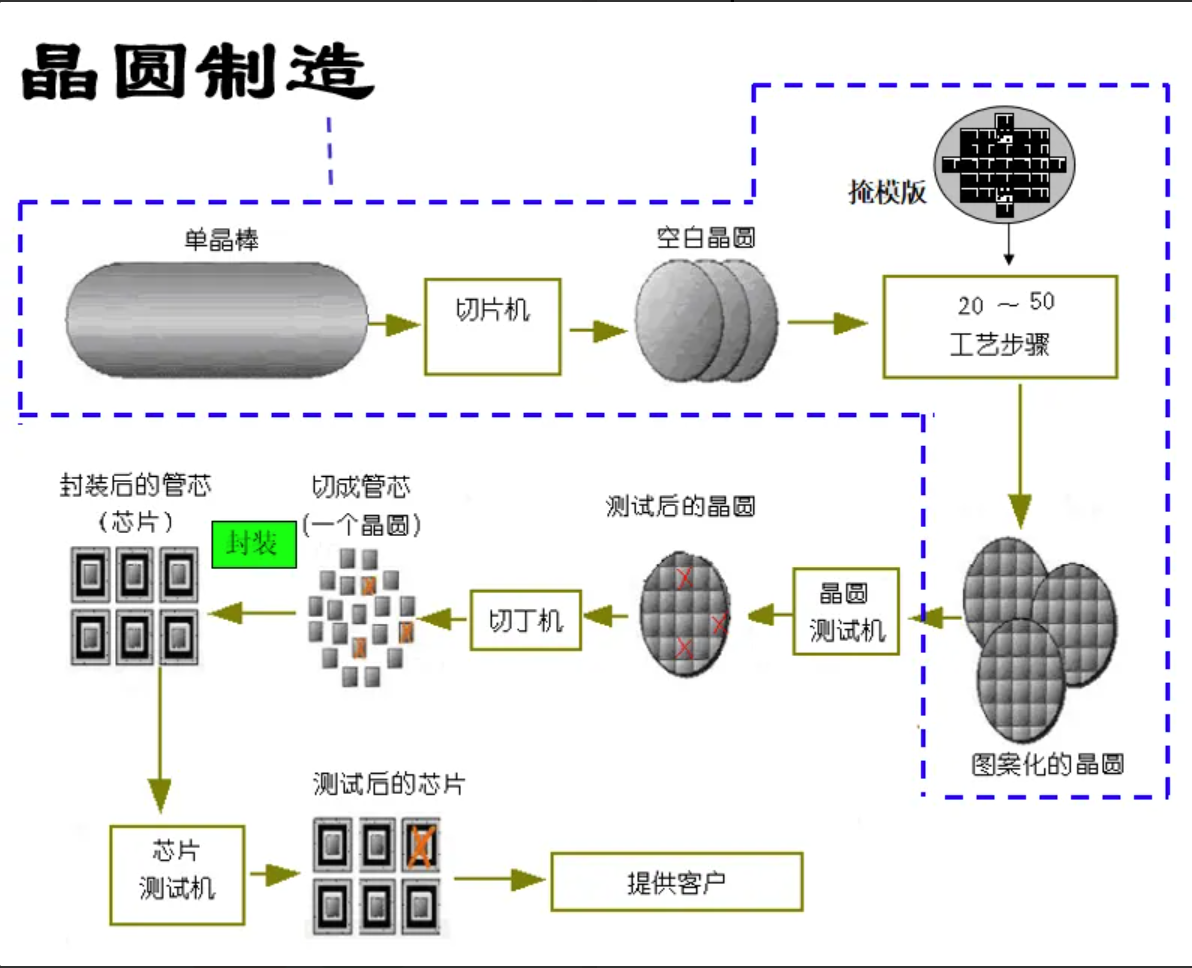

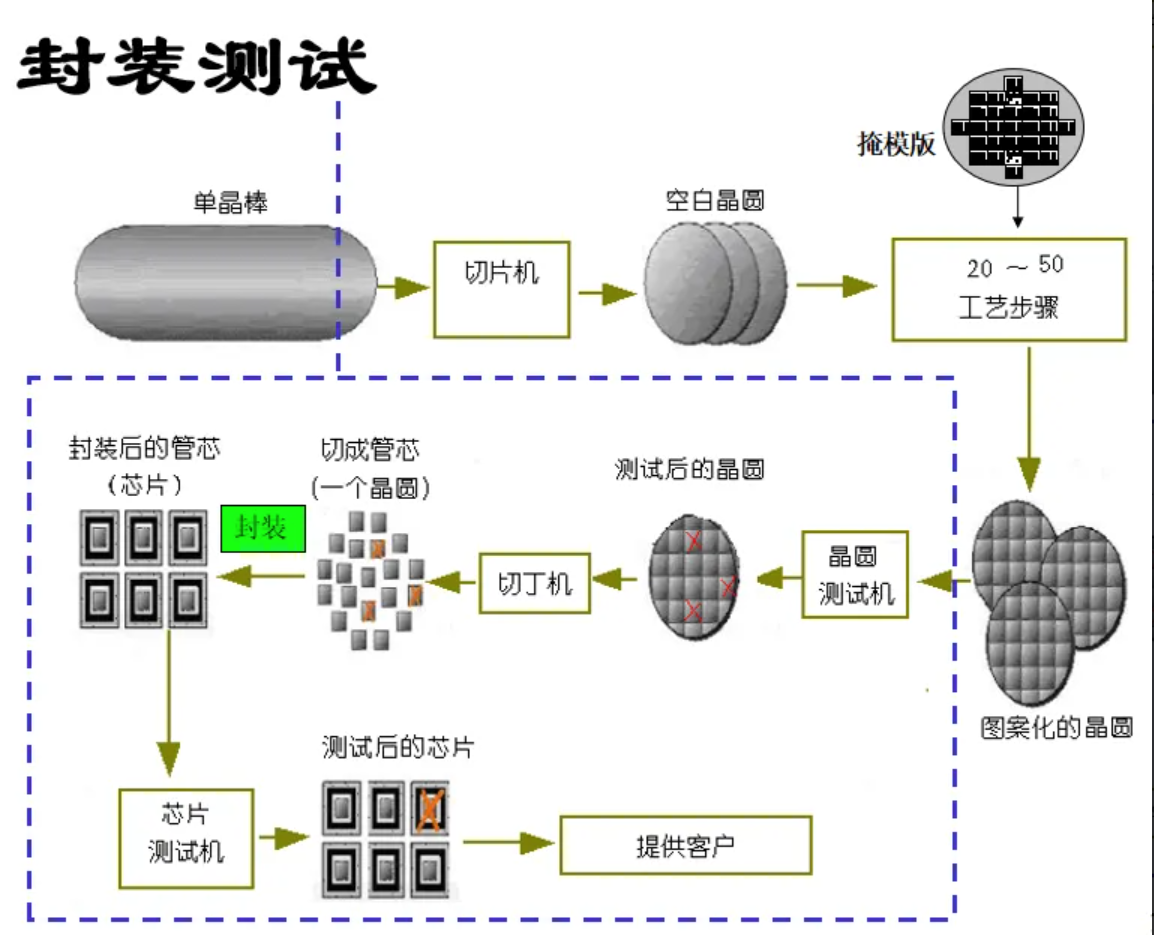

关于制造、封装测试我们看两张图稍作了解即可:

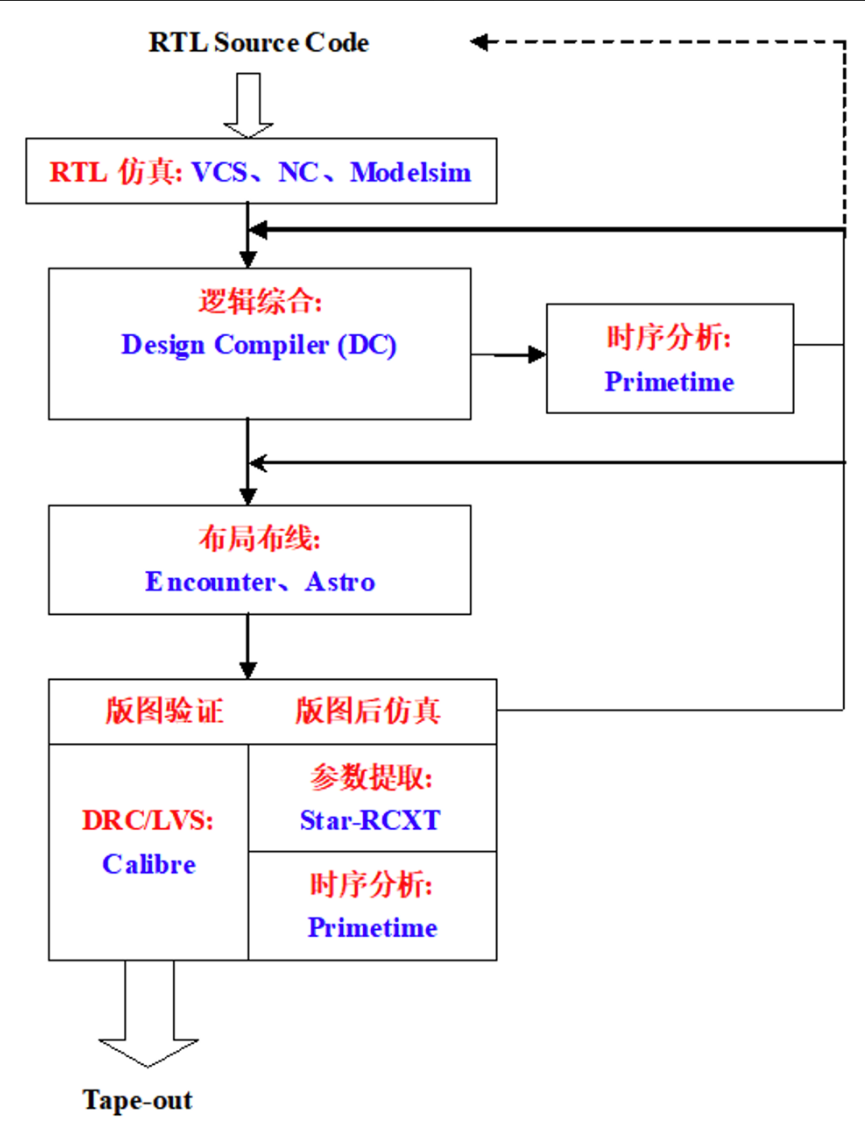

数字IC ASIC设计流程及EDA工具:

(1)了解数字IC设计:在VLSI时代,数字IC设计是VLSI设计的根本所在(更大的规模、更好的性能、更低的功耗、超深亚微米(VDSM)工艺技术:对互连问题的关注)

数字IC设计方法:

层次化:

从高层次的系统抽象描述,逐级向下进行设计/综合、验证,直到物理版图级的低层次描述(系统(功能)级→寄存器传输级(RTL)→门级→电路级→ 物理版图级);

层次化的设计方法使复杂的电子系统简化,并能在不同的设计层次及时发现错误并加以纠正 ;

结构化:

把复杂的系统划分成一些可操作的模块,允许多个设计者同时设计,而且某些模块的可以复用;

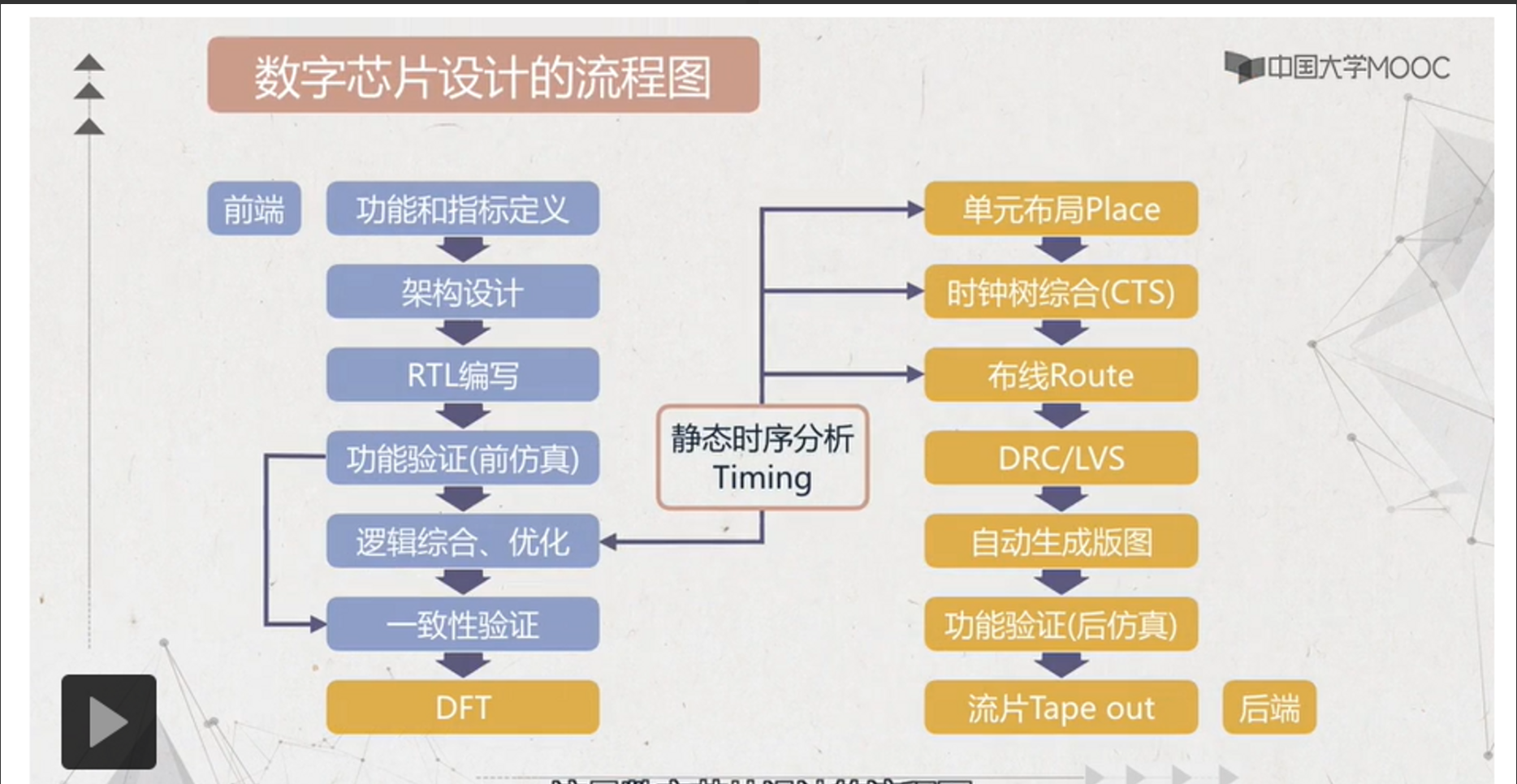

(2)数字IC ASIC设计流程:三阶段(前端设计/功能验证/后端实现)

RTL前端+功能验证(最终得到的是RTL Source Code)

GDSII后端:逻辑综合+后仿真(最终得到的是GDSII文件)

- 第一阶段:数字IC ASIC之 前端设计(RTL设计):

用硬件描述语言HDL(Verilog、VHDL)来描述;描述硬件电路,抽象地表示电路的结构和行为(怎样组成,完成什么功能);

HDL描述的两种方式:

结构描述:若干部件用信号线互连形成一个实体;

行为描述:反映信号的变化、组合和传播行为,特点是信号的延迟和并行性;

HDL的作用:

具有与具体硬件电路无关和与EDA工具平台无关的特性,简化了设计;

支持从系统级到门和器件级的电路描述,并具有在不同设计层次上的仿真/验证机制;

可作为综合工具的输入,支持电路描述由高层向低层的转换;

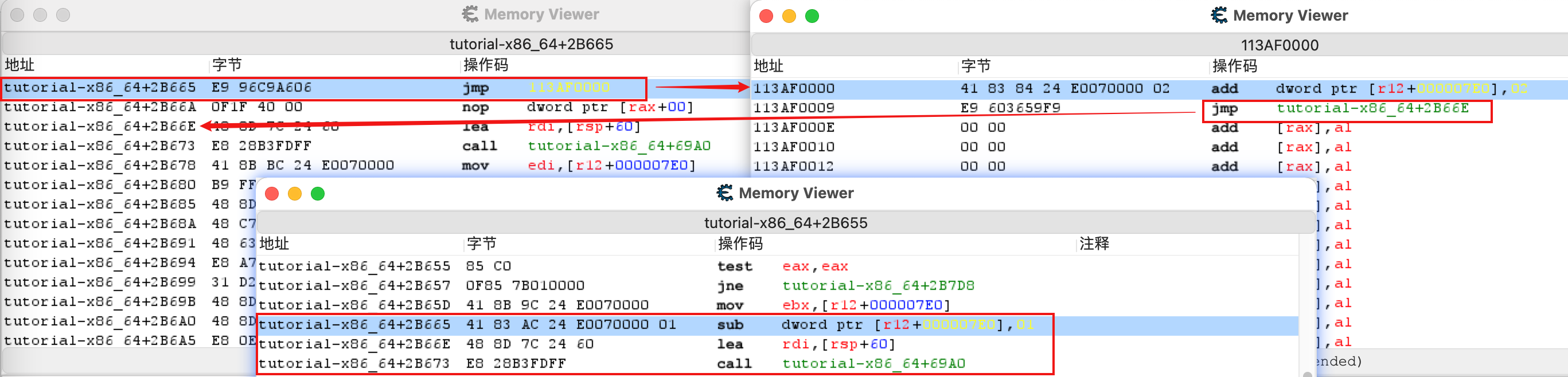

数字ASIC设计中采用的典型EDA工具:

- 第二阶段:数字IC ASIC之 功能验证(前仿真):

检验RTL级的HDL设计是否实现了Spec.需要的功能等;

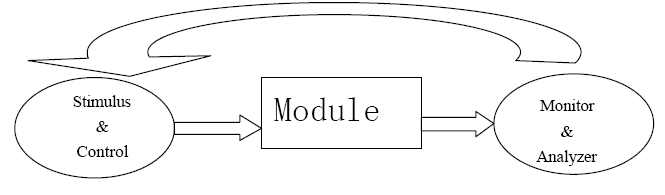

**仿真:**先对设计进行一系列的激励(输入),然后有选择的观察响应(输出)

激励与控制:设置输入端口,输入激励向量;

**响应和分析:**及时监控输出响应信号变化,判断是否正确、合法;

常用的仿真EDA工具:VCS (Synopsys), Modelsim(Mentor), NC(Cadence);

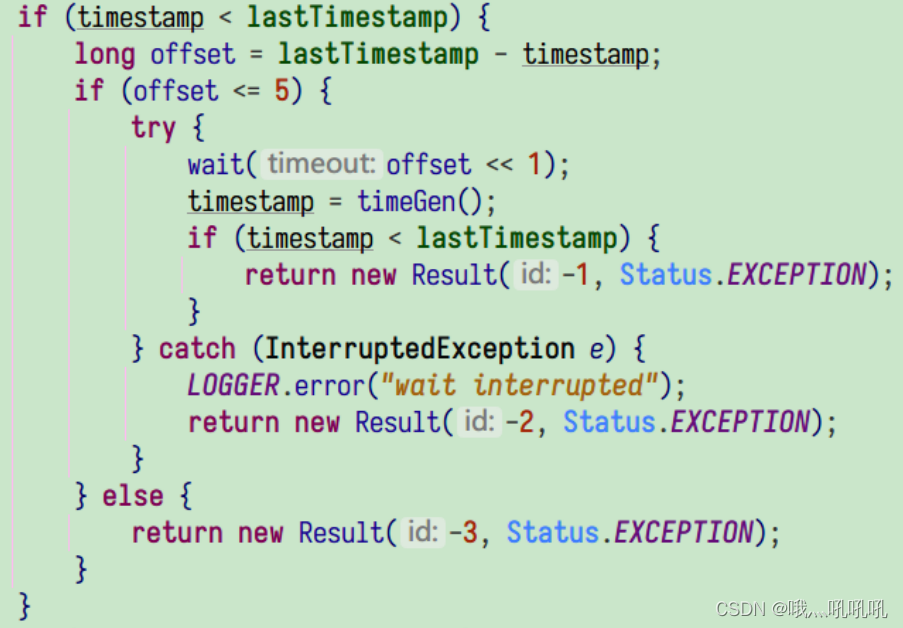

- 第三阶段:数字IC ASIC之 后端实现:(逻辑综合、时序分析、布局布线、版图验证、后仿真)

逻辑综合:

将描述电路的RTL级HDL转换到门级电路网表netlist的过程;根据该电路性能的要求(限制),在一个由制造商提供的包含众多结构、功能、性能均已知的逻辑元件的单元库的支持下,寻找出一个门级逻辑网络结构的最佳实现方案,形成门级电路网表netlist;

![[]](https://img-blog.csdnimg.cn/47f3b301e55d477b9827376dadf0304e.png)

综合EDA工具主要包括三个阶段:转换(Translation)、优化(Optimization)与映射(Mapping)

转换阶段:将RTL用门级逻辑来实现,构成初始的未优化电路。

优化与映射:对已有的初始电路进行分析,去掉电路中的冗余单元,并对不满足限制条件的路径进行优化,然后将优化之后的电路映射到由制造商提供的工艺库上

常用的EDA工具:Design Compiler(Synopsys)

时序分析:

对于VLSI,时序分析一般采用静态时序分析STA(Static Timing Analysis),以验证门级逻辑网络结构netlist的时序是否正确;

STA工具的基本思想: 在netlist中找到关键路径;关键路径是netlist中信号传播时延的最长路径,决定了芯片的最高工作频率;

STA工具可以分为三个基本步骤:

第一是将netlist看成一个拓扑图 ;

第二是时延计算(连线时延 net delay、单元时延 cell delay);

第三是找到关键路径并计算时延,进行判断;

常用的时序验证EDA工具:PrimeTime(Synopsys) ;

布局布线:

将门级电路网表(netlist)实现成版图(layout)

常用的EDA工具:Encounter(Cadence)、Astro (Synopsys)

版图验证:

版图验证包括DRC和LVS;

DRC(Design Rule Check):保证版图的可制造性,保证版图满足芯片制造厂的版图设计规则(Design Rule);

LVS(Layout Versus Schematic):证明版图与门级电路网表netlist的一致性;

常用的EDA工具:Mentor的Calibre,Synopsys的Hercules;

后仿真:

后仿真是保证版图是否满足时序的要求,在后仿真之前首先要进行参数提取,提取版图的连线时延信息(RC Extract),后仿真STA等;

常用的参数提取EDA工具:Synopsys的StarRCXT

常用的后仿真STA EDA工具:Synopsys的PrimeTime

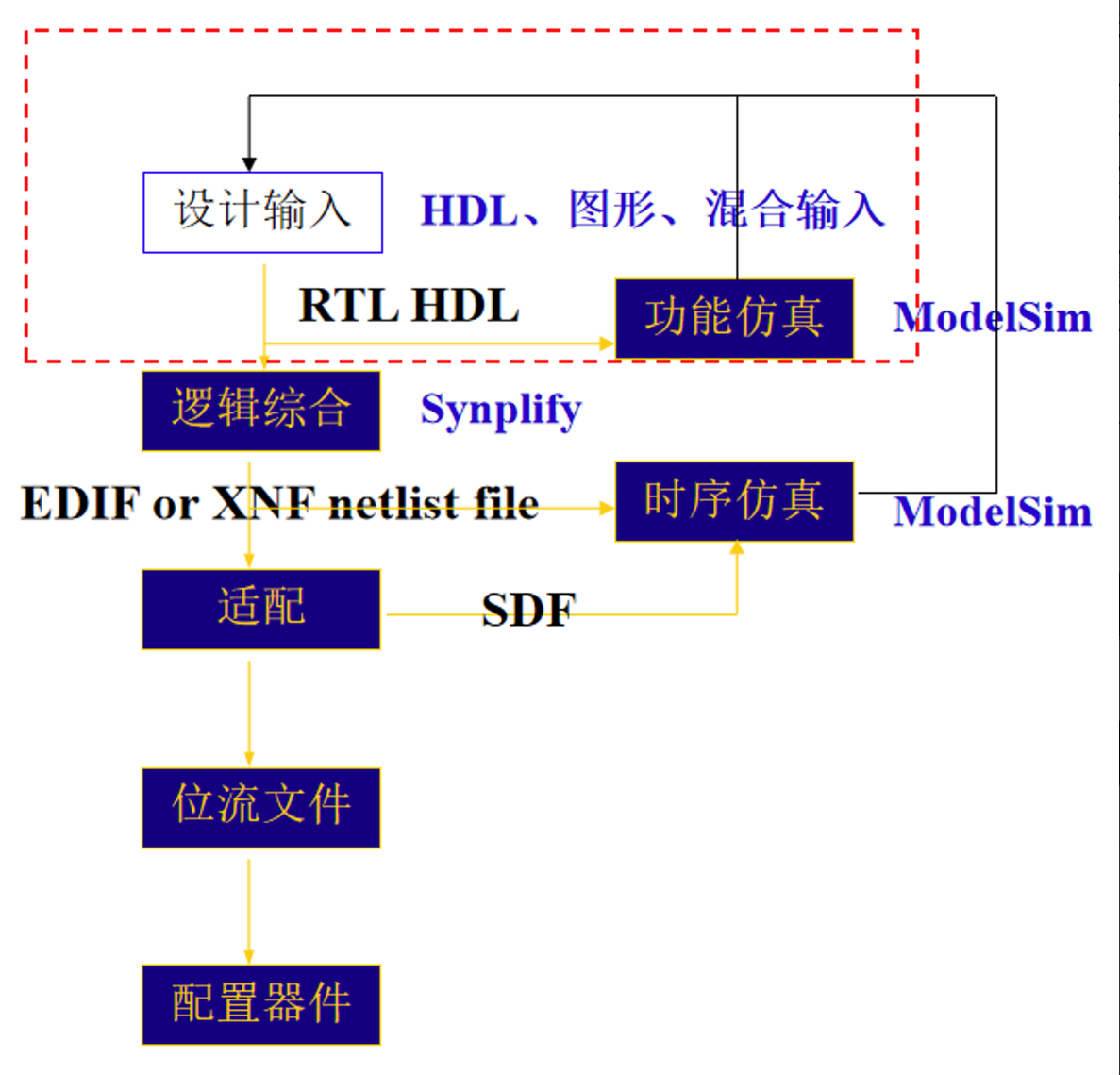

4.FPGA/CPLD设计流程及EDA工具:

仿真、综合与适配:

(1)功能仿真:HDL设计是否实现Spec.功能要求;

采用的EDA工具:Modelsim(Mentor);

(2)逻辑综合:HDL转化为FPGA门级网表;

采用的EDA工具:Synplify(Synplicity)、Precision(Mentor);

(3)时序仿真:不同于前面提到的静态时序仿真STA,是动态时序仿真;

采用的工具:Modelsim;

(4)适配:也称结构综合或FPGA布局布线,是将由综合产生的网表文件配置于指定的目标器件(FPGA/CPLD)中,产生最终的下载文件,如JEDEC、Jam格式的文件。

FPGA/CPLD 器件及其开发工具:

FPGA/CPLD 器件提供商:

Altera和Xilinx;

FPGA/CPLD 开发的EDA工具一般由器件生产厂家提供,但器件厂家只开发集成开发环境IDE和与器件密切相关的适配工具,功能仿真和综合工具实际是由第三方EDA软件开发商公司提供;

Altera -Quartus II (前身为Maxplus II )

Xilinx -ISE Vivado

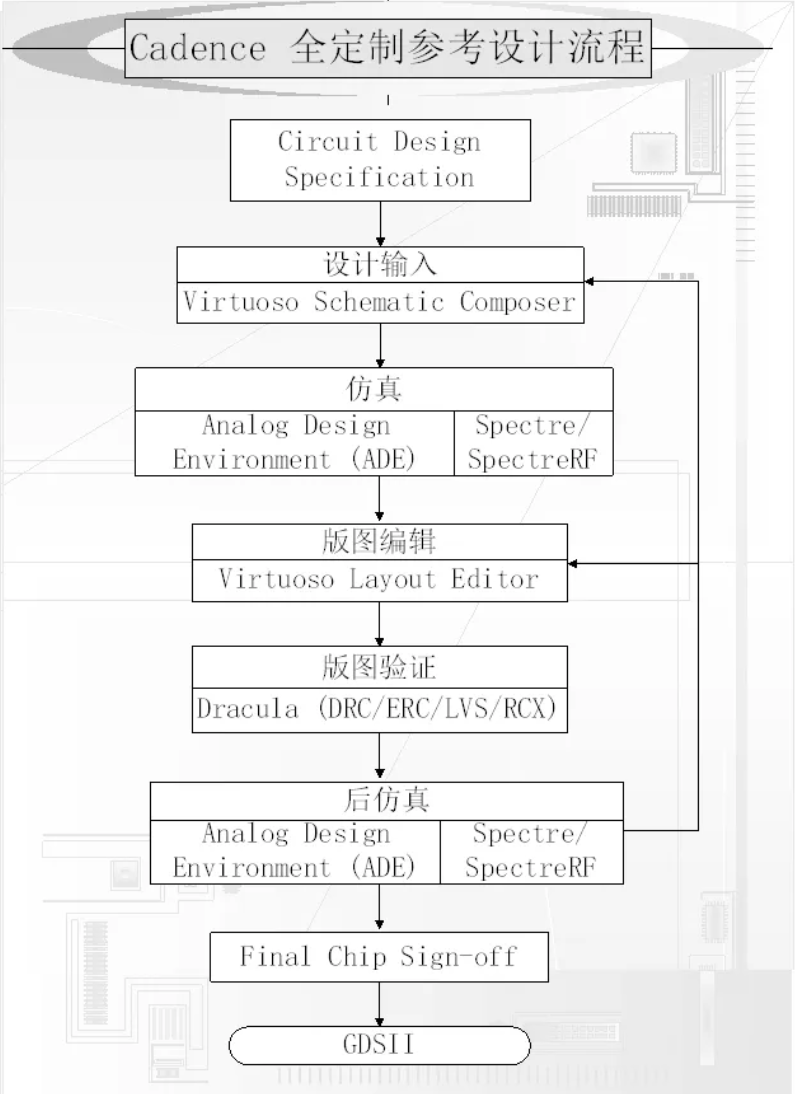

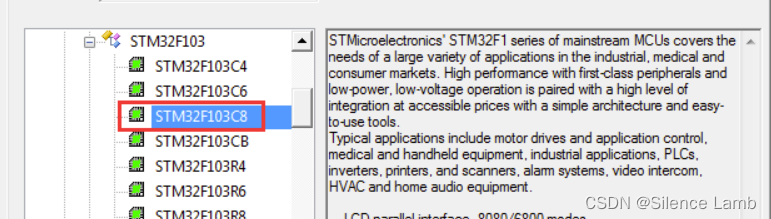

5.模拟IC设计流程及EDA工具:

模拟IC设计流程是全定制设计流程;

(1)电路图编辑

常用的工具:Cadence Virtuoso – Schamatic Composer

(2)电路仿真(电路模拟):俗称 SPICE 仿真

常用的工具: Synopsys HSPICE,Cadence Spectre

(3)版图编辑

常用的工具: Cadence Virtuoso – Layout Editor(LE)

(4)版图验证与后仿真

DRC/ LVS: DRC保证版图满足芯片制造厂的设计规则 / LVS证明版图与网表的一致性;常用的DRC/LVS EDA工具:Mentor Calibre、 Synopsys Hercules;

参数提取:提取版图的连线时延信息(RC Extract);常用的参数提取EDA工具:Synopsys StarRCXT;

版图后仿真:SPICE;

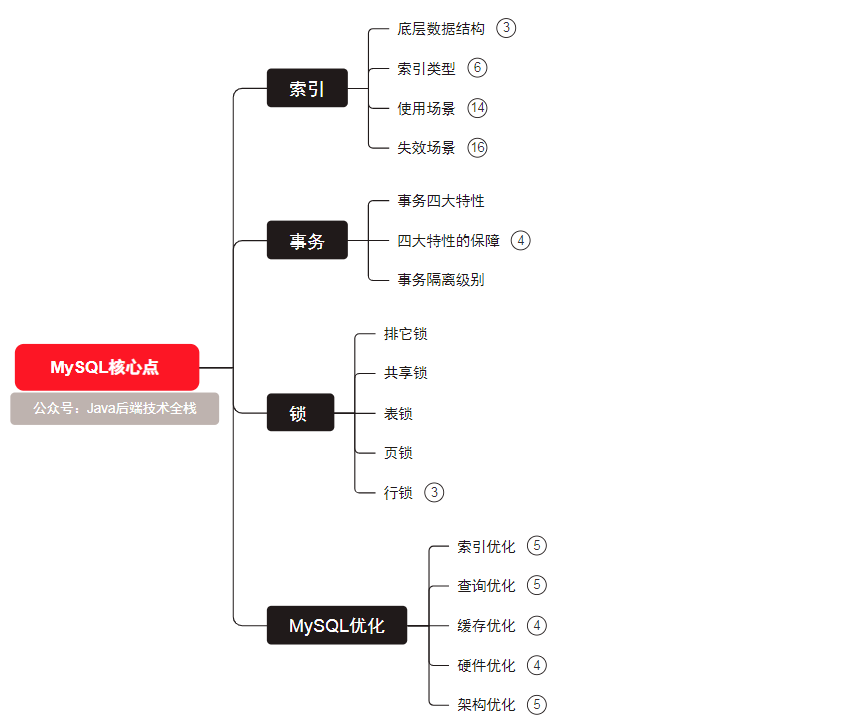

模拟典型设计流程及EDA工具:

![[HAOI2011]Problem b(莫比乌斯反演)](https://img-blog.csdnimg.cn/8894d21b08bb478c8b4b1a617f0eaaa0.png)