目录

一:触发器

二:寄存器(register)

缓冲寄存器

三态输出电路(只看标红的即可)数据总线上很常用

考试会问你触发器,寄存器,存储器是什么关系你知道就行。这个简答题在存储器笔记那张存储器笔记,触发器_小萌新上大分的博客-CSDN博客

三态指的是什么态

一:触发器

触发器你只需要知道,一个触发器可以存储一位数据

二:寄存器(register)

寄存器是由触发器组成的。一个触发器就是一个一位寄存器。由多个触发器可以组成一个多位寄存器。

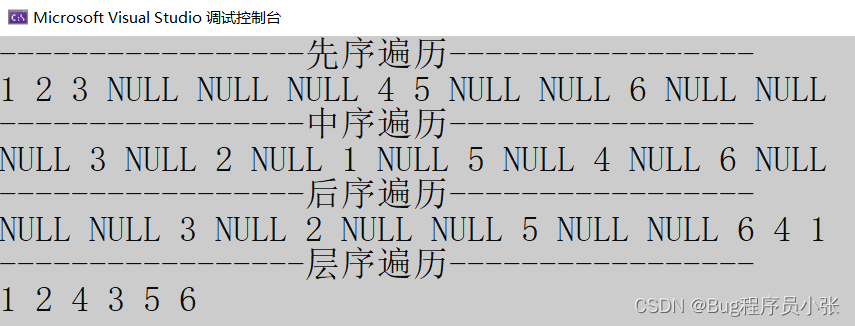

缓冲寄存器 (由D触发器组成)

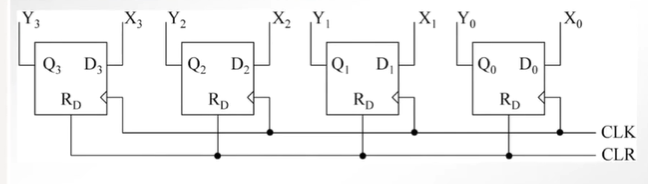

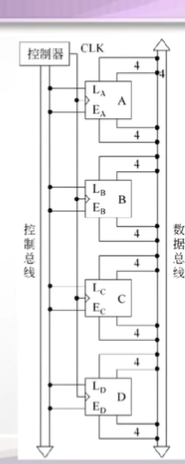

缓冲寄存器用于暂存某个数据,以便在适当的时间节拍和给定的计算步骤将数据输入或输出到其他记忆元件中去。4位缓冲寄存器电路如图

x是输入,y是输出

CLK:接外部时钟,如给出方波

CLR:清零

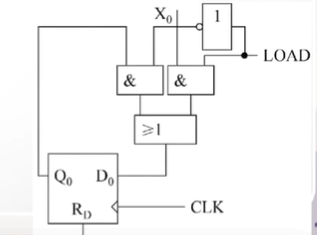

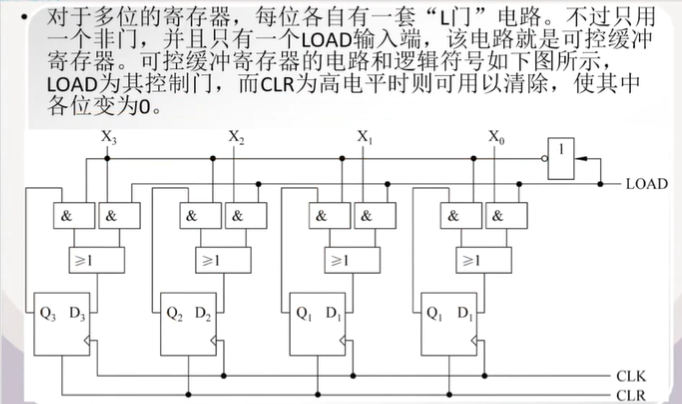

需要一个可控的门电路(决定新数据是否进入,如果LOAD给定零,信息会在自己中转圈数据就保留了,如果LOAD给定1新的数据X就会进来,把旧的数据替换掉)

最终的图

三态输出电路(只看标红的即可)数据总线上很常用

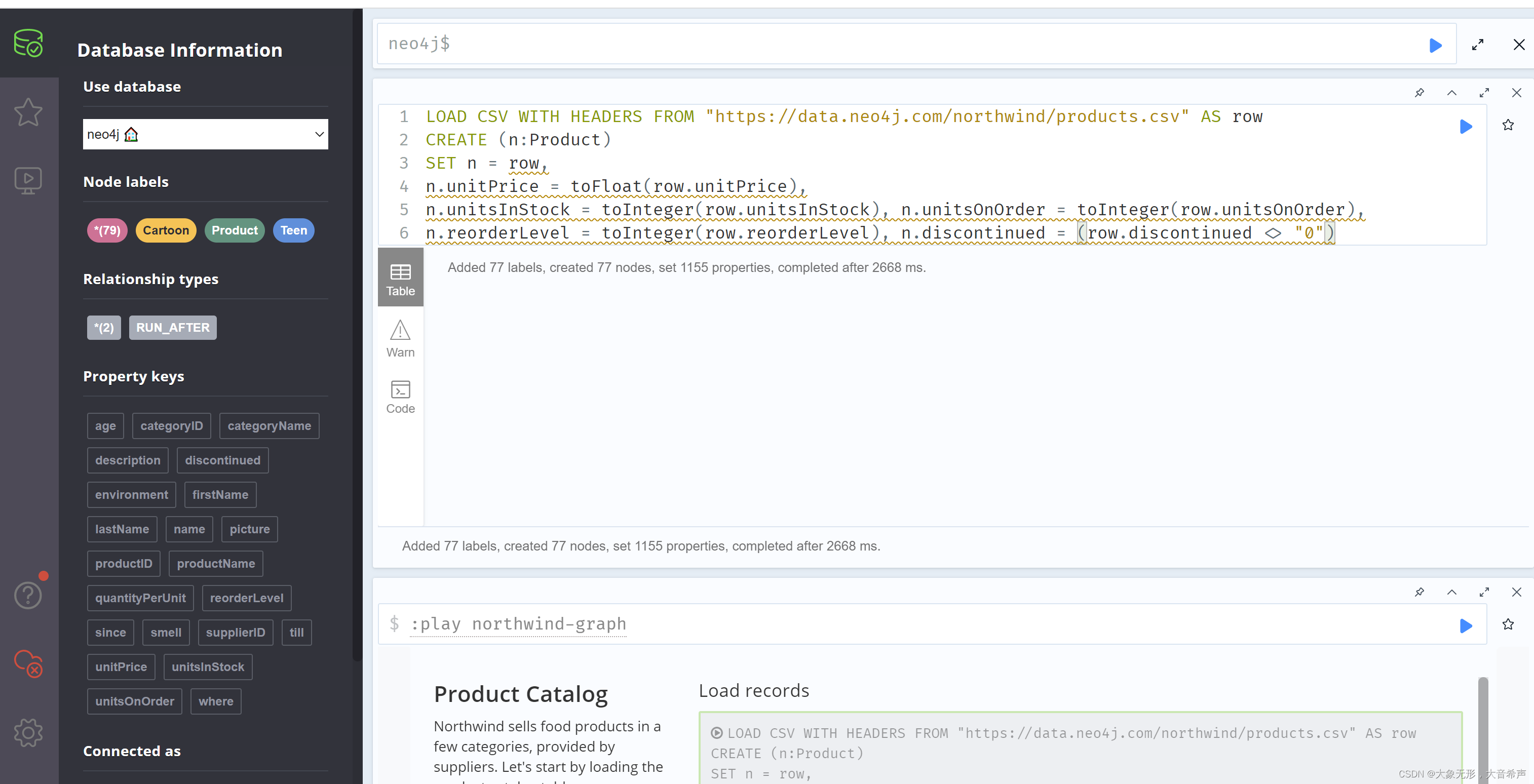

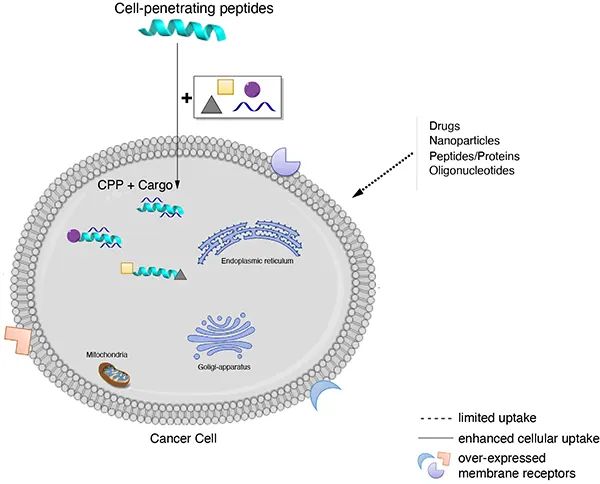

由于记忆元件是由触发器组成,而触发器只有两个状态:0和1,所以每条信号传输线只能传送一个触发器信息(0或1)。如果一条信号传输线既能与一个触发器接通,也可以与其断开而与另外一个触发器接通,则一条信息传输线就可以传输随意多个触发器的信息了。三态输出电路(或叫三态门)就是为了达到这个目的设计的。

三台输出电路可以由两个或非门和两个NMOS晶体管(T1,T2)及一个非门组成

三态(高阻态,或者叫浮 空态)

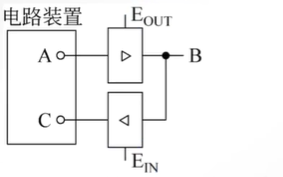

A输入端能不能输入到B,由E(Enable使能)决定。相当于是一把钥匙,看开没开门,没开就过不去

E为1(有效)上面是电源,假设A的输入为1。 标红的地方为mos,就为1,说明本条路是通的。B就是接的电源,输出就为1。如果A输入的为0,就是下面的路有效。自己试试就知道了。E为0 上下路都不通,那就是高阻态数据不能接收

双向的三态门在数据总线上常用了解即可