rk3568 Android11/12 适配 lvds 屏

LVDS(Low Voltage Differential Signal)即低电压差分信号。1994年由美国国家半导体(NS)公司为克服以TTL电平方式传输宽带高码率数据时功耗大、电磁干扰大等缺点而研制的一种数字视频信号传输方式。它是一种电平标准,广泛应用于液晶屏接口。

其中发送端是一个3.5mA的电流源,产生的3.5mA的电流通过差分线中的一路到接收端。由于接收端对于直流表现为高阻,电流通过接收端的100Ω的匹配电阻产生350mV的电压,同时电流经过差分线的另一路流回发送端。当发送端进行状态变化时,通过改变流经100Ω电阻的电流方向产生有效的’0’和’1’ 态。

它是电流驱动的,通过在接收端放置一个负载而得到电压,当电流正向流动,接收端输出为1,反之为0。

- LVDS是电流驱动模式 电压摆幅350mV,加载在100Ω电阻上;

- 传输速度快,推荐最大速率为655Mbps ,理论极限速率为1.923Gbps;

- LVDS不太适合较长距离的信号传送;

- LVDS接口只用于传输视频数据;

- LVDS接口主要将RGB TTL非平衡传输信号转换成LVDS平衡传输信号进行传输;

- LVDS不支持热插拔。

提示:rk3568 芯片设计只预留单lvds,双LVDS需要借助 mipi 或者HDMI 转换。

文章目录

- rk3568 Android11/12 适配 lvds 屏

- 圈重点 看想学

- 1. rk3568 适配 LVDS屏

- 2 LVDS 屏参调整

- Tips

- 总结

圈重点 看想学

a) rk3568 适配单LVDS屏

b) rk3568 调试过程异常情况

1. rk3568 适配 LVDS屏

- 核查原理图,适配LVDS硬件

确认屏端供电、复位、使能,只有VCC3V3_LCD。

- 确认 VCC3V3_LCD 控制信号 LVDS_ON 对应 GPIO3_D6。

- 确认背光,BL_EN 对应GPIO2_B1, PWM 信号使用 PWM4。

- 只因在图中多看一眼,发现不一样地方; PWM 和 BL_EN 均有反转三极管。

- 适配内核设备树

屏幕上电时许可在点亮屏幕慢慢调整,至于屏参则需要看屏幕规格书。

/ {

vcc3v3_lcd0_n: vcc3v3-lcd0-n {

gpio = <&gpio3 RK_PD6 GPIO_ACTIVE_LOW>;

};

backlight: backlight {

pwms = <&pwm4 0 25000 1>;

enable-gpios = <&gpio2 RK_PB1 GPIO_ACTIVE_LOW>;

};

panel {

compatible = "simple-panel";

backlight = <&backlight>;

power-supply = <&vcc3v3_lcd0_n>;

enable-delay-ms = <20>;

prepare-delay-ms = <20>;

unprepare-delay-ms = <20>;

disable-delay-ms = <20>;

bus-format = <MEDIA_BUS_FMT_RGB888_1X24>;

width-mm = <217>;

height-mm = <136>;

display-timings {

native-mode = <&timing0>;

timing0: timing0 {

clock-frequency = <68000000>;

hactive = <800>;

vactive = <1280>;

hback-porch = <32>;

hfront-porch = <16>;

vback-porch = <4>;

vfront-porch = <2>;

hsync-len = <16>;

vsync-len = <2>;

hsync-active = <0>;

vsync-active = <0>;

de-active = <0>;

pixelclk-active = <0>;

};

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dual-lvds-even-pixels;

panel_in_lvds: endpoint {

remote-endpoint = <&lvds_out_panel>;

};

};

};

};

};

&dsi0 {

status = "disabled";

};

&dsi0_in_vp0 {

status = "disabled";

};

&dsi0_in_vp1 {

status = "disabled";

};

&video_phy0 {

status = "okay";

};

&lvds {

status = "okay";

ports {

port@1 {

reg = <1>;

lvds_out_panel: endpoint {

remote-endpoint = <&panel_in_lvds>;

};

};

};

};

&lvds_in_vp1 {

status = "okay";

};

&lvds_in_vp2 {

status = "disabled";

};

&route_lvds {

status = "okay";

connect = <&vp1_out_lvds>;

};

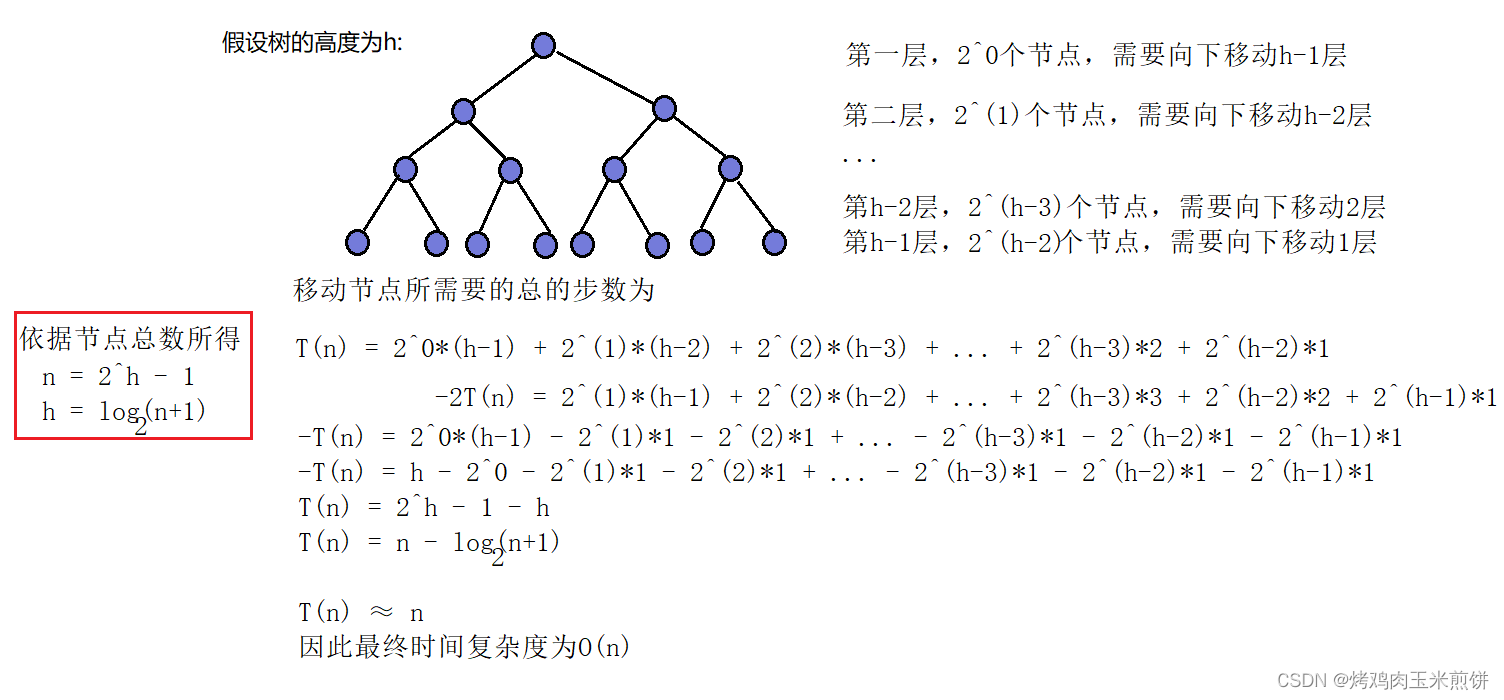

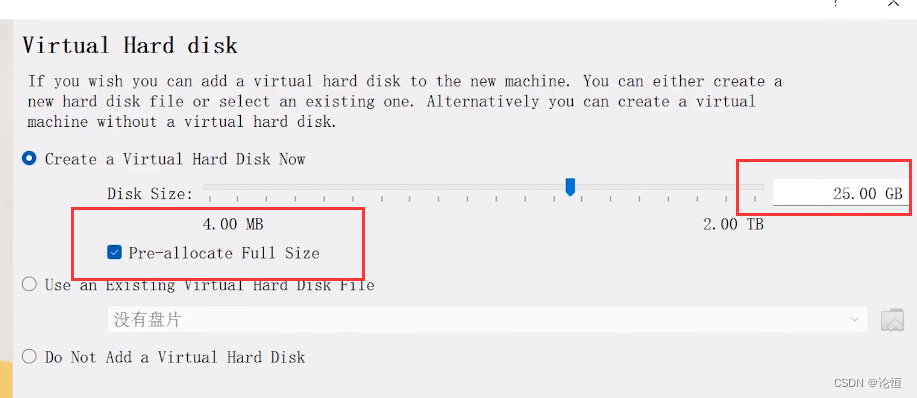

2 LVDS 屏参调整

timing0中参数解释如下:

水平分辨率:hactive 垂直分辨率:vactive

水平前尖:hfront-porch(HFP) 垂直前尖:vfront-porch (VFP)

水平后尖:hback-porch(HBP) 垂直后尖:vback-porch (VBP)

水平消隐信号:hsync - len(HS) 垂直消隐信号:vsync - len (VS)

– clock-frequency = HFP(Hactive + HS + HBP) x VFP(Vactive + VS + VBP) x fps(帧频率)

– lane-rate = clk (时钟频率) x RGB(3) x BIT(6或8) / lane_num

lane_num 表示差分时钟通道数,RGB与BIT值根据 dsi,format 具体情况而定。

– dsi,format 表示RGB三原色位深大小,可用参数如下:

MEDIA_BUS_FMT_RGB888_1X24 表示8bit色深

MEDIA_BUS_FMT_RGB666_1X18 表示6bit色深

上图是行同步信号:HS 为 864 = hsync+hbp+hactive+hfp = 16+32+800+16,在DE 为高电平时,HS 为低电平的时候就是有效的数据,即屏的水平像素为800。在HS 为高电平时,DE 是低电平,此时不显示数据,作用是消隐,即hsync。然后 32 个像素HBP 参数,就是等待屏真实数据信号前的无效信号数据长度,如果此时出现真实像素数据,很可能会丢数据和出现杂波。多余32 个像素看似多与时则防止这种情况;同理还有16 像素的HFP。

上图是行同步信号:HS 为 864 = hsync+hbp+hactive+hfp = 16+32+800+16,在DE 为高电平时,HS 为低电平的时候就是有效的数据,即屏的水平像素为800。在HS 为高电平时,DE 是低电平,此时不显示数据,作用是消隐,即hsync。然后 32 个像素HBP 参数,就是等待屏真实数据信号前的无效信号数据长度,如果此时出现真实像素数据,很可能会丢数据和出现杂波。多余32 个像素看似多与时则防止这种情况;同理还有16 像素的HFP。

上图是场同步信号,它与行同步信号相匹配,在DE 为高电平时里面会有1280 个行同步信号。按照当前屏幕 800x1280,看作每个数据包传输一个像素(pixel),800个水平方向像素传输完成需要一个行同步信号;水平行像素累积到1280则会需要产生一个场同步信号,确定这一帧图像传输完成。

上图是场同步信号,它与行同步信号相匹配,在DE 为高电平时里面会有1280 个行同步信号。按照当前屏幕 800x1280,看作每个数据包传输一个像素(pixel),800个水平方向像素传输完成需要一个行同步信号;水平行像素累积到1280则会需要产生一个场同步信号,确定这一帧图像传输完成。

人的视觉暂留效益,图像帧率达到30fps就会产生图像在一直运动的假象。

屏幕参数不对会出现闪屏和条纹。只需要对照规格书细微调整 前后肩,同步信号。

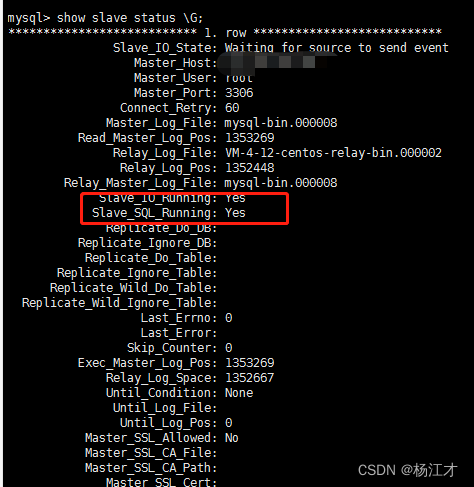

系统启动后可以查看屏参吗?查看VOP 属性确定相关数据。

# Android 查看 vop

cat /d/dri/0/summary

# linux 查看 vop

cat /sys/kernel/debug/dri/0/summary

Tips

- 开机过程屏幕无显示,休眠唤醒后显示正常

信号传输可排除,休眠唤醒时许也可排除;开机过程上电时许要核查 - 开机后一直黑屏,上电时许、信号均正常

可以去掉 logo 显示再次尝试,如果可正常看到 Android开机动画,很大概率时 VOP 不匹配。

&lvds_in_vp1 {

status = "okay";

};

&lvds_in_vp2 {

status = "disabled";

};

&route_lvds {

status = "okay";

connect = <&vp1_out_lvds>;

};

- 开机后黑屏,上电时许、信号异常

需要核查设备树,确保 dsi0关闭。

&video_phy0 {

status = "okay";

};

硬件须要确认各路供电是否正常。

- 开机后背光不亮,要仔细核查背光;本文中有反转三极管,需要翻转PWM极性,和使能信号有效电平

backlight: backlight {

pwms = <&pwm4 0 25000 1>;

enable-gpios = <&gpio2 RK_PB1 GPIO_ACTIVE_LOW>;

};

总结

活学活用,做个合格的搬运工。