写在前面:本章将理解编码器与解码器、多路复用器与多路分解器的概念,通过使用 Verilog 实现多样的解码器与多路分解器,通过 FPGA 并使用 Verilog 实现。

Ⅰ. 前置知识

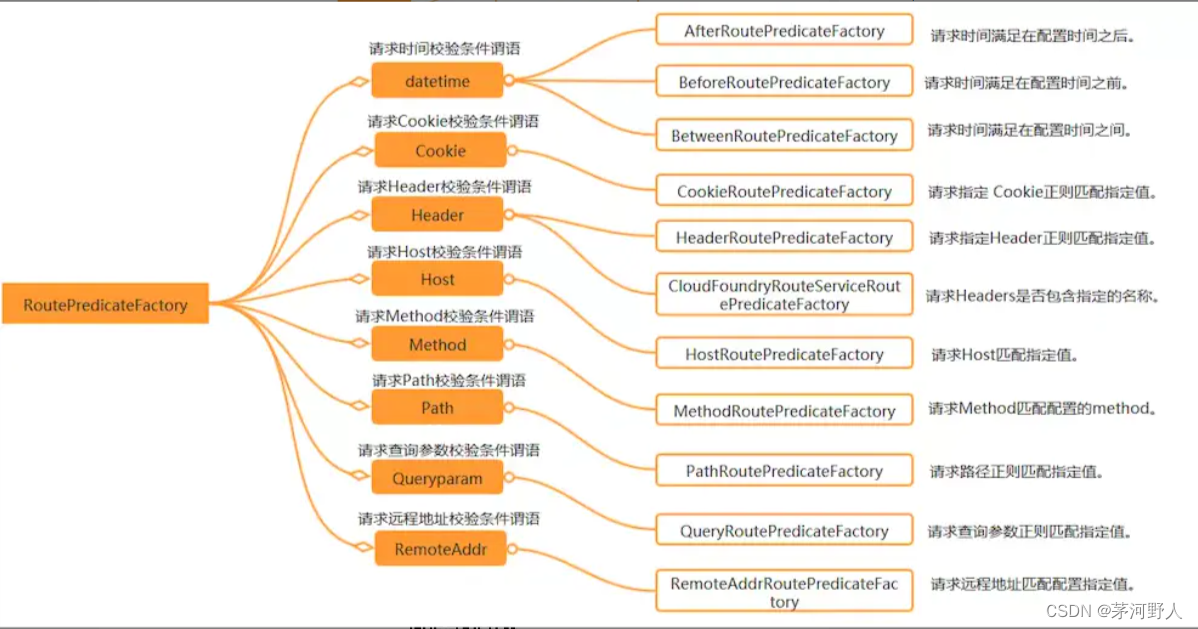

0x00 解码器与编码器(Decoder / Encoder)

解码器 (Decoder):执行转换和处理过程以将 Encoding 数据恢复到之前的电路。

编码器 (Encoder):将特定数据转换和处理为其他形式或格式的电路,以确保安全或缩小数据的大小。

编码器和解码器用于将任意两种符号体系相互转换。

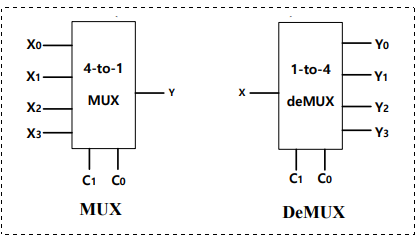

0x01 多路复用器 MUX 与 多路分解器 DeMUX

多路复用器 MUX (Multiplexer),能接收多个输入信号,按每个输入信号可恢复方式合成单个输出信号。复用器是一种综合系统,通常包含一定数目的数据输入,有一个单独的输出。

多路分解器 DeMUX (DeMultiplexer),是从一个输入接收资料,根据多条输出线中的输入,连接到预先选定的一条输出线的电路。

通常与带有 enable line 的解码器相同。

由于各自的功能特性,MUX 也被称为 Data Selctor(数据选择器),DeMUX 也被称为 Data Distributor(数据分配器)。

Ⅱ. 练习(Assignment)

0x00 2 to 4 Decoder

使用 AND 对电路进行 Verilog 编码,使用 NAND 结构对电路进行 Verilog 编码,通过 Verilog 的模拟结果完成真值表(2种),并比较两种形式的解码器。

💬 Design source:

`timescale 1ns / 1ps

module two_to_four_decoder(

input A, B,

output D1, D2, D3, D4

);

assign D1 = ~A&~B;

assign D2 = ~A&B;

assign D3 = A&~B;

assign D4 = A&B;

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module two_to_four_decode_tb;

reg AA, BB;

wire D1, D2, D3, D4;

two_to_four_decoder u_two_to_four_decoder(

.A(AA),

.B(BB),

.D1(D2),

.D2(D2),

.D3(D3),

.D4(D4)

);

initial AA = 1'b0;

initial BB = 1'b0;

always AA = #100 ~AA;

always BB = #200 ~BB;

initial begin

#1000

$finish;

end

endmodule

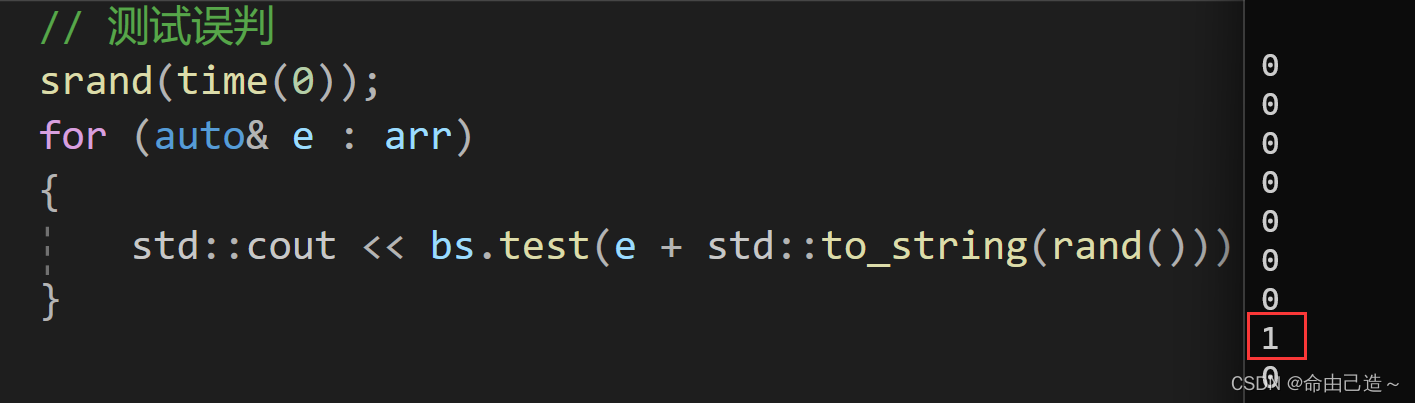

🚩 运行结果如下:

0x01 4 to 2 Encoder

使用 OR 对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表。

💬 Design source:

`timescale 1ns / 1ps

module four_to_two_encoder(

input a, b, c, d,

output e0, e1

);

assign e0 = a|b;

assign e1 = a|c;

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module four_to_two_encoder_tb;

reg aa, bb, cc, dd;

wire e0, e1;

four_to_two_encoder u_four_to_two_encoder(

.a(aa),

.b(bb),

.c(cc),

.d(dd),

.e0(e0),

.e1(e1)

);

initial aa = 1'b0;

initial bb = 1'b0;

initial cc = 1'b0;

initial dd = 1'b0;

always aa = #100 ~aa;

always bb = #200 ~bb;

always cc = #400 ~cc;

always dd = #800 ~dd;

initial begin

#1000

$finish;

end

endmodule

🚩 运行结果如下:

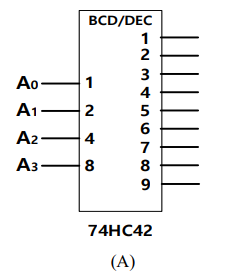

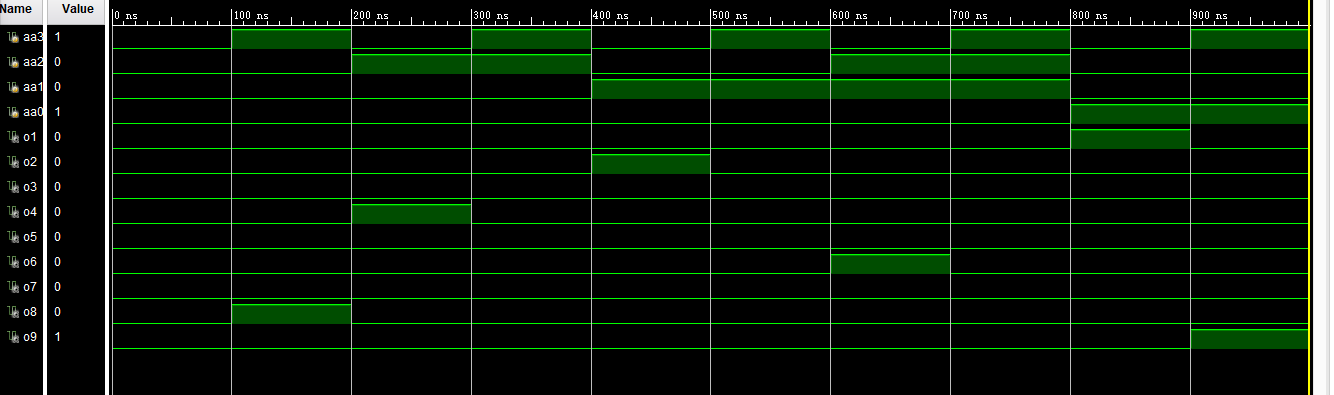

0x02 BCD to Decimal Decoder

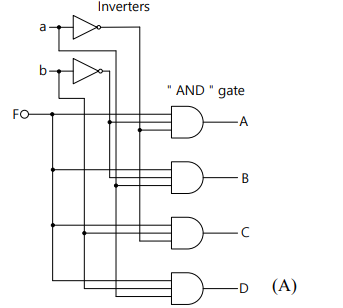

通过 Verilog 编码实现(A)的结构,通过 Verilog 的仿真结果完成真值表,并确认是否与理论中的Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1ps

module bcd_decoder(

input a3, a2, a1, a0,

output o1, o2, o3, o4, o5, o6, o7, o8, o9

);

assign o1 = ~a3&~a2&~a1&a0;

assign o2 = ~a3&~a2&a1&~a0;

assign o3 = ~a3&~a2&a1&a0;

assign o4 = ~a3&a2&~a1&~a0;

assign o5 = ~a3&a2&~a1&a0;

assign o6 = ~a3&a2&a1&~a0;

assign o7 = ~a3&a2&a1&a0;

assign o8 = a3&~a2&~a1&~a0;

assign o9 = a3&~a2&~a1&a0;

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module bcd_decoder_tb;

reg aa3, aa2, aa1, aa0;

wire o1, o2, o3, o4, o5, o6, o7, o8, o9;

bcd_decoder u_bcd_decoder(

.a3(aa3),

.a2(aa2),

.a1(aa1),

.a0(aa0),

.o1(o1),

.o2(o2),

.o3(o3),

.o4(o4),

.o5(o5),

.o6(o6),

.o7(o7),

.o8(o8),

.o9(o9)

);

initial aa3 = 1'b0;

initial aa2 = 1'b0;

initial aa1 = 1'b0;

initial aa0 = 1'b0;

always aa3 = #100 ~aa3;

always aa2 = #200 ~aa2;

always aa1 = #400 ~aa1;

always aa0 = #800 ~aa0;

initial begin

#1000

$finish;

end

endmodule

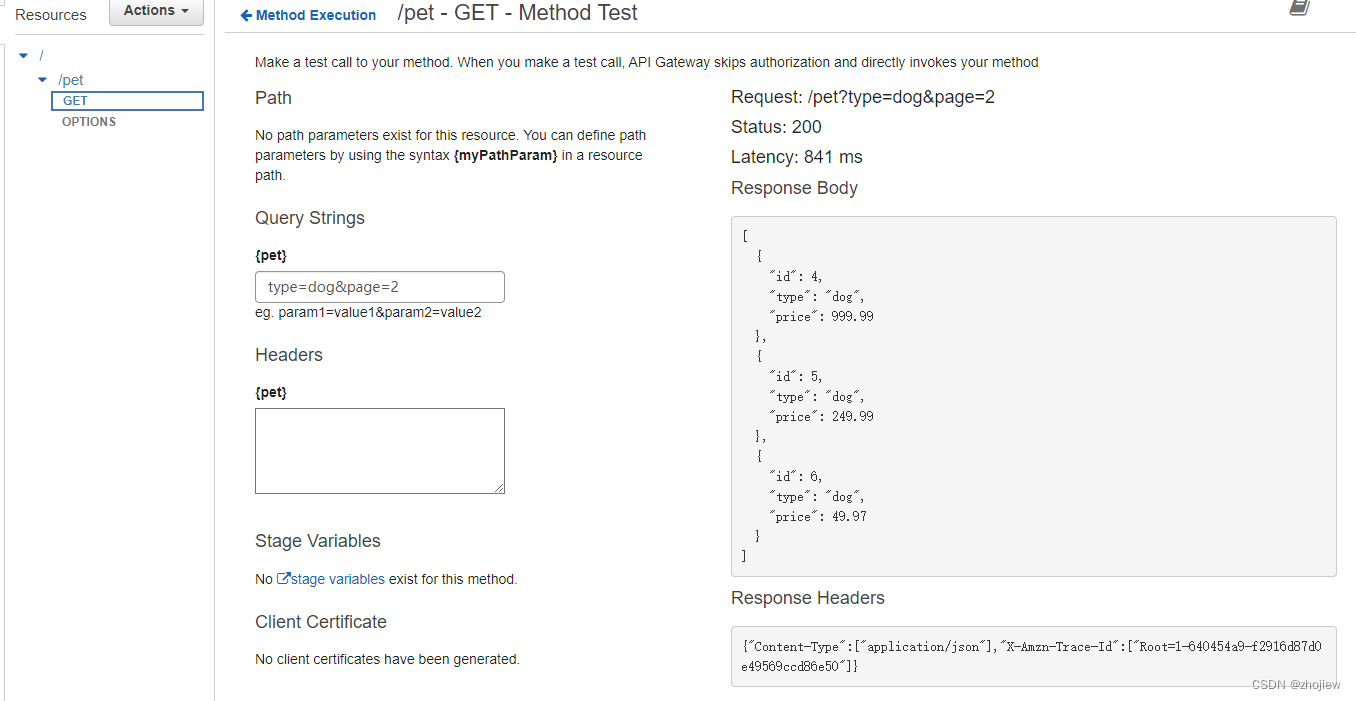

🚩 运行结果如下:

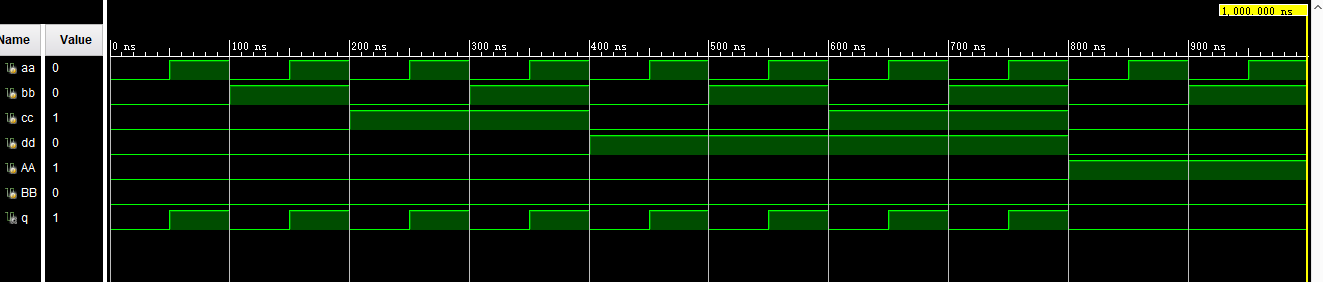

0x03 4 to 1 line MUX

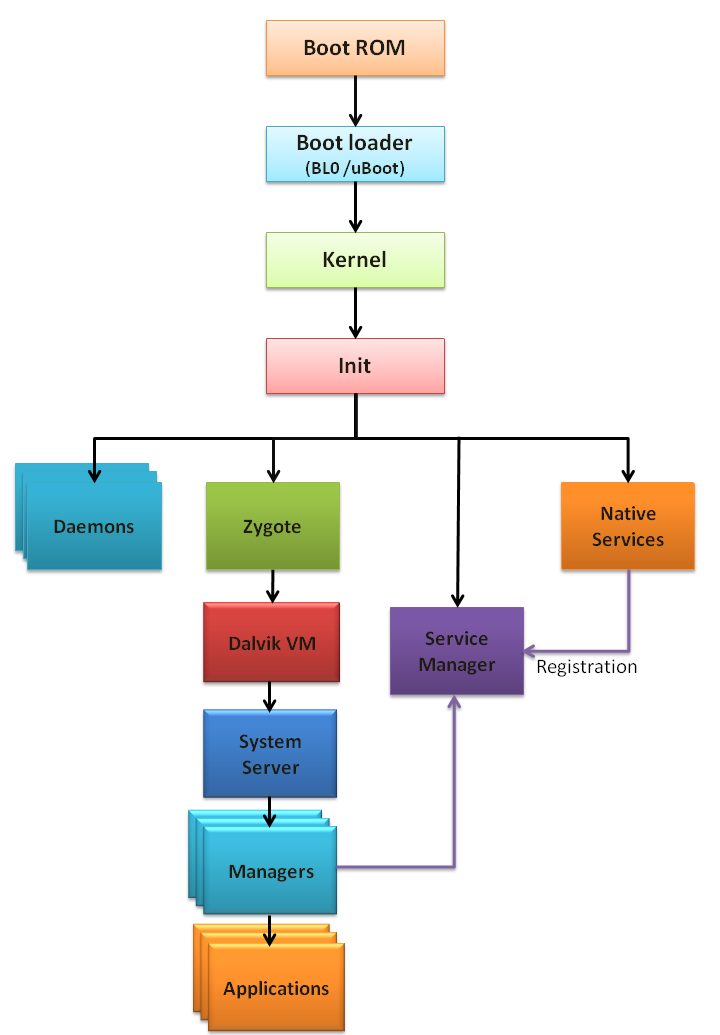

以(A)的结构对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表。并确认是否与理论中的 Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1ps

module four_to_one_mux(

input a, b, c, d, A, B,

output q

);

assign q = (a&~B&~A)|(b&B&~A)|(c&~B&A)|(d&B&A);

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module four_to_one_mux_tb;

reg aa, bb, cc, dd, AA, BB;

wire q;

four_to_one_mux u_four_to_one_mux(

.a(aa),

.b(bb),

.c(cc),

.d(dd),

.A(AA),

.B(BB),

.q(q)

);

initial aa = 1'b0;

initial bb = 1'b0;

initial cc = 1'b0;

initial dd = 1'b0;

initial AA = 1'b0;

initial BB = 1'b0;

always aa = #50 ~aa;

always bb = #100 ~bb;

always cc = #200 ~cc;

always dd = #400 ~dd;

always AA = #800 ~AA;

always BB = #1600 ~BB;

initial begin

#2000

$finish;

end

endmodule

🚩 运行结果如下:

0x04 1 to 4 line deMUX

以(A)的结构对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表,确认是否与理论中的 Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1ps

module one_to_four_mux(

input A, B, f,

output a, b, c, d

);

assign a = f&(~A&~B);

assign b = f&(~A&B);

assign c = f&(A&~B);

assign d = f&(A&B);

endmodule

💬 Testbench:

`timescale 1ns / 1ps

module one_to_four_mux_tb;

reg AA, BB, ff;

wire a, b, c, d;

one_to_four_mux u_one_to_four_mux(

.A(AA),

.B(BB),

.f(ff),

.a(a),

.b(b),

.c(c),

.d(d)

);

initial AA = 1'b0;

initial BB = 1'b0;

initial ff = 1'b0;

always AA = #100 ~AA;

always BB = #200 ~BB;

always ff = #400 ~ff;

initial begin

#1000

$finish;

end

endmodule

🚩 运行结果如下:

📌 [ 笔者 ] Foxny,Akam

📃 [ 更新 ] 2023.3.5

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,

本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |

![[Latex]参考文献的格式:数字,作者+年份](https://img-blog.csdnimg.cn/5634e9a8127b4d66925c131c5a419ebf.png)