“棱镜门”的曝光,暴露出我国的信息安全存在极大的安全隐患,作为信息传输

载体的网络设备,其国产化需求迫切,国产处理器、国产可编程逻辑器件、以太网交

换芯片等具有良好的应用前景,另一方面,宽带数据业务、多媒体业务的需求对网络

设备的性能提出了更高的要求。基于高速串行总线技术的

VPX

标准以高性能、高可

靠性、扩展性以及优良的架构,在现代通信中得到了广泛的应用。本文对国产芯片及

VPX

标准进行了系统的研究,以某信息处理设备为背景平台,设计了基于

VPX

的以

太网交换板,其核心处理器、可编程逻辑器件、交换芯片均采用了国产芯片。

2.1

VPX

总线概述

2.1.1

VPX

总线发展

VPX

总线是美国国防部授权由

28

家国际知名嵌入式科研生产厂家为核心成员的

VITA

组织联合讨论并制定的新一代高速串行总线。

VPX

总线来源于

VME

总线,随

着业界对总线技术传输带宽要求不断提高,采用并行方式的

VME

总线逐渐显露其弊

端,一方面并行传输方式是依赖于同一时钟来传输和接收信号,总线带宽依赖于时钟

频率,过分提高时钟频率会引起信号完整性的问题,布线长度稍有差异,会造成数据

的时序紊乱。另一方面,并行总线位宽的增加会导致引脚数增加,封装尺寸增加,布

线数目随之增加,系统成本随之攀升。针对并行总线的缺点,高速串行总线采用时钟

打包和时钟恢复技术以及信号的预加重和均衡处理技术,成功解决了时钟和数据之间

的偏移和抖动问题;采用低压差分电平的传输协议,大大减少了总线位宽,降低了系

统成本。基于高速串行总线的优势,

VITA

组织将高速串行互连技术引入到

VME

总

线中,即诞生了新的

VPX

总线,并制定了

VITA46

标准。

VITA46

是

VPX

的基础标

准,也是一个单板模块规范的协议族,包括若干个子规范,主要定义了连接器、

VME

总线与

VPX

总线管脚映射关系、对

PCI Express

、

Serial Rapid IO

、

1/10Gbit Ethernet

等高速串行协议的支持以及系统管理等。在

VITA46

的基础上,

VITA

组织又根据市

场使用反馈及功能需求情况对

VPX

标准进行了更新和升级,比较重要的有两个:一

个是

VITA48

,其全称为“增强加固设计的机械规范”,

VITA 48

标准在模块结构等方

面对

VITA46

标准进行了补充,对散热和结构加固等方面做了新的定义,以满足军事

和航空航天领域严酷的应用环境,也是第一个可用于军用平台的商用现货模块;二是

VITA65

,又称

Open VPX

,是一个基于

VPX

模块的开放式系统架构,它在

VITA46

规范基础上重新定义系统兼容框架,定义了模块结构、连接器、散热、通信协议、电

源定义,并且描述了槽位定义、背板、模块及未定义与应用见的特性,解决了不同厂

家的

VPX

产品兼容问题。目前

VPX

总线仍在不断地更新升级,成为最具潜力的总线

技术。

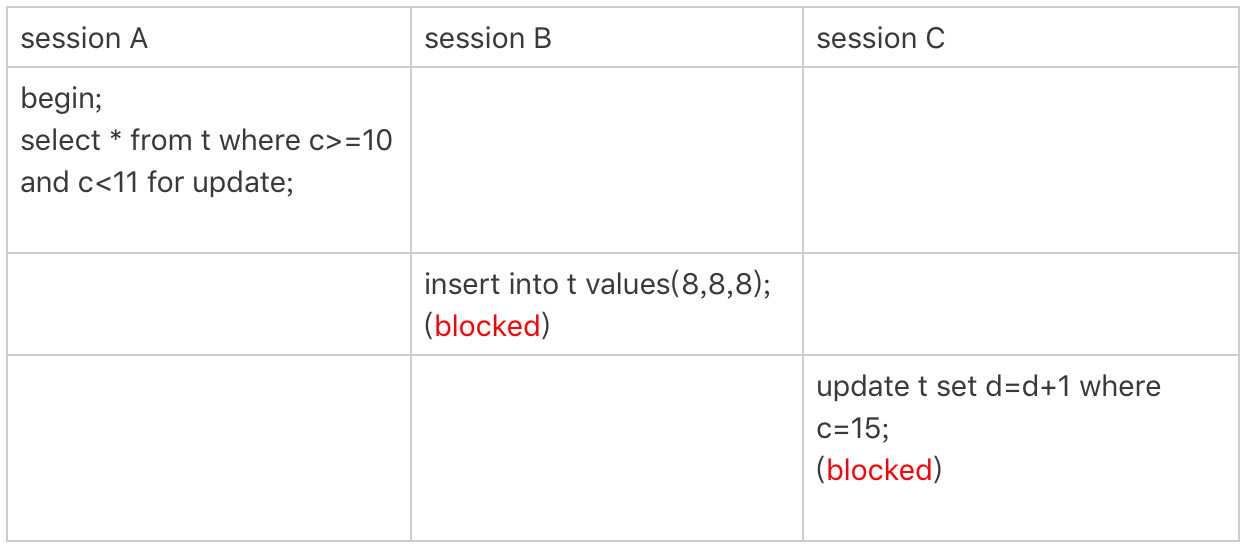

2.2

信息处理平台总体方案设计

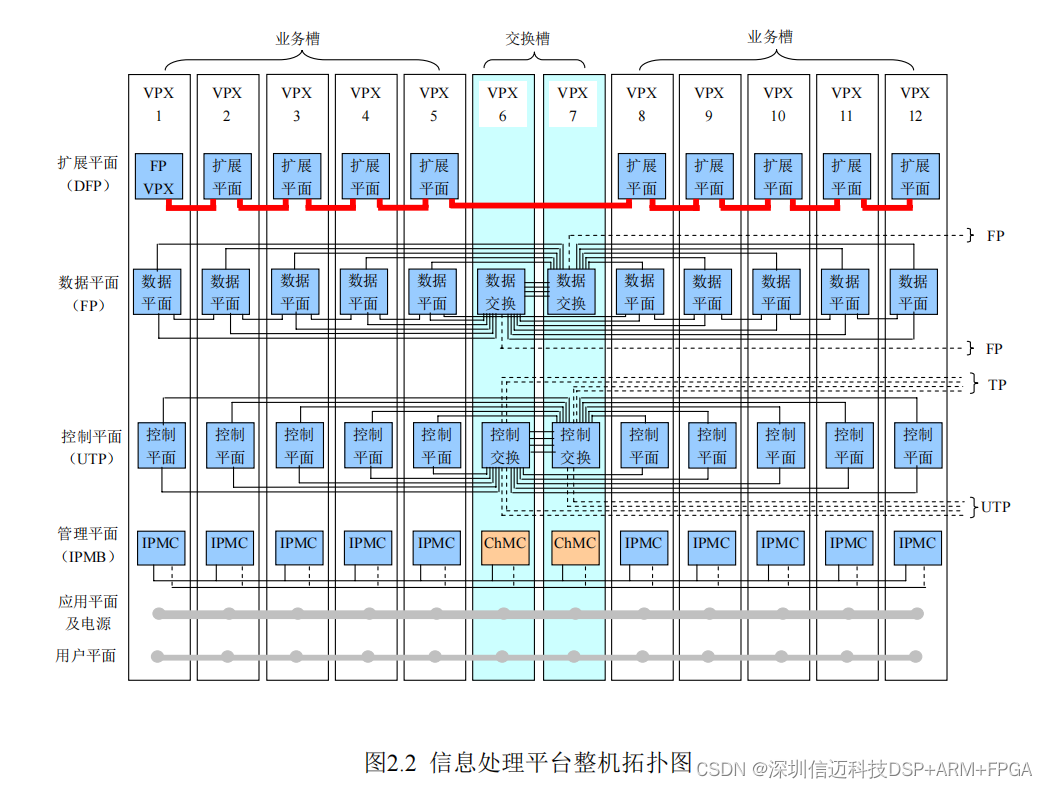

根据之前的描述,本设计的信息处理平台基于以太网交换,所以采用千兆以太网

串行协议作为平台系统内部总线,实现交换板和业务板的互联是比较合适的。对于拓

扑结构,

VPX

标准支持网络型、单星型、双星型等多种结构。网络型结构中每个节

点与其他节点都有互连通路,其中任意节点失效时,未失效节点仍能相互通信,因此

该结构具有较强的冗余度,但这种结构中背板的走线数量、接口管脚数量是随着节点

数量呈几何倍数增长,软硬件设计复杂度成倍增加,如果系统中需要互连的设备较多

(如超过

5

个),会对系统的可靠性造成较大影响。单星型结构中每个业务节点通过

交换节点实现互连互通,这种结构较为简单,某个业务节点失效时其他节点还可以通

过交换节点正常通信,但当交换节点出现故障时,整个系统将会瘫痪,因此可靠性相

对低。双星形结构相对于星型结构增加了一个交换节点作为备份,同时业务节点与备

份交换节点有互连通路,当其主交换节点出现故障时,备份交换节点接替主交换节点,

实现业务的无缝切换,因此这种结构综合了网络型结构和单星形结构的优点,既控制

了软硬件设计的复杂度,又起到冗余和备份的作用。综合比较

3

种结构的优缺点,本

平台选用双星型结构作为背板的互连结构,整机拓扑如图

2.2

所示。

本课题的信息处理平台设计

12

个槽位,槽位

1-5

及

8-12

为业务板卡插槽,

6-7

为以太网交换板插槽(

6

主

7

备),拓扑框架中包含数据平面、控制平面、管理平面、

扩展平面、应用平面及电源和用户平面。其中数据平面实现交换插卡与各业务插卡间

数据业务传送。控制平面实现交换插卡与各业务插卡间控制信息传送。管理平面用于

机箱管理。用户平面及电源位于

P0/J0

和部分

P1/J1

的单端信号,主要为各插卡提供

电源、时钟、复位等相关信号。数据平面、控制平面、扩展平面位于

P2/J2~P6/J6

和

P1/J1

的差分信号,均通过

serdes

串行总线实现互联。

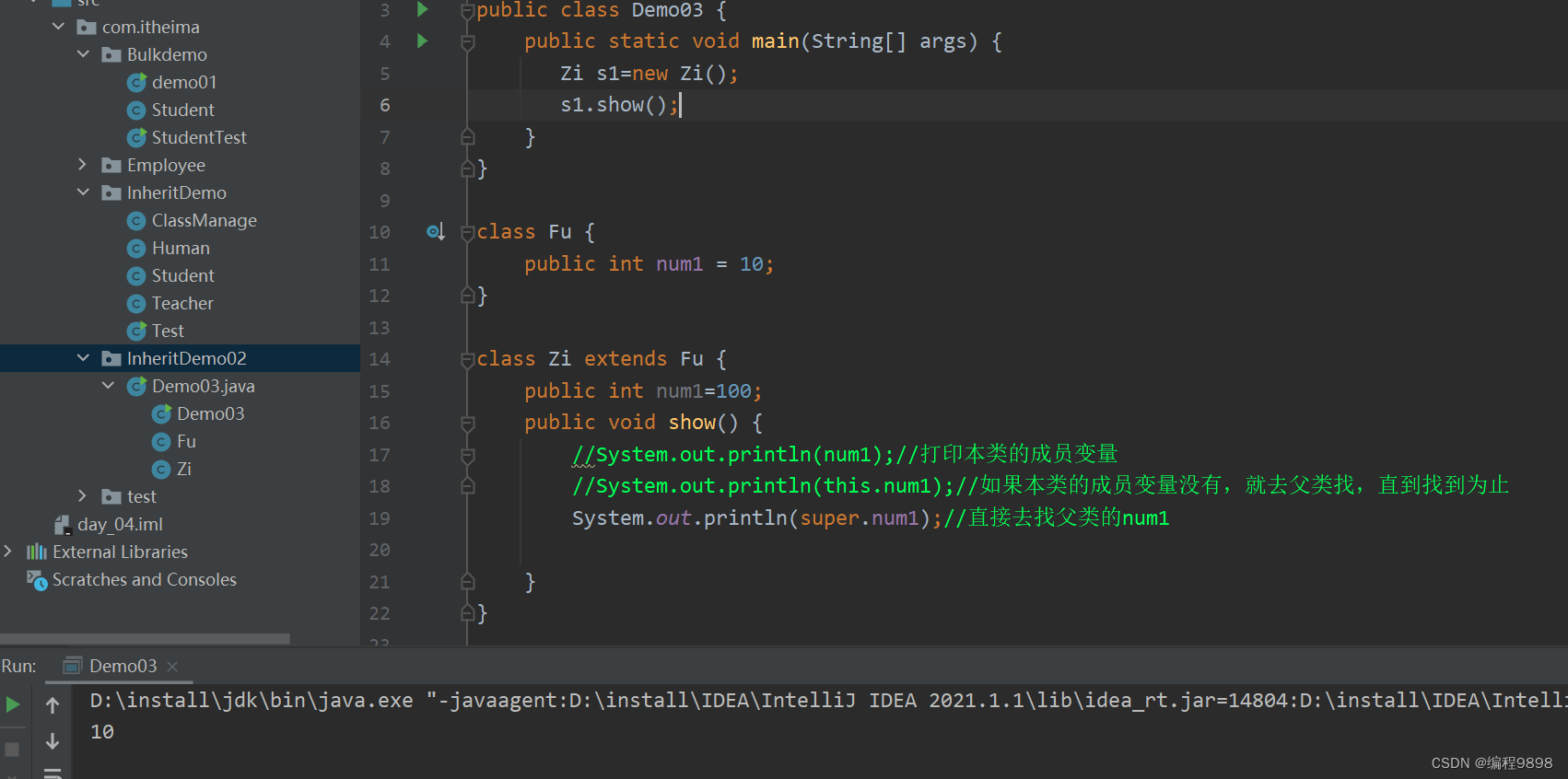

2.3

核心交换芯片选型

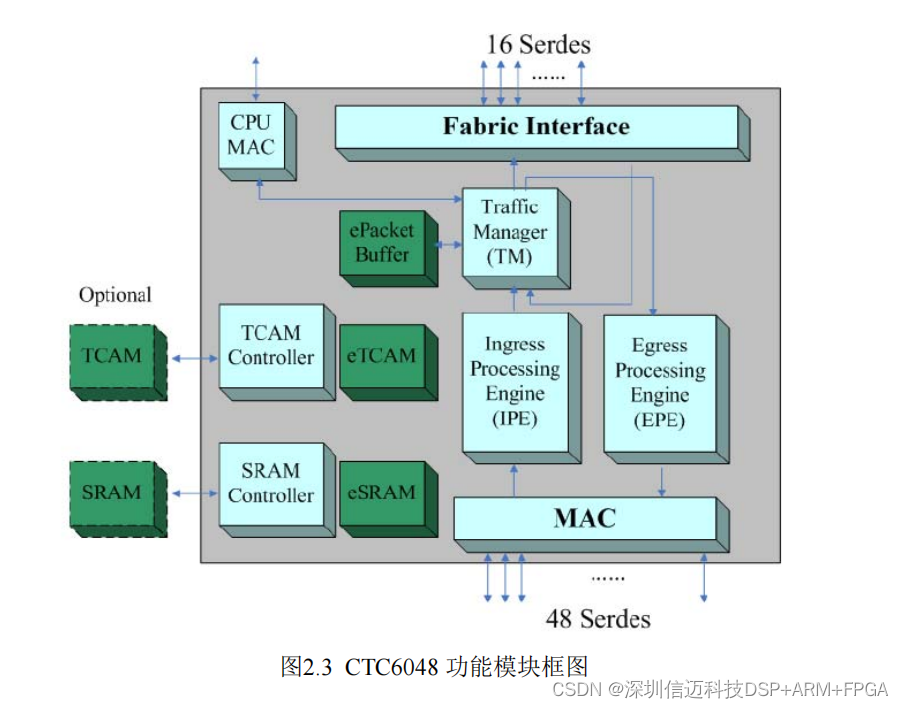

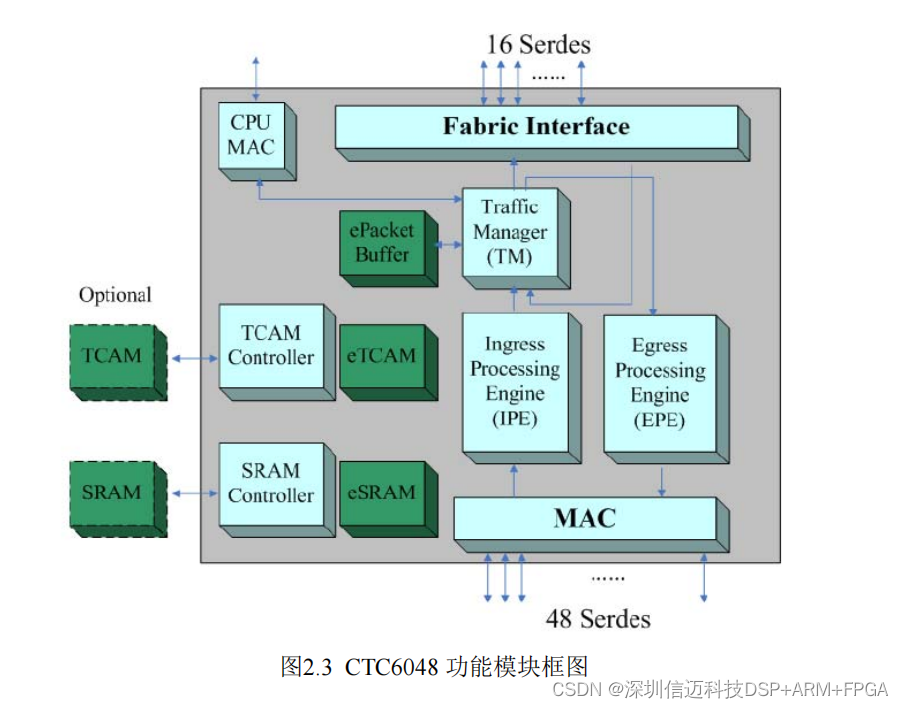

前一章节已经说明,国内提供自主以太网交换芯片的厂家只有苏州盛科,因此对

以太网交换芯片的选型主要考虑盛科公司的相关产品。根据课题对下一代信息处理平

台的性能要求及厂家建议,最终选用苏州盛科的

CTC6048

作为以太网交换板的核心

以太网交换芯片。

CTC6048

是盛科公司自主研发的第二代以太网网络交换核心芯片,

它集数据包处理、流量管控功能与一身,并集成了上联

Fabric

,具备完整的

L2/L3/MPLS/Metro

特性。

CTC6048

支持基于硬件的

IPV4/IPV6

双栈路由、

MPLS

交

换、

IP/MPLS

隧道、

L2/L3 VPN

以及组播等,在保证

QOS

的情况下提供

150Mpps

的

包处理能力。芯片采用业界先进的

65nm

高速

CMOS

工艺,芯片内部包括多个

Mac

接口,数据入口处理引擎(

IPE

)、数据出口处理引擎(

EPE

),流量管控模块、内部

TCAM

及

TCAM

控制器、内部

SDRAM

及

SDRAM

控制器、交换网络接口,网络侧

提供

48

对高速

Serdes

,可根据应用环境配置为

48

个

10/100/1000M

以太网接口或

8

个万兆以太网接口,上联口提供

16

对高速

Serdes

,可以连接盛科交换芯片或交换矩

阵以实现接口扩展,也可以配置为

4

个万兆以太网接口。

CTC6048

的功能模块框图

如图

2.3

所示。

2.4

核心处理器芯片选型

以太网交换板的处理器的主要功能是基于某种操作系统来运行网络协议软件、系

统维护等,需要考虑与交换芯片的互连及支持的操作系统、开发环境等。根据之前的

介绍,龙芯

1

系列主要面向低端嵌入式领域,龙芯

2

系列面向高端嵌入式领域,龙芯

3

系类主要面向服务器市场,所以本课题选用龙芯

2F

作为以太网交换板的核心处理

器。龙芯

2F

是一款集成龙芯

64

位

CPU

核,兼容

MIPS64

的高性能低功耗处理器芯

片

,

支持

1G

主频,具有高

I/O

接口带宽和访存带宽。龙芯

2F

还集成了

64

位

DDR2

内

存控制器,

PCI/PCI-X

控制器、

Local-Bus

总线接口、中断控制器和视频加速单元片

,

支持

1G

主频,具有高

I/O

接口带宽和访存带宽。龙芯

2F

还集成了

64

位

DDR2 内存

控制器,

PCI/PCI-X

控制器、

Local-Bus

总线接口、中断控制器和视频加速单元,系统

通过扩展标准的

PCI/PCI-X

总线进行,既作为

PCI/PCI-X

总线的主控制器,也能作为

PCI/PCI-X

总线的设备。龙芯

2F

还实现了软件动态调节处理器工作频率的特性,操

作系统使用这个特性可根据负载情况改变处理器工作频率已达到降低功耗的目的。龙

芯

2F

在典型工作频率

800MHz

下的实测功耗仅为

3W

。综上所述,龙芯

2F

能满足本

课题低功耗高性能的应用需求。

2.5

核心

FPGA

芯片选型

针对

FPGA

的选型,需综合功能、性能、技术支持、开发环境考虑多方面的因素,

以降低设计风险。通过与深圳国微、成都华微、京微雅格三个厂家技术交流发现,从

逻辑资源、性能等方面出发,三个公司均有对应的产品能满足本课题以太网交换板的

需求,但从器件应用情况、开发环境等方面来看,京微雅格的产品主要应用在民用领

域,另一方面其

FPGA

器件结构、开发环境与目前我们所熟悉的

Altera

、

Xilinx

均不

同,尤其是需要重新熟悉开发环境,开发难度较大。深圳国微、成都华微均具备“二

级保密资质”,“军用元器件承研、承制资质”,产品大量应用于航空、航天领域,且

开发环境与

Xilinx

开发环境相同,便于设计人员快速进入角色。但成都华微的

FPGA

目前不支持

FPGA

硬核

MicroBlase

,针对某些领域其适用范围有限,综合考虑上述因

素,本课题核心

FPGA

的选型针对深圳国微的产品展开。根据本课题

FPGA 的功能

及其需要的逻辑资源,并综合考虑器件封装大小等因素,最终选用深圳国微的

SMQ2V1000FG256

作为本课题的核心

FPGA

芯片。

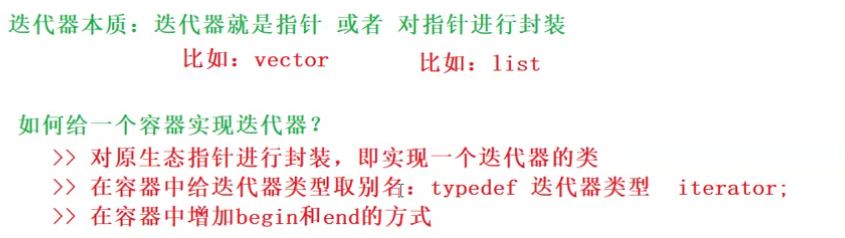

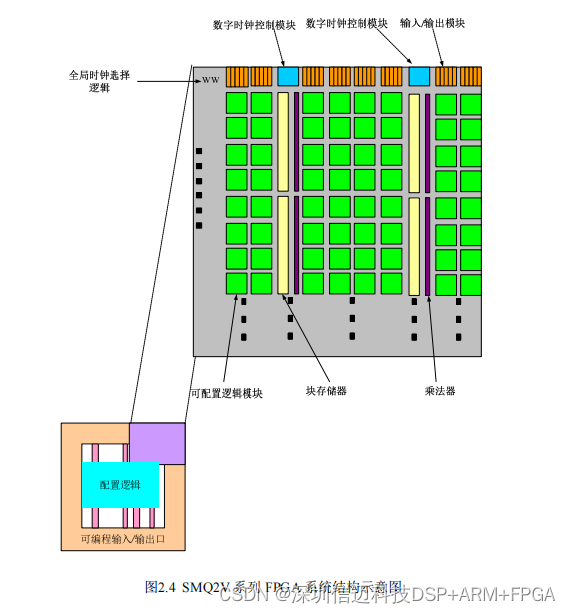

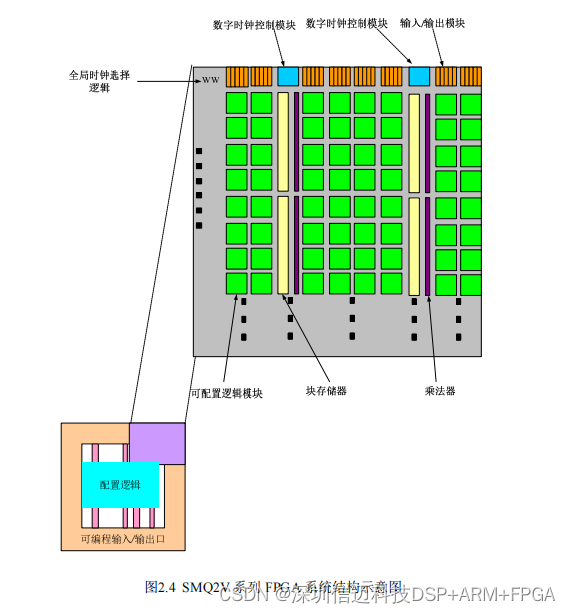

SMQ2V1000FG256

主要由可配置逻辑模块(

CLB

)、可配置输入输出模块(

IOB

)、

可配置

SRAM

型存储模块(

BRAM

)、可配置内嵌乘法器(

MUL

)、可配置数字时钟

管理器(

DCM

)以及资源丰富的层次式可编程互连线等单元所构成,如图

2.4

所示。

信迈提供龙芯+国产FPGA方案及定制。