鉴频鉴相器设计(Phase Frequency Detector,PFD)

- 前言

- 一、 PFD的工作原理

- 二、 PFD电路设计

- (1)PFD电路图

- (2)D触发器电路图

- (3)与非门(NAND)电路图

- (4)或非门(NOR)电路图

- (5)反相器(INV)电路

- 三、PFD仿真测试

- PFD测试电路图

- (1)A超前B

- (2)B超前A

- 参考文献:

- 各部分链接链接:

前言

本文主要内容是对鉴频鉴相器(Phase Frequency Detector,PFD) 模块设计设计进行阐述,包括工作原理、电路结构、仿真结果各部分内容。

一、 PFD的工作原理

PFD 作为 PLL 中的关键模块,完成比较输入参考频率

f

r

e

f

f_{ref}

fref与反馈频率

f

d

i

v

f_{div}

fdiv的频率与相位的工作,将相位差以电压通断的形式传输到 CP 中,进而对环路滤波器充电和放电。常见的三态鉴频鉴相器的输入输出端口定义如图4-2-1所示。

其状态转换图可以用图4-2-2表示,对于理想的三态鉴频鉴相器而言, UP 和 DN 信号不会同时为高电平。它具有三种工作状态:

状态1:当

f

r

e

f

f_{ref}

fref信号的相位超前

f

d

i

v

f_{div}

fdiv信号时,PDF的输出 UP 为高电平矩形脉冲,且脉冲宽度与两输入信号的相位差相对应,在f_ref信号上升沿到来时矩形脉冲开始,在

f

d

i

v

f_{div}

fdiv信号上升沿到来时矩形脉冲结束,此时 DN 一直为低电平;

状态2:当

f

d

i

v

f_{div}

fdiv的相位超前

f

r

e

f

f_{ref}

fref时,PFD的输出DN为高电平矩形脉冲,且脉冲宽度与两输入信号间的相位差相对应,f_div信号上升沿到来时矩形脉冲开始,

f

r

e

f

f_{ref}

fref信号上升沿到来时矩形脉冲结束,而输出 UP 一直为低电平;

状态3:当信号

f

r

e

f

f_{ref}

fref和

f

d

i

v

f_{div}

fdiv完全相位相同时,UP 和 DN 信号一直都是低电平。

状态3:当信号

f

r

e

f

f_{ref}

fref和

f

d

i

v

f_{div}

fdiv完全相位相同时,UP 和 DN 信号一直都是低电平。

根据上述的状态转换原理,PFD的输出脉冲的宽度就可以用来量化两输入信号

f

r

e

f

f_{ref}

fref和

f

d

i

v

f_{div}

fdiv之间的相位差。图4-2-3给出了上述的工作波形图。

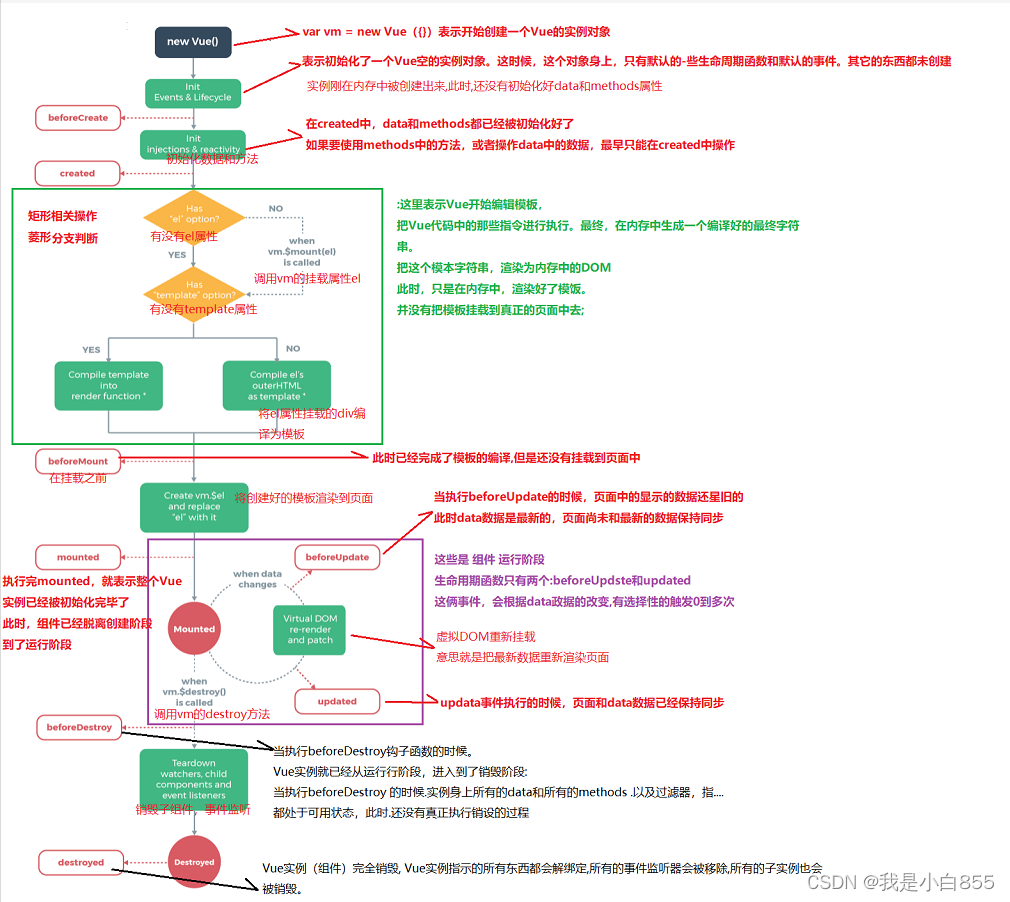

典型的三态 PFD 的结构如图4-2-4所示。它由两个带有复位端的上升沿触发的D触发器和一个逻辑与门组成,D 触发器的数据端 D 总是接高电平。该鉴频鉴相器通过

f

r

e

f

f_{ref}

fref和

f

d

i

v

f_{div}

fdiv的时钟上升边沿触发,产生高电平的 UP 和 DN 矩形脉冲信号。UP 和 DN 通过与门提供给D触发器的复位信号 Reset,当 UP 和 DN 均为高电平时复位信号使之恢复为电平。

但在实际的电路中往往会有第四态的出现,以

f

r

e

f

f_{ref}

fref超前于

f

d

i

v

f_{div}

fdiv的状态为例:在

f

d

i

v

f_{div}

fdiv到来将 UP 信号复位的时刻,DN信号出现了很短暂的脉冲。在当信号

f

r

e

f

f_{ref}

fref和

f

d

i

v

f_{div}

fdiv完全相位相同时,UP和DN信号也都会出现这样很短暂的脉冲。出现的原因是,在实际电路中由于存在器件的开关延时,造成了 PFD 的 UP 和 DN 信号通过逻辑与门产生 Reset 信号有一定时间的滞后,并且Reset 信号对 D 触发器的复位同样有一定时间的滞后。和理想状态的区别是由于实际电路中器件的延时造成的。因此,从UP和DN信号被Reset信号通过 D 触发器复位为低电平的过程中产生了 UP 和 DN 信号都为高电平的第四种状态。那么,此时 PFD的工作状态为:

状态1:UP=0,DN=0

状态2:UP=1,DN=0

状态3:UP=0,DN=1

状态4:UP=1,DN=1

考虑到信号复位存在一定的响应时间,所以经过δt时间后,输出的UP和DN才会变成0,其状态转换图如图4-2-5所示:

这种PFD的输出 UP 和 DN 在一段时间内同时处于逻辑高电平时的第四态会使电荷泵的充放电开关同时打开,因而不仅会增加锁相环的功耗,同时会加剧电荷泵的电源噪声,器件热噪声等对 PLL 的相位噪声的恶化。此外还会加剧电荷泵充放电电流失配这一非理想因素给锁相环带来的相位杂散等负面影响。

评价PFD好坏的主要有如下特征:克服死区、高速、低功耗、低噪声和宽线性范围。在实际设计中要折中速度和死区两方面因素来考虑。为了提高PFD电路的速度,减小复位脉冲的脉宽是关键,但对于后接电荷泵的锁相环会导致死区,在实际设计时既需要复位脉冲来克服死区,为了提高速度又尽量减小复位脉冲的宽度。

二、 PFD电路设计

图4-2-6是本次设计的 PFD 实现电路,它由两个边沿触发、带复位功能的 D 触发器、一个与非门和一个反相器组成。针对 PFD 电路中存在的死区效应,我们对传统的 PFD 电路结构进行了优化设计,在复位电路的输入端加上了一个延时单元。该延时单元的作用是,当PFD的两输入信号同频同相时,输出的脉冲有足够的宽度(延迟时间)使电荷泵的充放电开关打开(关断),从而避免死区效应的发生。在加入了该延时电路后,PFD 的输出信号上会出现微小的窄脉冲延时信号,即使在锁定状态下,该脉冲信号依然会存在。如果该脉冲信号过小,将会造成电荷泵输出端电压出现毛刺。因而这个延迟时间必须考虑电荷泵开关的打开与关断时间。同时,在设计尺寸时,采用小尺寸的 MOS 管作为开关管,目的是尽可能减小开关管的寄生电容,减少 MOS 器件的开关时间,从而改善死区。D 触发器实现 PFD 电路的原理图如图4-2-7所示,其中的两个 RS 锁存器交叉耦合。图4-2-8、4-2-9、4-2-10分别给出了 PFD 所用到的模块的具体实现电路。

(1)PFD电路图

(2)D触发器电路图

(3)与非门(NAND)电路图

(4)或非门(NOR)电路图

(5)反相器(INV)电路

三、PFD仿真测试

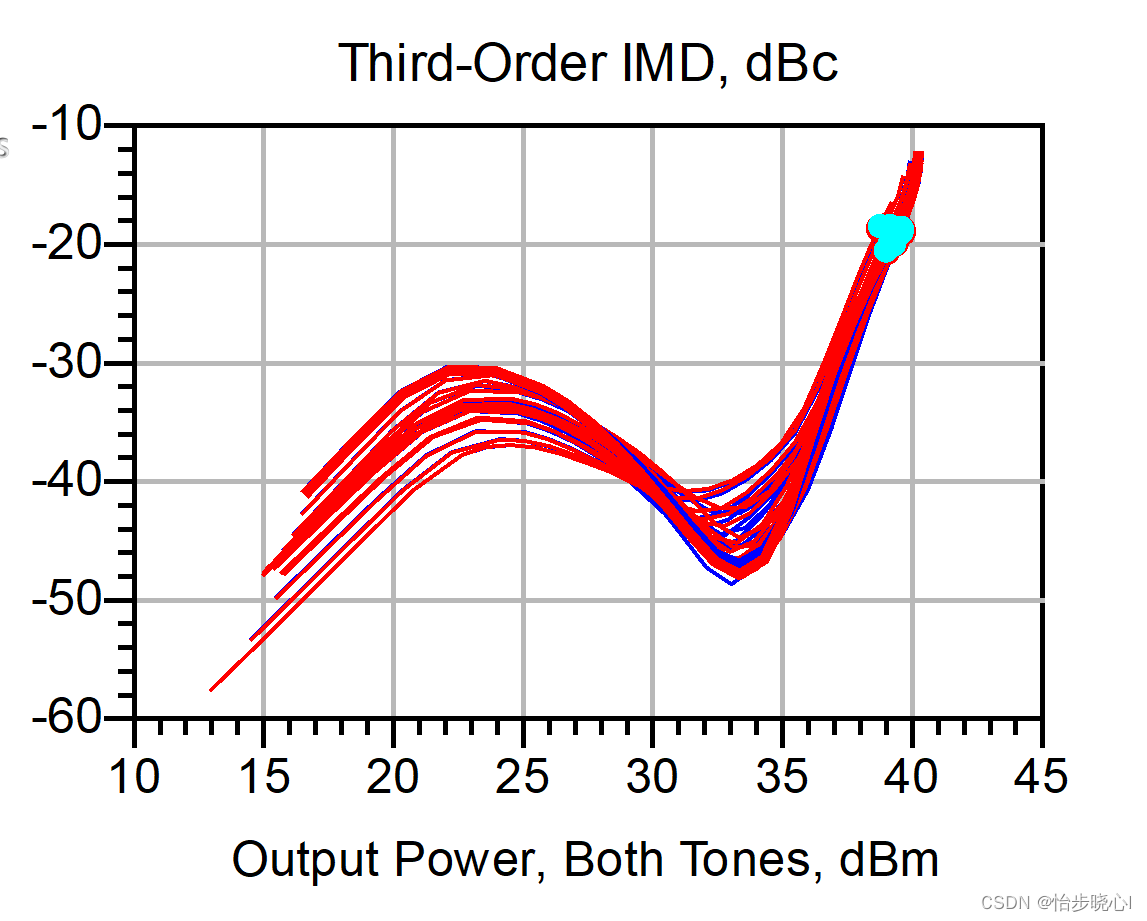

本文的电路仿真基于 TSMC 0.18μm 工艺库,运用仿真工具 Cadence Spectre 仿真软件进行仿真的,该工艺的电源电压为1.8V。本次 PFD 仿真的测试图如4-2-11所示,脉冲发生器 V16、V17 分别接鉴频鉴相器的 A、B端,分别代表的是参考信号 f r e f f_{ref} fref和 VCO 输出信号 f d i v f_{div} fdiv。

PFD测试电路图

图4-2-12给出了当信号 A 相位超前于 B 信号时的仿真结果。根据上述原理可知,当 A 超前 B 时,在 QA 端将会产生一个跟相位差相关的高电平,直到 B 上升沿到来之时结束恢复为低电平,由于逻辑门传输的延时问题,QB 端在 B 信号上升沿到来时也会有一个短暂的脉冲。仿真的结果表明实验仿真与理论分析一致。

(1)A超前B

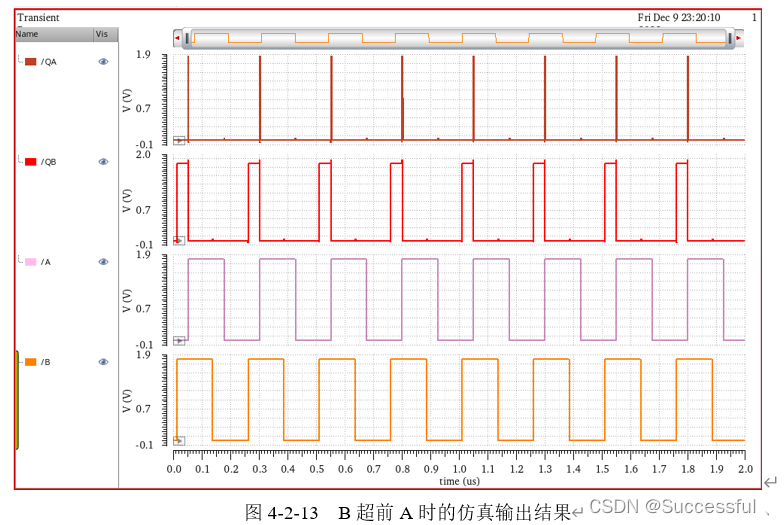

同理,信号 B 相位超前信号A相位时仿真结果如图4-2-13所示,其中,脉冲 QA 的存在时必要的,该脉冲传递给 CP 后,经过低频滤波产生恒定的静态电平,使得 VCO 处于合适的静态点 VDD/2,从而确保 VCO 有最大的调频范围。经分析知仿真结果与原理相符。

(2)B超前A

参考文献:

[1]李智群, 王志功. 射频集成电路与系统[M]. 科学出版社,2008.

[2]毕查德・拉扎维. 模拟CMOS集成电路设计[M]. 西安交通大学出版社, 2003.

[3]聂礼通. 射频锁相环中鉴频鉴相器和电荷泵的设计[D].东南大学,2016.

[4]谢吉辉. CMOS锁相环频率综合器的研究与设计[D].重庆邮电大学,2020.

[5]阮予. 超宽频锁相环频率综合器的关键技术研究[D].西安电子科技大学,2020.

| 分割线 |

各部分链接链接:

频率综合器(Frequency Synthesizer,FS)设计 链接:【模拟集成电路】频率综合器(Frequency Synthesizer,FS)设计

电荷泵(CP)设计 链接:【模拟集成电路】电荷泵(CP)设计

压控振荡器(VCO)设计 链接:【模拟集成电路】宽摆幅压控振荡器(VCO)设计

环路滤波器(LPF)设计 链接:【模拟集成电路】环路滤波器(LPF)设计

分频器(DIV_TSPC)设计 链接:【模拟集成电路】分频器(DIV_TSPC)设计