应用于无线局域网的频率综合器设计

- 前言

- 频率综合器简介

- 各部分链接链接:

前言

本文主要内容是对频率综合器或称为PLL 做出简单介绍,为课程设计部分章节内容,后需给出各部分的设计方案,以及测试结果。

频率综合器简介

无线收发系统中的**频率综合器(Frequency Synthesizer,FS)**模块是影响无线收发系统信号质量的一个重要因素,担负着为系统提供高精度、高稳定度频率的任务。频率综合器常见的结构有如下三种:直接模拟频率合成器(Direct Analog Synthesis,DAS)、锁相环频率合成器(Phase-Locked Loops,PLL)以及直接数字频率合成器(Direct Digital Synthesizers,DDS)。

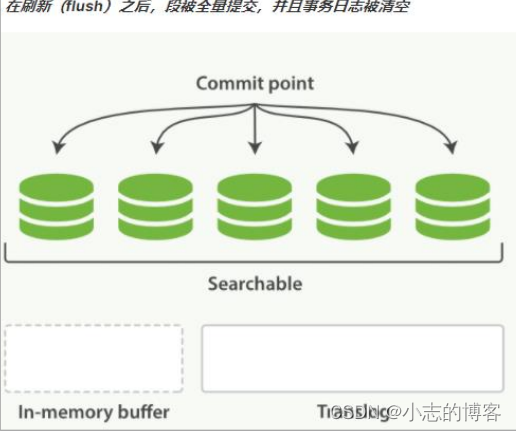

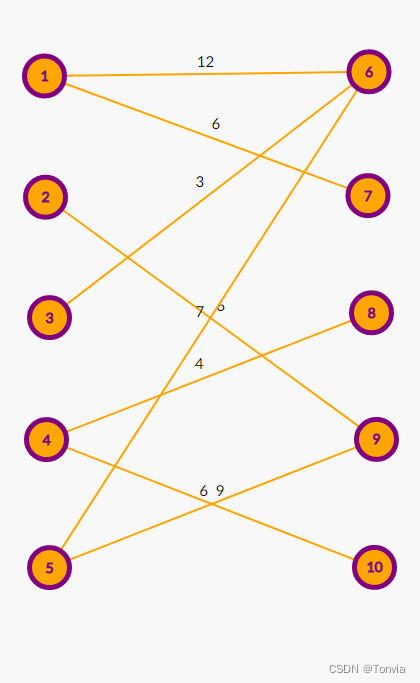

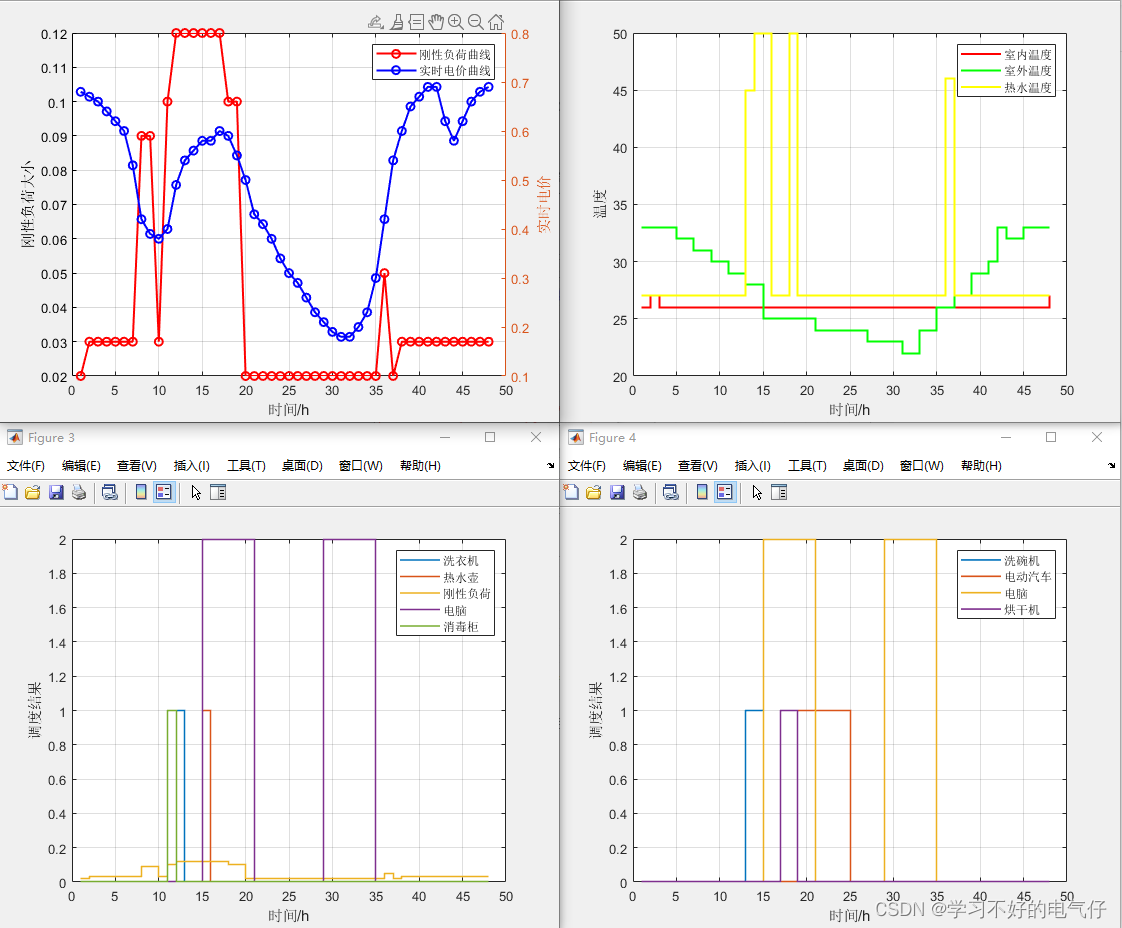

最典型的锁相环频率合成器是电荷泵锁相环频率综合器(Charge-Pump Phase-Locked Loop, CPPLL),它具有工作频率高、相位噪声好、频谱纯度高、低功耗、易于集成等优点,是现今应用范围最广泛的频率合成方式。如下图4-1-1所示,本次所设计的电荷泵锁相环频率综合器主要由如下模块组成:鉴频鉴相器(Phase Frequency Detector,PFD)、电荷泵(Charge Pump,CP)、压控振荡器(Voltage Controlled Oscillator,VCO)、环路滤波器(Loop Filter,LPF)和分频器(Divider,DIV) 。

各个模块相互连接构成一个环路,其工作过程为如下:

在环路的左端,输入信号

f

r

e

f

f_{ref}

fref 和反馈信号

f

d

i

v

f_{div}

fdiv 被同时输入到 PFD 中,PFD 探测到它们的相位差,并以电压信号的形式输出到下一级,电压的大小与相位差成正比;

CP将PFD的输出离散电压转变成对后级LPF的充放电流,电流大小与电压值成正比;

CP 对 LPF 中的电容充放电使得 LPF 的输出电压

V

c

t

r

V_{ctr}

Vctr大小产生变化,VCO 的输出频率与 V_{ctr} 大小成正比,当

V

c

t

r

V_{ctr}

Vctr 发生变化时,

f

o

u

t

f_{out}

fout亦随之改变;

分频器对 VCO 的输出频率进行N次分频后得到与

f

r

e

f

f_{ref}

fref 进行比较的

f

d

i

v

f_{div}

fdiv 信号,当环路锁定时,有如下关系式:

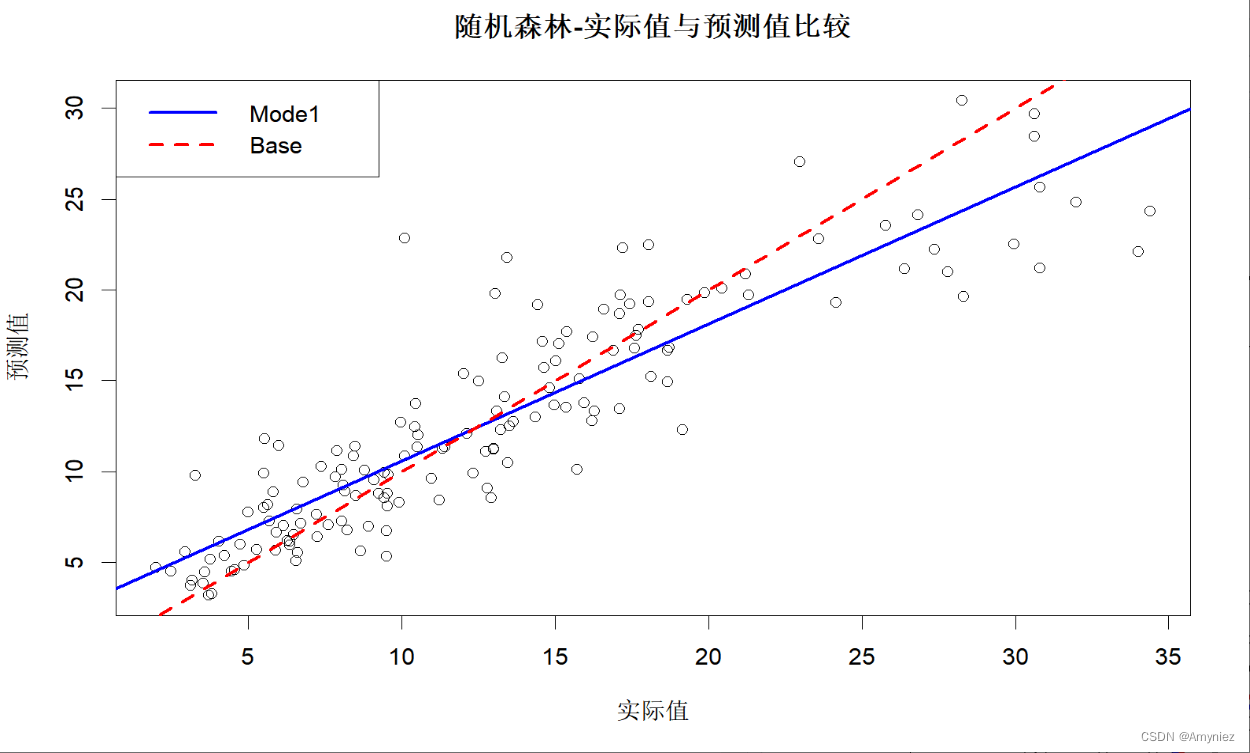

其相位的线性模型可用下图4-1-21来表示:

PFD 和 CP 电路模块是完成输入信号与压控振荡器输出信号之间相位差到电压的转换。PFD 比较输入信号的相位

θ

i

θ_i

θi 与反馈信号的相位

θ

f

b

0

θ_{fb0}

θfb0 的相位,得到相位差

θ

e

θ_e

θe,再通过CP把这个相位差

θ

e

θ_e

θe 转化为正或负的输出电流,从而实现对环路滤波器的充放电。当 CP 的充放电电流值大小为

I

c

p

I_{cp}

Icp 时,线性相位模型为:

环路滤波器的功能是将 PFD 和 CP 产生的代表相位差的充放电电流转换成电压

V

C

V_C

VC,这个电压就是压控振荡器的控制电压。这个电压的变化将控制压控振荡器的输出频率发生变化。设环路滤波器的传递函数为

Z

(

s

)

Z(s)

Z(s),因此环路滤波器的输出,也就是压控振荡器输入端电压的表达式为:

压控振荡器是频率受电压控制的振荡器,控制电压和 VCO 输出频率之间的关系通常用压控振荡器的压控增益 K v c o K_{vco} Kvco 来表示。即:

但在 PLL 线性相位系统中的变量是相位,又因为瞬时角频率是其相位对时间的倒数,所以 VCO 输出信号的瞬时相位为:

因此在 s 域中,时域上的积分就是增加一个 s=0 的极点。在压控振荡器的线性化相位模型表达式为:

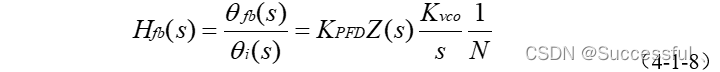

环路分频器对VCO的输出相位

θ

o

θ_o

θo 进行N分频后反馈到PFD的输入端并且得到反馈相位

θ

f

b

θ_{fb}

θfb:

综上,可以得到图4.2所示的线性相位模型的相位传输函数:

| 分割线 |

各部分链接链接:

鉴频鉴相器(PFD)设计 链接:【模拟集成电路】鉴频鉴相器设计(Phase Frequency Detector,PFD)

电荷泵(CP)设计 链接:【模拟集成电路】电荷泵(CP)设计

压控振荡器(VCO)设计 链接:【模拟集成电路】宽摆幅压控振荡器(VCO)设计

环路滤波器(LPF)设计 链接:【模拟集成电路】环路滤波器(LPF)设计

分频器(DIV_TSPC)设计 链接:【模拟集成电路】分频器(DIV_TSPC)设计