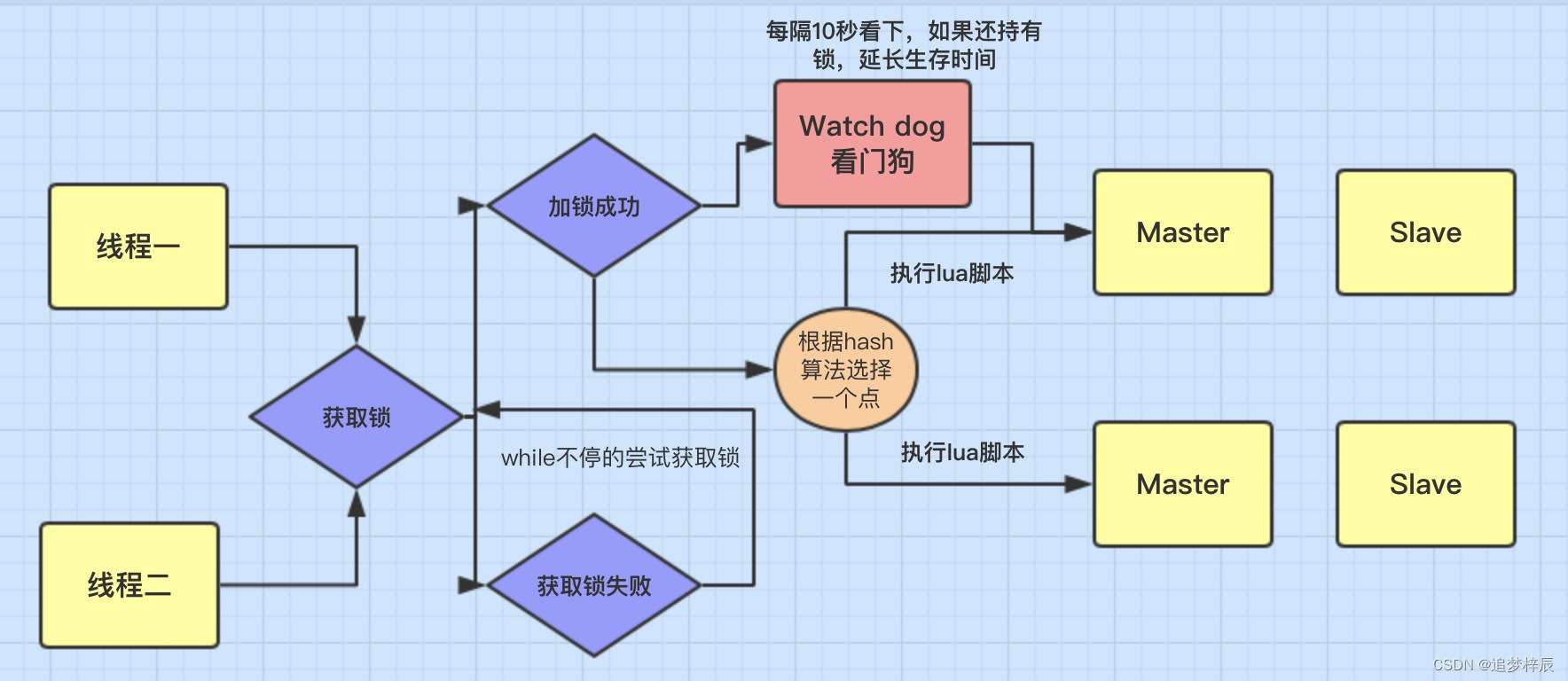

一、原理图编译

原理图检查的主要内容有:

1、元件位号冲突。也即多个元件编号相同,例如两个电容在原理图中都被命名为C2,显然肯定是无法生成PCB的。

2、网络悬浮。也即网络标号没有附着在电气走线上,一般这种是人操作失误,又容易被忽视。如果注意不到会造成生成的PCB中某些线连接不上。

3、电源悬浮。也即图中有些VCC和GND跟谁都不连接。。

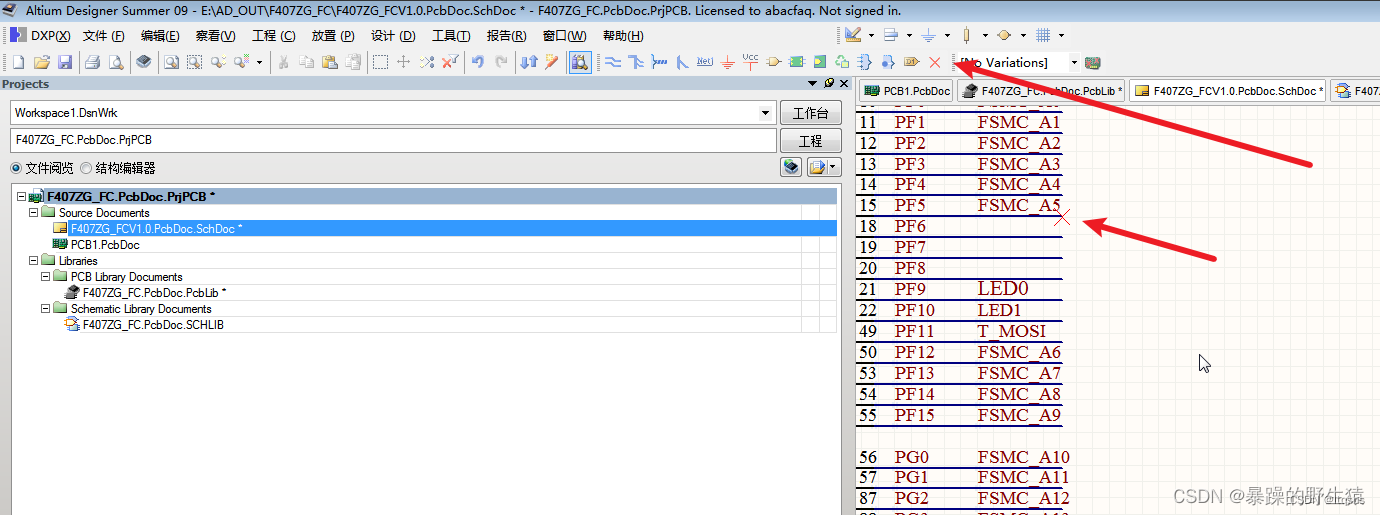

4、单端网络。例如MCU上有一个引脚引出的电气线标注了网络标号I2C1_SCL,但在图中仅此一个标号,一般这种是人疏忽忘记连接对应的元件了,建议检查。(除非设计人员故意就是想要一个单端网络)。

以上这些是日常设计时容易出错的几个地方,建议把这些检查内容设置为“严重警告”或“致命错误”,以便让AD帮我们自动识别这些易错点。除了以上这些,还有一些别的致命错误,AD都已经默认使能了,不再赘述。

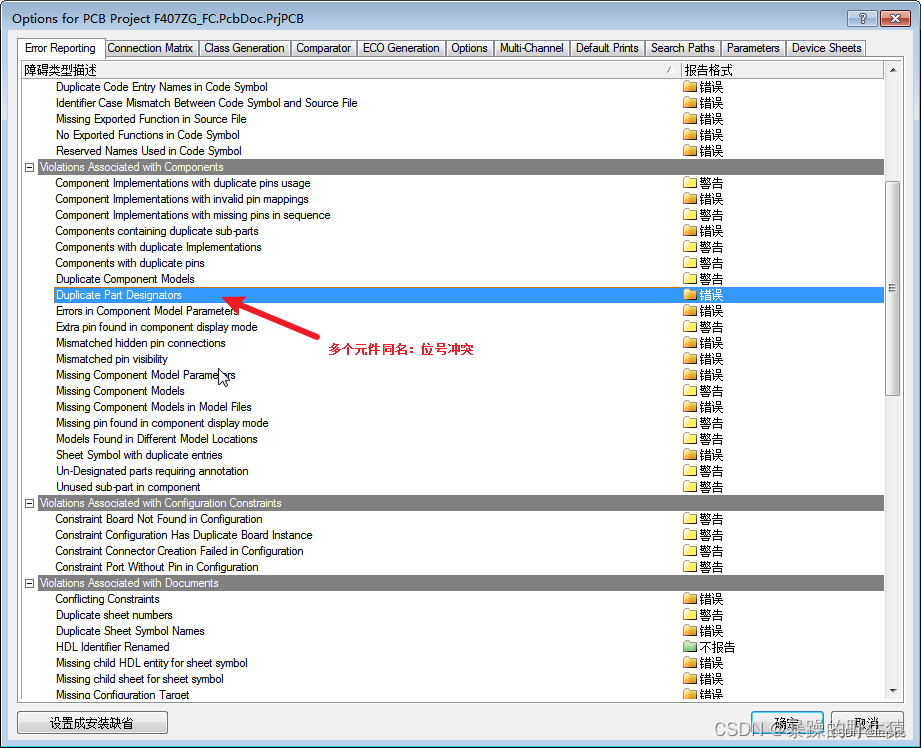

1、右击目录树中的工程,选择工程参数,如下图。或者点击菜单栏->工程->工程参数。

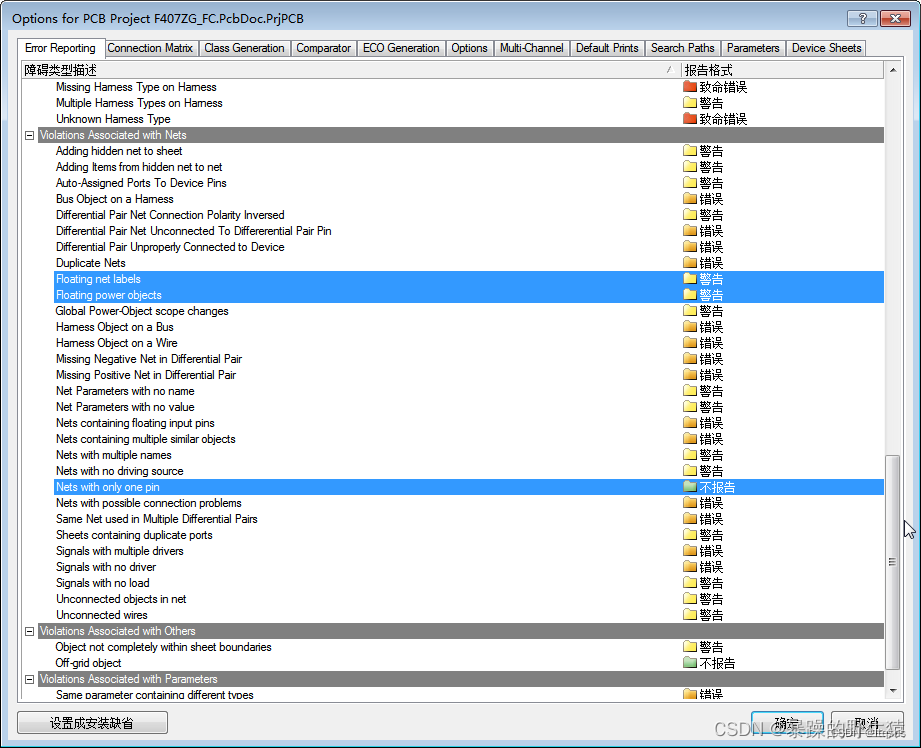

2、把下图的检查项改成“致命错误”。

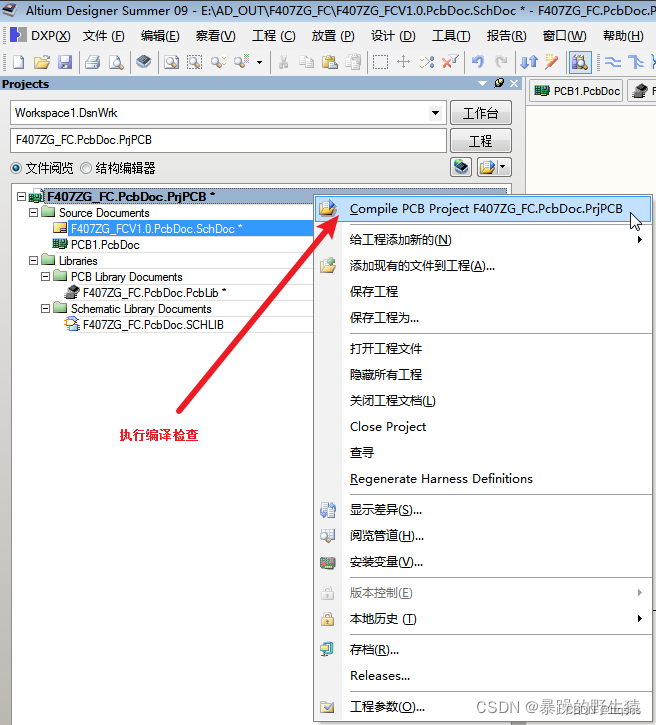

3、右击工程,选择编译。

4、在原理图右下角Panels–>Messages会显示报错的报告。

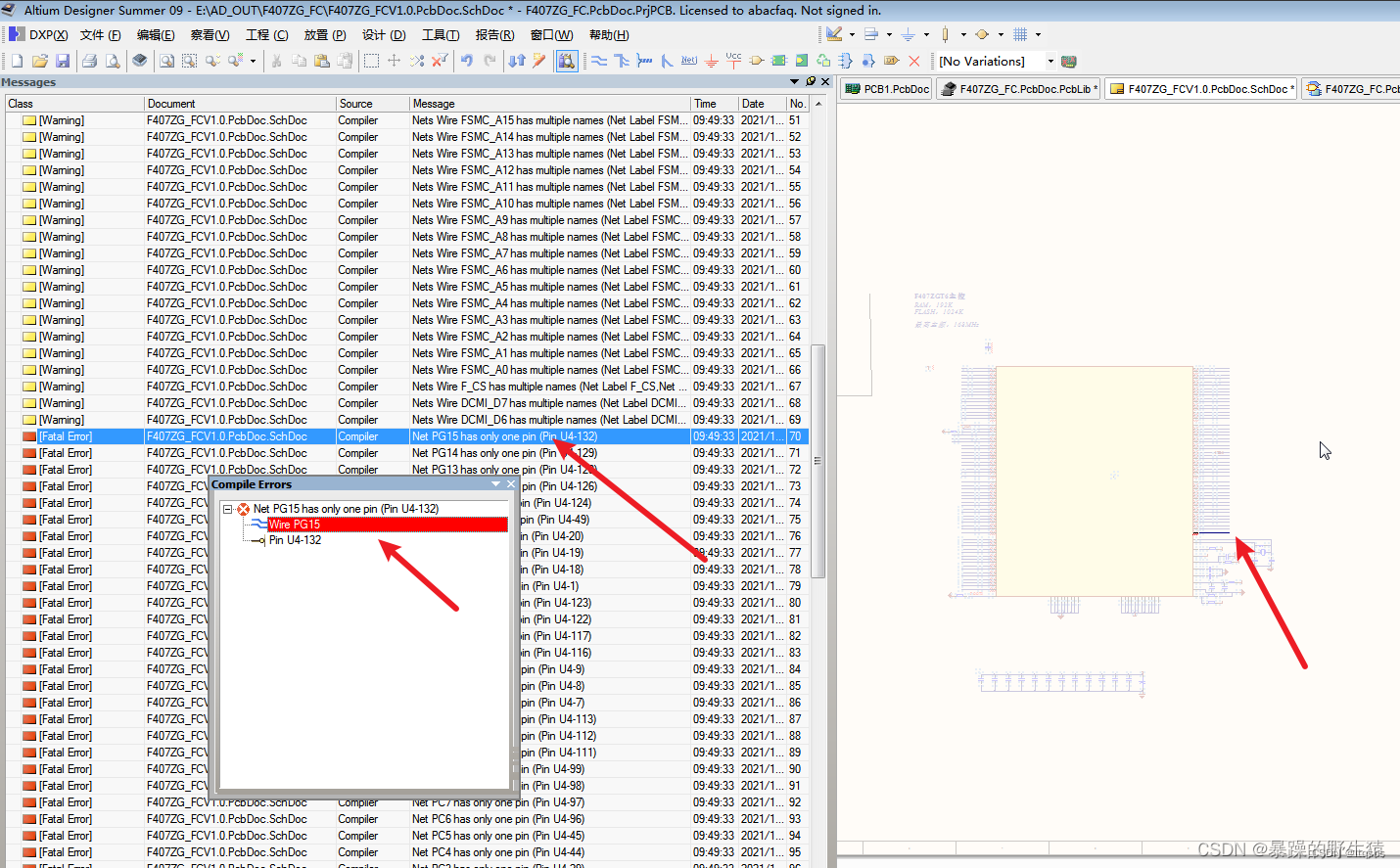

然后AD会把检查的结果,按照上一步骤的设置,给报告出来。如下图所示。

我的MCU很多引脚没有连东西,AD报告了很多“单端网络”的错误,双击这条错误,可以看到原理图区高亮了这个没有被连接的MCU引脚。

参考原文:《Altium designer原理图检查(编译检查)》

二、PCB DRC检查

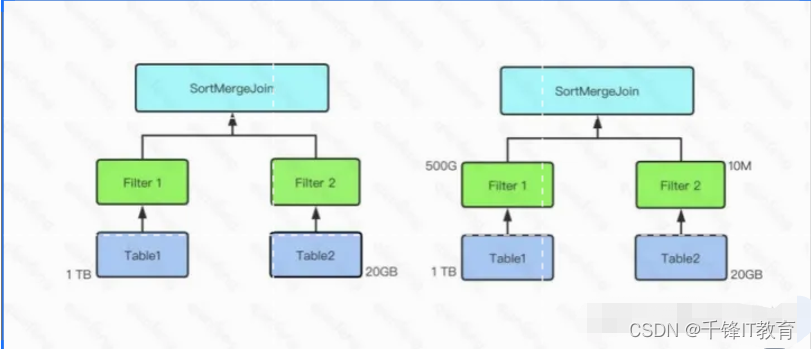

DRC就是检查设计是否满足所设置的规则。需要检查什么,其实都是和规则相对应的,在检查某个选项时,请注意对应的规则是否使能打开。

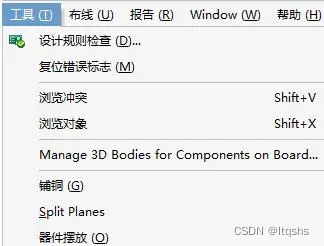

(1)执行菜单命令“工具-设计规则检查(快捷键“TD”),如图11-1所示,打开如图11-2所示的设计规则检查器。

图11-1 打开DRC设置命令

图11-2 设计规则检查器

① 创建报告文件:执行完DRC之后,Altium Designer会创建一个关于DRC的报告,对报错信息会给出详细的描述并会给出报错的位置信息,方便设计者对报错信息进行解读,如图11-3所示。

图11-3 DRC详细报告内容

② 停止检测50000冲突找时:表示当系统检测到50000个DRC报错的时候直接停止再检查,系统默认设置一般是500,但是设置到500时有些DRC会进行显示,有些DRC不会进行显示,只有修正已存在的错误,再次DRC的时候才会显示,这样对于大板设计非常不方便。

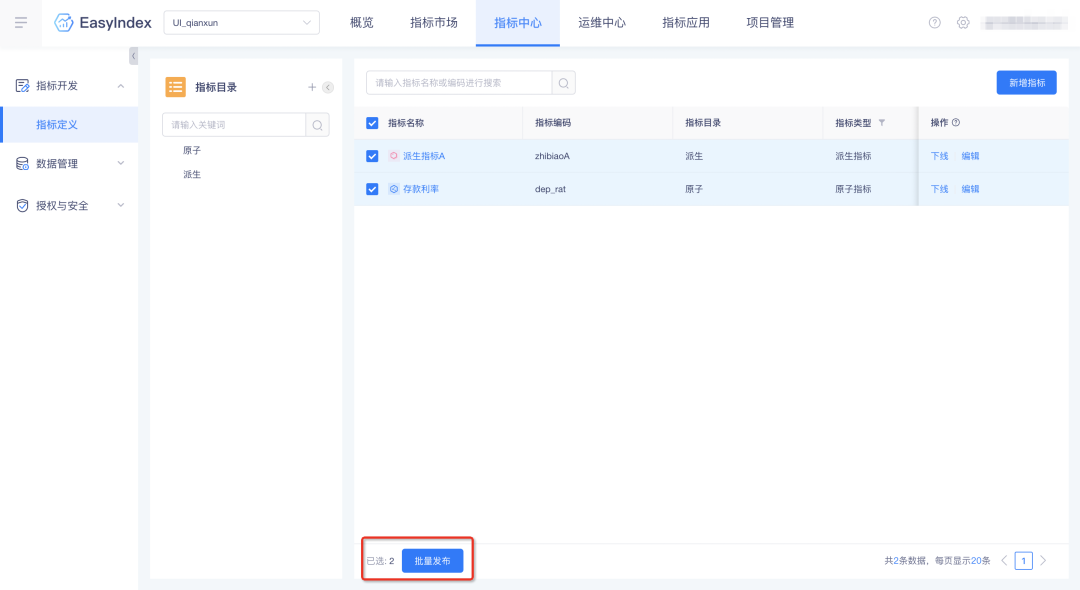

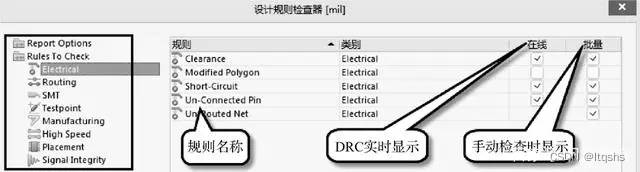

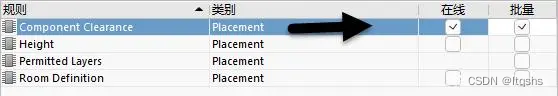

(2)设置DRC检查选项,如图11-4所示,选择需要检查的规则项,在“在线”和“批量”栏中勾选使能检查。

① 在线:当PCB设计当中存在DRC报错时可以实时地显示出来。

② 批量:只有手工执行DRC时,存在问题的报错才会显示出来。

一般来说,需要进行DRC的时候两者都进行勾选,方便实时检查和手动检查同时进行。

图11-4 设置DRC检查选项

DRC不是说所有的规则都需要检查,设计者只需要检查自己想要检查的规则即可,不想检查的规则对应的“在线”和“批量”取消勾选就好了。下面对常见的几种DRC进行详细的描述。

电气性能检查

电气性能检查包括间距检查、短路检查及开路检查,如图11-5所示,一般这几项都需要勾选,对应的常见问题报错如图11-6所示。

图11-5 电气性能检查设置

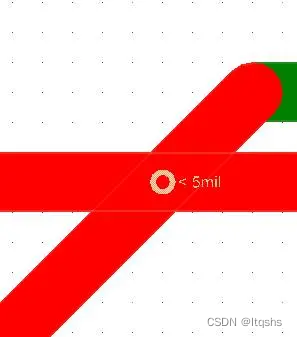

(a)间距报错

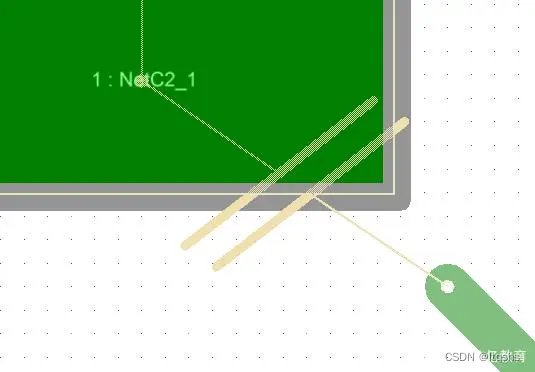

(b)开路报错

(c)短路报错

图11-6 常见电气性能DRC报错

布线检查

如图11-7所示,布线检查包含阻抗线检查、过孔检查、差分线检查,当设置的线宽、过孔大小及差分线宽不满足规则约束要求时就会提示DRC报错,让设计者注意。

图11-7 阻抗线检查、过孔检查、差分线检查设置

一般在设计中,过孔的类型不要超过两种,这样再生产的时候可以少用钻头类型,提高生产效率。

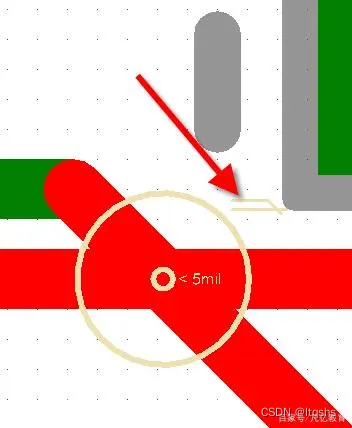

Stub线头检查

虽然我们会对走线进行一些优化,但是考虑到还要人工进行布线处理,难免会对走线的一些线头有遗漏,这种线头简称Stub线头。Stub线头在信号传输过程中相当于一根“天线”,不断地接收或发射电磁信号,特别是高速的时候,容易给走线导入串扰,所以有必要对Stub线头进行检查,并在设计中进行删除处理,如图11-8所示。

图11-8Stub线头检查

天线公差:设置“天线”长度报错范围,一般设置为1mil。

丝印上阻焊检查

阻焊是防止绿油覆盖的区域,会出现露铜或者露基材的情况,当丝印标识放置到这个区域时,会出现缺失的情况,需要对丝印上阻焊进行例行检查,如图11-9所示,需要对其规则进行设置,并且勾选DRC检查选项。

(1)检查到裸露铺铜的间距:检查丝印到铜皮的间距。

(2)检查到阻焊开窗的间距:检查丝印到阻焊开窗的间距,一般选择设置这项。

(3)对象与丝印层的最小间距:丝印到阻焊的最小间距,一般设置为2mil。

图11-9 丝印上阻焊的设置与检查

元件高度检查

因为考虑到PCB布局存在限高要求,这种情况须对高度等进行例行检查。元件高度检查需要元件封装设置好高度信息、设置好高度检查规则及适配范围(全局还是局部),并勾选高度检查,如图11-10所示。

图11-10 元件高度检查

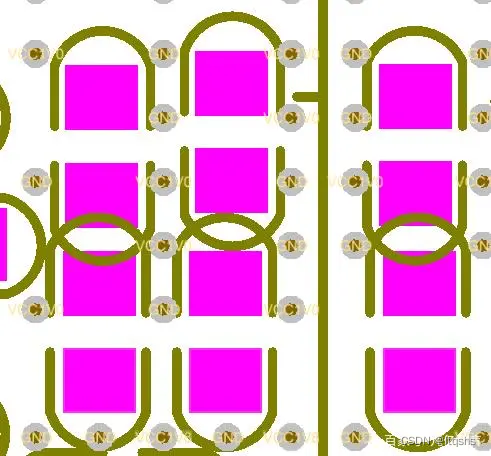

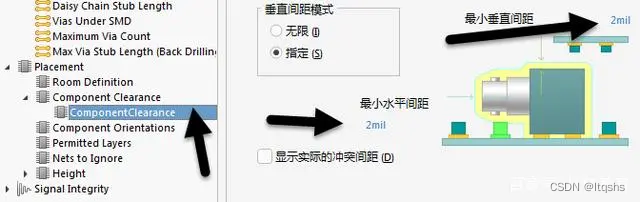

元件间距检查

大部分板子设计都是手工布局,难免存在元件重叠的情况,需要对元件间距进行检查,防止后期元件装配时出现干涉,如图11-11和图11-12所示。

(1)最小水平间距:元件与元件的最小水平间距,一般设置为2mil。

(2)最小垂直间距:元件与元件的最小垂直间距,一般设置为2mil。

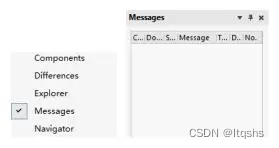

对上述常见的DRC检查选项设置勾选之后,执行DRC菜单左下角的“运行DRC”命令,运行DRC,等待几分钟之后,系统会生成一个DRC报告,详细列出错误内容及位置,如图11-13所示;或者回到PCB设计交互界面,在右下角执行命令“Panels-Messages”,如图11-14所示,同样可以查看DRC类型。一般情况下都是采用第二种方法来进行查看。

图11-11 常见的元件重叠情况及元件间距规则设置

图11-12 元件间距检查

图11-13 DRC报告

图11-14 Messages报告

用鼠标双击Messages里面的DRC报告选项,可以弹跳到PCB报错位置,可以有针对性地对这个DRC报错修正,可以接受的DRC报错可以直接忽略。例如,焊盘在禁止布线层边线上,会出现间距报错,这种可以直接忽略不管。

重复上述步骤直到所有DRC报错更改完成,没有DRC报错或者所有DRC报错可以忽略为止,即完成DRC。PCB电路设计通过DRC,可以进行下一步骤。

参考原文:《硬件工程师基本功:DRC设置要点详解》