How To Write EMX PROC File

编写EMX工艺文件需要2方面的信息:

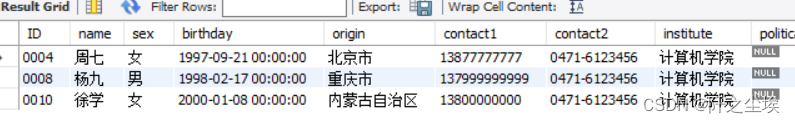

- GDSII layer number and type 映射到 layer name。

这个信息可以从layermap文件中获取;EMX的manual有相应的介绍,这个过程十分基础且简单容易,简单说就是把GDSII中数字编号的layer转换成人眼认识的字符,例子中L代表layer number,T代表type;除此之外可以用GDSII中的布尔运算符来定义layer的几何关系,例如+ (union),* (intersection), ^ (exclusive-or, or symmetric difference), - (difference), and !(complement)。

与metal相关的操作常见有fill,fill表达式用来去除小于一定面积的几何形状,有些制程会填充dummy来满足density DRC的要求,如果想去除dummy金属来run EMX,可以使用fill来操作,例如define M1=fill(L39T0,3um)就会去除L39T0小于3um by 3um的形状,参数设为0为不简化。

在定义VIA的几何形状时,使用merge表达式更有效率,比如GDSII层次L48T1上的VIA 标准pitch=0.3um,可以写define contact = merge(L48T1,0.3um)。一般工艺的design rule会要求画很多VIA的阵列,而不是一个长长的大大的VIA,但是这对EMX来说不太友好,所以EMX会选择把VIA挨得比较紧的阵列拼接起来处理,上面提到的0.3um就是距离远近的判断,如果不想拼接,可以把这个值设为0。详情可以搜索EMX manual中的merge和--via-separation. 和VIA相关的操作还有count:有些工艺的VIA阻值通过ohm per via给出,那么EMX可以通过count操作来计算VIA阻值,例如:

define co=count(merge(L48T1,0.3um))

via poly m1 10ohm/via co

这不影响EMX识别VIA的几何特征,只是VIA的计算方法有所改变。

- 衬底堆叠信息和各层之间的厚度/介电常数/电导率/磁损耗角正切。

可以从ICT (QRC), ITF (STARRC)或者TSMC的IRCX文件中获取工艺信息手动编写(TSMC也提供parser脚本完成IRCX到PROC的转换,但是作为主宰一切的设计人员,同样需要review脚本产生的文件,避免踩坑)。

下面简单介绍如果编写层次和导体的描述。

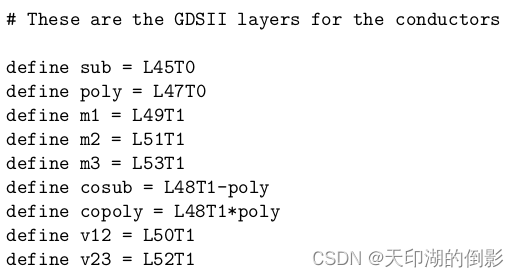

EMX的manual在开篇就提供了一个简单的proc file example以及对应的堆叠关系。Proc file从底层向顶层描述堆叠信息。Layer之间是无缝堆叠的,而metal镶嵌在layer中,因此正确描述metal在layer中的位置就很关键,会影响到EMX的建模准确性。

这个例子很好的解释了一个关键表达式:offset; offset表达式通常用来确定金属的起始位置/结束位置,或者说下平面和上平面的位置;offset的逻辑是这样的,以offset定义前的最后一个layer的下平面作为起始点,加上之前所有offset数值之和的偏移量作为当前位置,那么例子中的第一个offset 0.6就意味着poly的起始位置为5um厚度介质的起始位置500um处+0.6um,第二个offset 1就是500um处+0.6um+1um;

和offset类似有position表达式,和offset表征相对值不同,position后的数值表示相对于之前最后一个layer起始位置的绝对距离。例如:layer xxx, offset 1.3um, position 1um将当前位置设置到了layer xxx起始点上方1um的高度。

如果工艺厂提供了ICT文件,可以直接使用QRC/EXT下的ictviewer + ictfile来观察层次关系,效果如下图所示。从图中可以清晰看到M7终止于layer IMD7d的起始点,可以认为M7淀积完成后去除光刻胶再填充IMD7c研磨了一下,M7的上表面和IMD7c一样平整,蚀刻/淀积的bottom位置也许很难保证,而CMP却可以保证金属的上表面位置,因此可以用position来描述这里的M7:

layer name IMD7d

position -M7_thickness #注意负号,这里相对于IMD7d的起始位置回退了M7厚度

conductor M7_thickness M7_RSH M7 #再加上M7厚度,最终M7和IMD7d的起始点齐平

如何具体描述一个metal和一个VIA?当然所有信息都来自ITF或者ICT或者IRCX文件,这3个文件只是编写格式略有不同,内容基本一致。

一个简单的metal描述如下:

conductor thickness Resistive_val metalname,

e.g.: conductor 0.08 0.4 M1表示M1金属厚度80nm,方块电阻0.4ohm。如此简单似乎无须赘述,但是只要浏览ITF文件就可以看到thickness和阻值特性并非一个固定的值,先进制程下的金属厚度和金属density以及金属宽度width息息相关,而电阻率又和thickness以及width相关,因此ITF/ICT/IRCX给出了thickness变化量的求解方法,一般采用多项式拟合,而RHO/RSH则采用查找表。如何理解这些计算方法可以参考一篇博文https://ileonsun.github.io/understanding-itf/,或者阅读starrc的manual,博文中的内容贴在附页中。

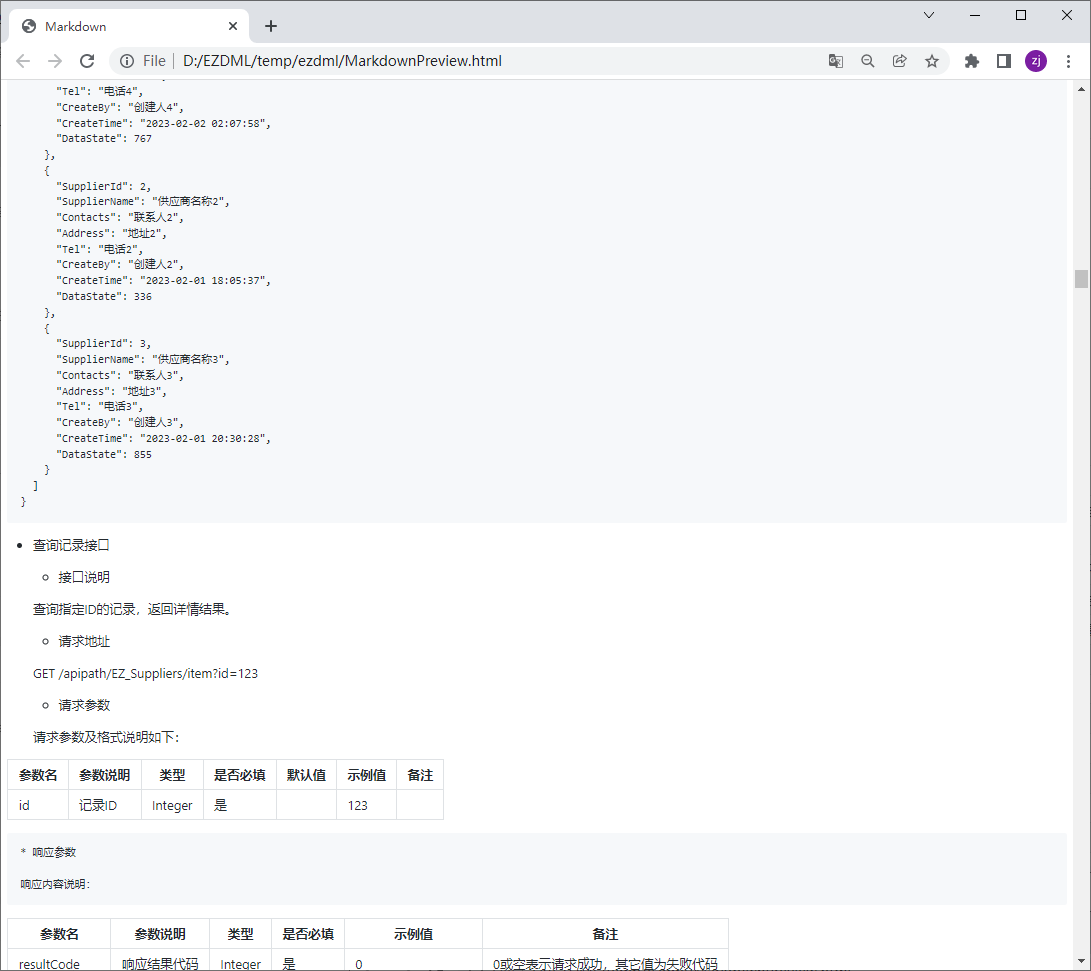

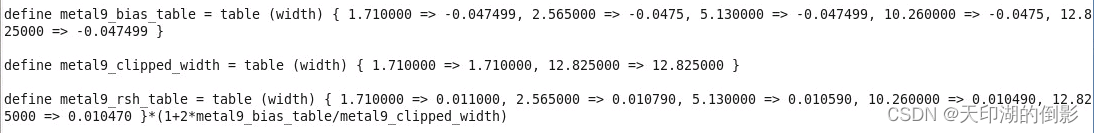

对于一个详尽的proc文件来说,需要包含ITF文件中的所有conductor信息,而EMX也支持查找表的形式。不确定EMX是否支持计算density再计算thickness再计算Rsh的方式,width/spacing的查找表是支持的,如果前者不支持就需要人员或者脚本先计算好width/spacing的查找表,再录入到proc文件中。一个包含查找表的AP金属层定义如下:

![]()

Bias的定义具体可以参考EMX manual,其描述了在不同width/space时的真实线宽。

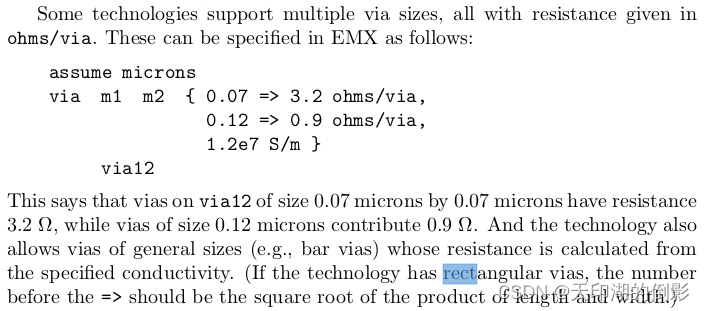

关于VIA的描述,manual上一段话可以很好地概括:

建议遵循这个例子去描述VIA,如果版图中有不规则的VIA,比如旋转45度的VIA,而没有定义general size的阻值信息(1.2e7 S/m),那么EMX就会报错VIA不是方形而找不到必须的阻值信息。

S/m到欧姆的计算法如下:电阻率=电导率的倒数,电阻=电阻率 x VIA的高度/截面积,VIA高度可以从堆叠信息中推算。试算了一下某28nm厚金属到铝的孔,高度775nm,边长2.56um,电导率2.8e6 S/m, 则电阻=0.775/(2.8*2.56^2)=0.042,和工艺文档吻合。

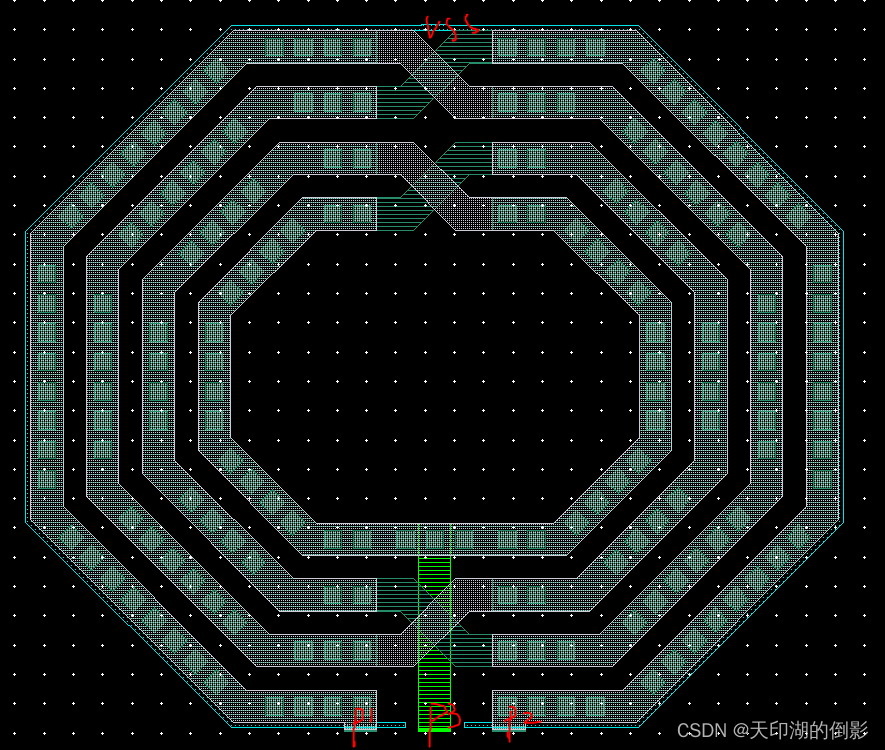

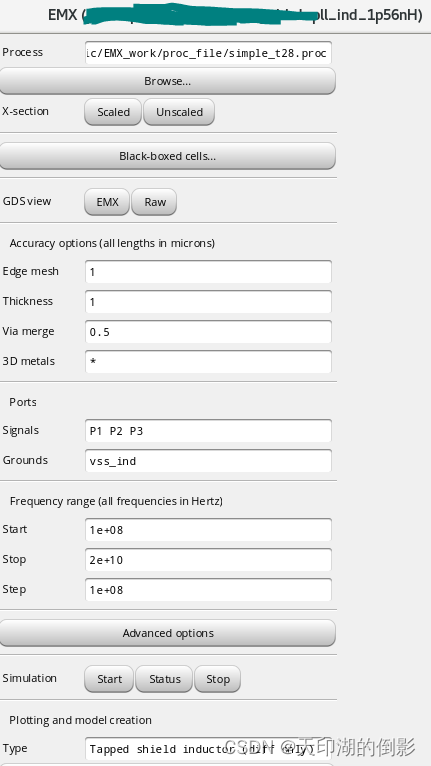

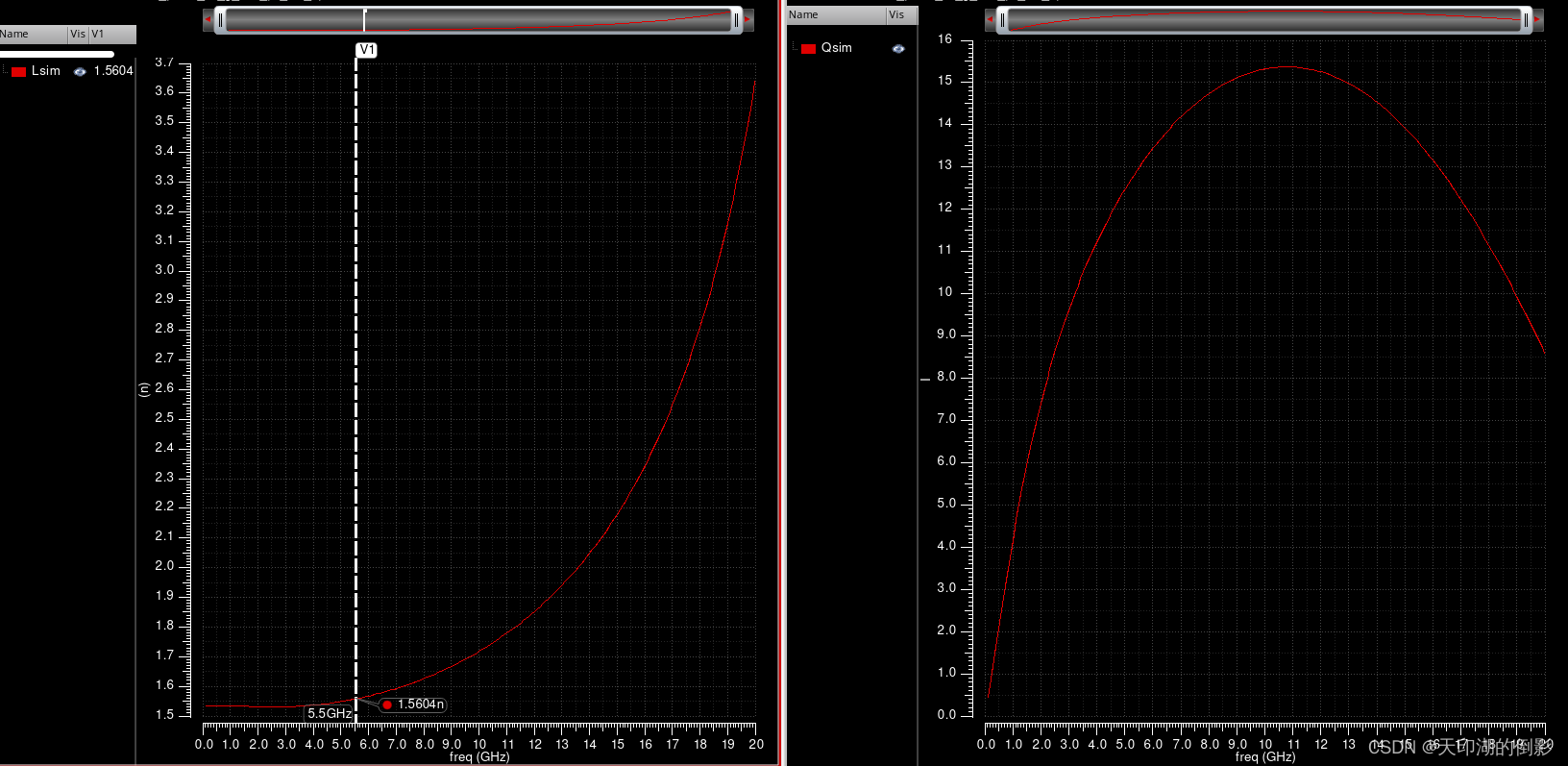

利用手写的某28nm的proc文件,metal和via只有中心值而不带查找表,EMX仿真一个PLL的电感,设计标称1.56nH,结果如下:

EMX还可以仿真传输线

备注一些PCB的参数:

一般单、双面PCB板铜箔(覆铜)厚度约为35um(1.4mil),另一种规格为50um和70um。多层板表层厚度一般为35um=1oz(1.4mil),内层17.5um(0.7mil)。

| 一.不同介质厚度及其不同组合方式 | ||||

| 序号 | 理论厚度(MM) | 理论厚度(MIL) | 组合方式 | 介电常数 |

| 1 | 0.05 | 1.97 | 106*1 | 3.9 |

| 2 | 0.07 | 2.76 | 1081*1 | 4.2 |

| 3 | 0.08 | 3.2 | LPP1080*1 | 4.2 |

| 4 | 0.1 | 4 | 106*2 | 3.9 |

| 5 | 0.12 | 4.72 | 106+1080 | 4.2 |

| 6 | 0.12 | 4.72 | 2116*1 | 4.2 |

| 7 | 0.14 | 5.5 | 1080*2 | 4.2 |

| 8 | 0.15 | 6 | 106*3 | 3.9 |

| 9 | 0.17 | 6.7 | 2116+106 | 4.2 |

| 10 | 0.17 | 6.7 | 1080+106*2 | 4.2 |

| 11 | 0.19 | 7.5 | 1080+2116 | 4.2 |

| 12 | 0.19 | 7.5 | 7628*1 | 4.5 |

| 13 | 0.21 | 8.27 | 1080*3 | 4.2 |

| 14 | 0.22 | 9 | 106*2+2116 | 4.2 |

| 15 | 0.24 | 9.45 | 7628+106 | 4.5 |

| 16 | 0.24 | 9.45 | 2116*2 | 4.2 |

| 17 | 0.26 | 10.24 | 7628+1080 | 4.5 |

| 18 | 0.26 | 10.24 | 1080*2+2116 | 4.2 |

| 19 | 0.29 | 11.42 | 7628+106*2 | 4.5 |

| 20 | 0.29 | 11.42 | 2116*2+106 | 4.2 |

| 21 | 0.31 | 12.2 | 7628+2116 | 4.5 |

| 22 | 0.31 | 12.2 | 2116*2+1080 | 4.5 |

| 23 | 0.33 | 13 | 7628+1080*2 | 4.5 |

| 24 | 0.38 | 15 | 7628*2 | 4.5 |

| 25 | 0.43 | 16.93 | 7628+2116*2 | 4.5 |

| 26 | 0.43 | 16.93 | 7628*2+106 | 4.5 |

| 27 | 0.45 | 17.72 | 7628*2+1080 | 4.5 |

| 28 | 0.5 | 19.69 | 7628*2+2116 | 4.5 |

| 29 | 0.57 | 22.44 | 7628*3 | 4.5 |

附录Understanding ITF file:

至https://ileonsun.github.io/understanding-itf/可在线阅读

$$ 省略文件头和AP,M8比较有代表性。

$$ PS:itf中用$注释

DIELECTRIC PASS2 {THICKNESS=0.668210 ER=4.2 }

DIELECTRIC PASS1 {THICKNESS=0.071590 ER=7.1 }

DIELECTRIC IMD8c {THICKNESS=0.778950 ER=4.2 }

DIELECTRIC IMD8b {THICKNESS=0.051500 ER=7.1 }

DIELECTRIC IMD8a_A {THICKNESS=0.055000 ER=4.2 }

$$ 上面5行说明AP/M8之间有5层绝缘层,THICKNESS为该层厚度,ER为该层相对介电常数ε。

$$ 介电常数ε也被称为电容率,理想金属导体的ε应该是正无穷。

$$ 金属导线的cap值就是和这些绝缘层的ε有关。

CONDUCTOR M8 {THICKNESS= 0.885450

CRT1=3.890e-03 CRT2=-1.500e-07

$$ 这两个值用来计算temperature variation时的电阻, temperature-dependent resistance 为T的二次多项式,如下:

$$ R= CRT2*(T-T0)^2 + CRT1*(T-T0) + R0

SIDE_TANGENT = 0.046869

$$ 理想情况下,金属层的截面应该是规则矩形,但是沉积过程引起的偏差,可能会导致截面为梯形(上宽下窄或上窄下宽)

$$ SIDE_TANGENT指的就是截面斜边偏移角度的正切值(tanΘ);正值表示上宽下窄,负值表示上窄下宽

$$ 这里,我们可以计算得出M8截面是个底角2.68°的上宽下窄的梯形。

POLYNOMIAL_BASED_THICKNESS_VARIATION {

$$ 这部分描述的是工艺过程中M8后端偏差,该值是基于density和width的多项式

DENSITY_POLYNOMIAL_ORDERS { 4, 3, 2, 1, 0 }

$$ 多项式中density的指数

WIDTH_POLYNOMIAL_ORDERS { 4, 3, 2, 1, 0 }

$$ 多项式中width的指数

WIDTH_RANGES {0.9 10.8000}

$$ width分布,这里有两个值,所以下面的多项式系数有三组,分别对应width<=0.9, 0.9<width<10.8, width>10.8的情况

POLYNOMIAL_COEFFICIENTS {

0 -2.09675E+01 4.71013E+01 -3.63903E+01 1.10754E+01

0 2.24127E+01 -5.02114E+01 3.88210E+01 -1.28144E+01

0 -7.76371E+00 1.73158E+01 -1.32161E+01 5.02100E+00

0 9.83830E-01 -2.18583E+00 1.54960E+00 -8.13606E-01

0 -3.44482E-02 7.69210E-02 -3.26943E-02 5.70675E-02

}

$$ 多项式的系数,因为上面density/width指数都有5种,所以多项式有5*5=25项,表格分别为每项的指数,具体为:

$$ delta_thickness =

$$ 0 * D^4W^4 + -2.09675E+01 * D^3W^4 + 4.71013E+01 * D^2W^4 + -3.63903E+01 * D^1W^4 + 1.10754E+01 * D^0W^4

$$ 0 * D^4W^3 + 2.24127E+01 * D^3W^3 + -5.02114E+01 * D^2W^3 + 3.88210E+01 * D^1W^3 + -1.28144E+01 * D^0W^3

$$ 0 * D^4W^2 + -7.76371E+00 * D^3W^2 + 1.73158E+01 * D^2W^2 + -1.32161E+01 * D^1W^2 + 5.02100E+00 * D^0W^2

$$ 0 * D^4W^1 + 9.83830E-01 * D^3W^1 + -2.18583E+00 * D^2W^1 + 1.54960E+00 * D^1W^1 + -8.13606E-01 * D^0W^1

$$ 0 * D^4W^0 + -3.44482E-02 * D^3W^0 + 7.69210E-02 * D^2W^0 + -3.26943E-02 * D^1W^0 + 5.70675E-02 * D^0W^0

POLYNOMIAL_COEFFICIENTS {

省略

}

POLYNOMIAL_COEFFICIENTS {

省略

}

}

RHO_VS_SI_WIDTH_AND_THICKNESS {

$$ 这部分表示体电阻率(bulk resistivity),该值是基于width和thickness查表得到

$$ 补充: 如何通过这一项计算RSH? RSH=RHO/THICKNESS=0.023ohm/sq

WIDTH { 0.3240 0.3600 0.3960 0.4320 0.4680 0.5400 0.7200 1.0800 1.3500 1.8000 2.7000 3.6000 4.5000 5.4000 6.7500 8.1000 9.0000 10.8000 }

THICKNESS { 0.5950 0.6800 0.7650 0.8500 0.9350 1.0200 1.1050 1.1900 1.2750 }

VALUES {

0.0206 0.0204 0.0202 0.0201 0.0200 0.0198 0.0196 ...

0.0205 0.0203 0.0202 0.0201 0.0200 0.0198 0.0195 ...

0.0205 0.0203 0.0201 0.0200 0.0199 0.0197 0.0195 ...

0.0204 0.0202 0.0201 0.0200 0.0199 0.0197 0.0194 ...

0.0204 0.0202 0.0201 0.0199 0.0198 0.0197 0.0194 ...

0.0204 0.0202 0.0200 0.0199 0.0198 0.0196 0.0194 ...

0.0204 0.0202 0.0200 0.0199 0.0198 0.0196 0.0193 ...

0.0203 0.0202 0.0200 0.0199 0.0198 0.0196 0.0193 ...

0.0203 0.0201 0.0200 0.0199 0.0198 0.0196 0.0193 ...

}

}

ETCH_VS_WIDTH_AND_SPACING {

$$ 这部分表示刻蚀宽度偏差。理想情况下,刻蚀的宽度就是mask留的宽度,但实际制造中,光刻和刻蚀会受到线宽和间距影响而引起偏差

$$ 因此,实际的线宽应该是理想线宽减去两倍的刻蚀偏差,real_width=origin-2*etch_value

$$ etch_value为正值时,说明线宽变窄,shrink; etch_value为负值时,说明线宽变宽,expansion

$$ 实际线上电阻应该基于考虑etch后的真实线宽

$$ etch_value通过spacing和width查表得到

SPACINGS { 0.3600 0.5400 0.7200 0.9000 1.0800 1.3500 1.8000 2.2500 2.7000 3.1500 3.6000 4.0500 4.5000 4.9500 5.4000 }

WIDTHS { 0.3600 0.5400 0.7200 0.9000 1.0800 1.3500 1.8000 2.7000 3.6000 4.5000 5.4000 6.7500 8.1000 9.0000 10.8000 }

VALUES {

-0.023150 -0.022300 -0.021450 -0.020650 -0.019800 -0.018950 -0.018100 -0.017300 -0.016450 -0.015600 -0.014800 -0.013950 -0.013100 -0.012250 -0.011450

-0.014300 -0.013100 -0.011900 -0.010700 -0.009500 -0.008350 -0.007150 -0.006000 -0.004800 -0.003600 -0.002450 -0.001200 -0.000050 0.001150 0.002300

省略

}

}

WMIN=0.36 SMIN=0.36

$$ WMIN为min width;SMIN为min spacing

CRT_VS_SI_WIDTH {

$$ 上面说过temperature-dependent resistance,两个系数分别为CRT1和CRT2

$$ CRT1/CRT2基于width查一维表得到

(0.3900, 3.6490e-03, -8.5347e-07) (0.4572, 3.6834e-03, -8.5317e-07) 省略

}

}

总结:

芯片制造过程中的工艺偏差,会导致金属的宽度/厚度/形状发生偏差,继而导致RC的偏差。

thickness = origin - f(density,width)

width = origin - 2*f(spacing,width)

resistivity = f(width,thickness)

R= CRT2*(T-T0)^2 + CRT1*(T-T0) + R0