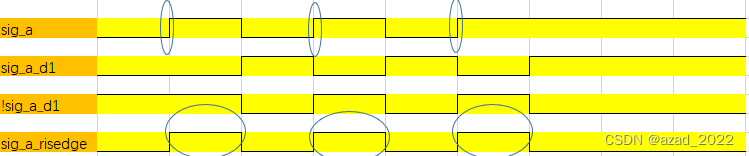

检测上升沿:(从低到高的跳变 __| )

input sig_a;

reg sig_a_d1;

wire sig_a_risedge;

alaways @(posedge clk or negedge rstb)

begin

if(!rstb)

sig_a_d1 <= 1'b0;

else

sig_a_d1 <= sig_a;

end

assign sig_a_risedge = sig_a & !sig_a_d1;

即为检测sig_a 的上升沿信号(图中圈),sig_a_risedge的圈即检测出上升沿信号,作为指示信号

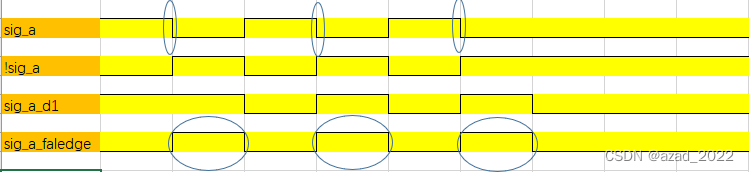

检测下降沿:(从高到低的跳变 |__ )

input sig_a;

reg sig_a_d1;

wire sig_a_faledge;

alaways @(posedge clk or negedge rstb)

begin

if(!rstb)

sig_a_d1 <= 1'b0;

else

sig_a_d1 <= sig_a;

end

assign sig_a_faledge = !sig_a & sig_a_d1;

即为检测sig_a 的下降沿信号(图中圈),sig_a_faledge的圈即检测出下降沿信号,作为指示信号