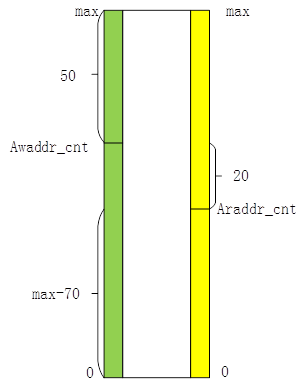

一、本章概括

在上一节中,我们概括了工程的整体思路,并提供了工程框架,给出了读写DDR4寄存器的接口列表和重点时序图。当然,对于将DDR4内存封装成FIFO接口,其中的重点在于对于读写DDR4内存地址的控制,相对于读写fifo只需要有读写数据和读写使能的接口来说,ddr4内存的读写需要控制更多的信号,其中最重要的就是地址和长度,这一章就重点讲到如何利用读写DDR4的接口来实现对DDR4的读写控制。

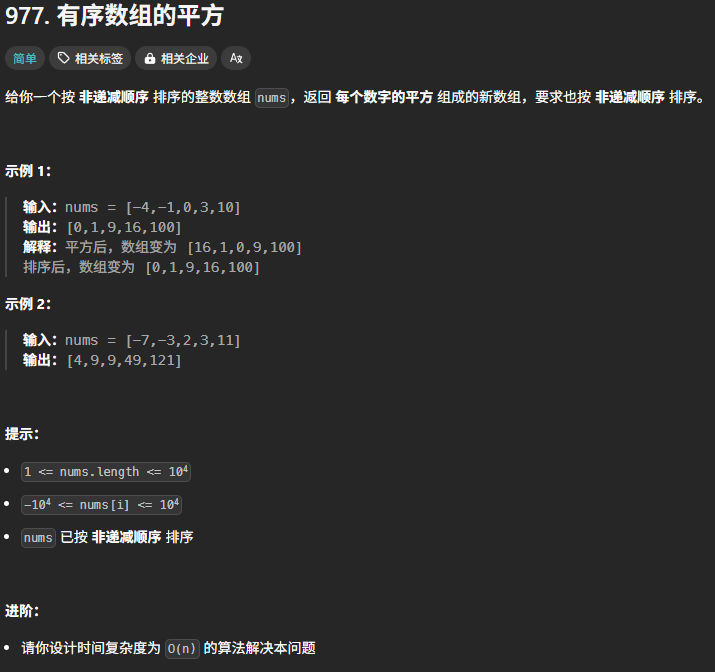

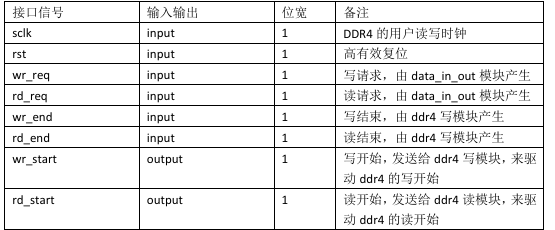

二、data_in_out模块接口列表:

三、data_in_out模块功能介绍

设计思路为:如果fifo_1不空并且ddr不满的话,就往ddr中写入fifo_1中的数据。如果fifo_2不满并且ddr不空的话,就从ddr中读出数据存到fifo_2中。

(1)、写入ddr:

Ddr的写模块和读模块在工作时会分别输出一个拉高的忙碌信号(wr_busy和rd_busy)。只要ddr不满并且fifo_1不空,并且wr_busy和rd_busy都为0时,就会拉高wr_req信号。

当开始写时,写地址就为awaddr_cnt。

增加一个ddr中有效数据的计数器addr_left。每写一个数就+1,每读一个数就-1。想要写ddr,就需要统计fifo_1中数据的数量和ddr中有多少空位。使用fifo_1的rd_data_count表示fifo_1中可以读出多少个数据,ddr的深度-addr_left表示ddr中可以存多少个数据。由于突发类型为incr类型,ddr的地址在存储数据的过程中不会自动回零,所以还要计算当前写地址距离写满地址还可以储存的数据数量。

以下为信号说明:

DDR_ADDR_MAX:32’H80000000,ddr4的地址深度。

ddr_data_max= DDR_ADDR_MAX[31:6],表示ddr中可以存储的最大数据数量。

awaddr_data_cnt:awaddr_cnt[30:6],表示当前ddr中写入的数据数量。

rd_data_count:为fifo_1中可以读出的数据数量。

addr_vac:ddr_data_max-addr_left,表示ddr中的空位可以存储的数据数量。

awaddr_sub_cnt:ddr_data_max-awaddr_data_cnt,表示距离写满地址还可以储存的数据数量。

因为写长度最大为255,所以当rd_data_count和addr_vac和awaddr_sub_cnt都大于255时,wr_len就为255,否则,就取这仨中最小的值-1。

如果ddr中有效数据数量addr_left = ddr_data_max,那么ddr_full为1,否则为0.

如果ddr中有效数据数量addr_left =0,那么ddr_empty为1,否则为0.

ddr的写数据通道的valid 和ready同时有效 = fifo_1的读使能。Fifo_1的读数据为写入ddr的数据。

(2)、读ddr:

只要ddr不空并且fifo_2不满,并且wr_busy和rd_busy都为0时,就会拉高rd_req信号。

在读ddr时,读地址为读ddr模块中的araddr_cnt。

以下为信号说明:

araddr_data_cnt:araddr_cnt[30:6]。表示当前从ddr中读取的数据数量

rd_fifo_left:511-(fifo_2的wr_data_count-2),表示fifo_2中还可以写入的数据数量。

araddr_sub_cnt:ddr_data_max-araddr_data_cnt。表示距离读满地址还可以读取的数据数量。

因为读长度最大为255,所以当addr_left和rd_fifo_left和araddr_sub_cnt都大于255时,rd_len就为255,否则,就取他仨中最小的值-1。

Ddr的读数据通道的valid和ready同时有效时为fifo_2的写使能,ddr读出的数据为fifo_2的写数据。

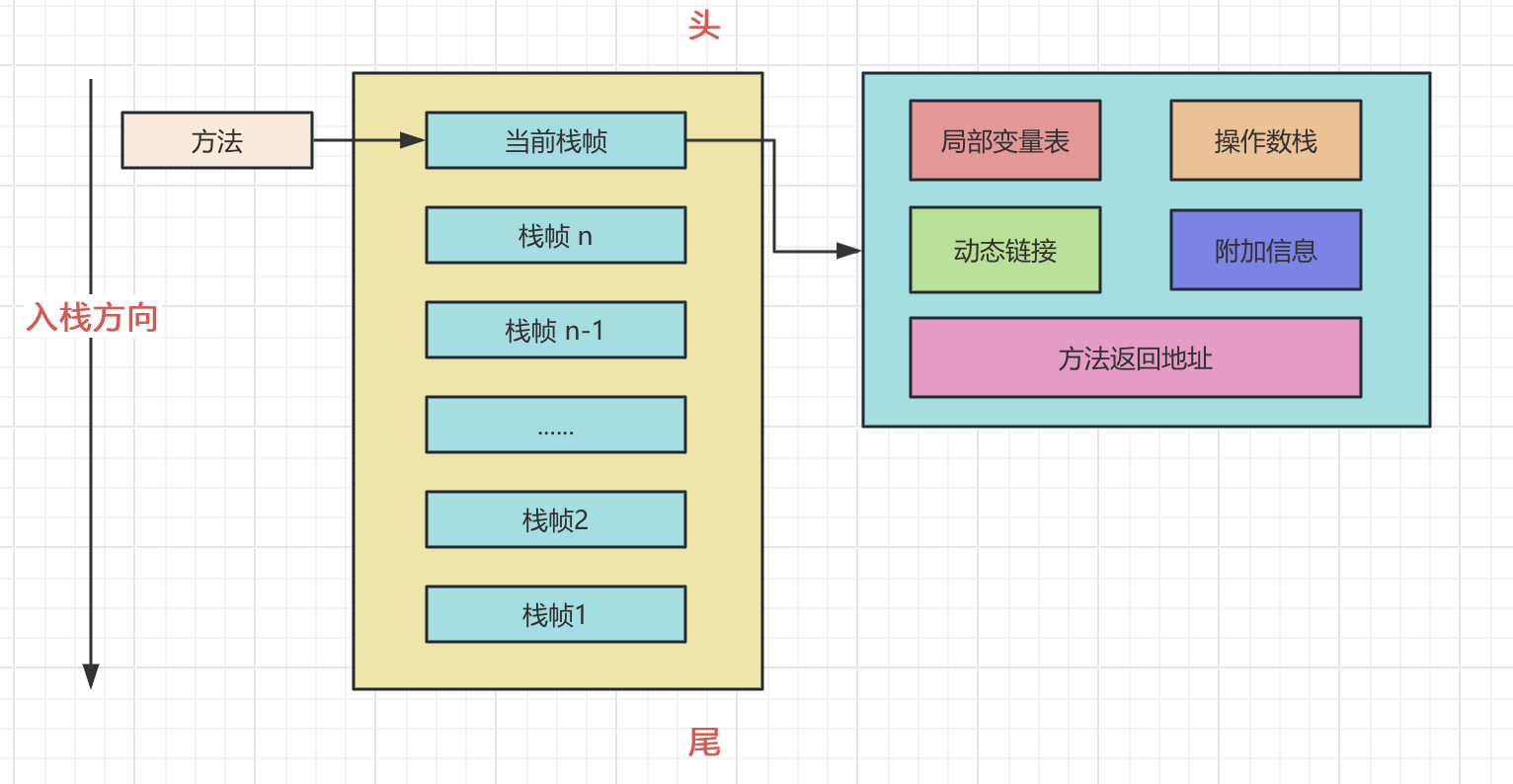

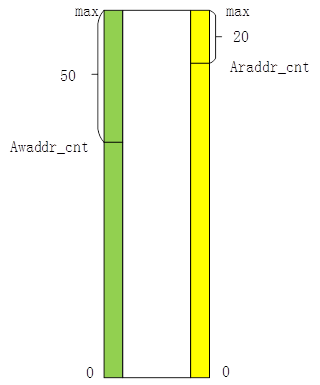

为了更好理解以上内容,我们以ddr的地址空间为例,假设fifo_1有足够的数据,fifo_2有足够的空间,不考虑fifo的情况下。选择两种情况来分析一下:

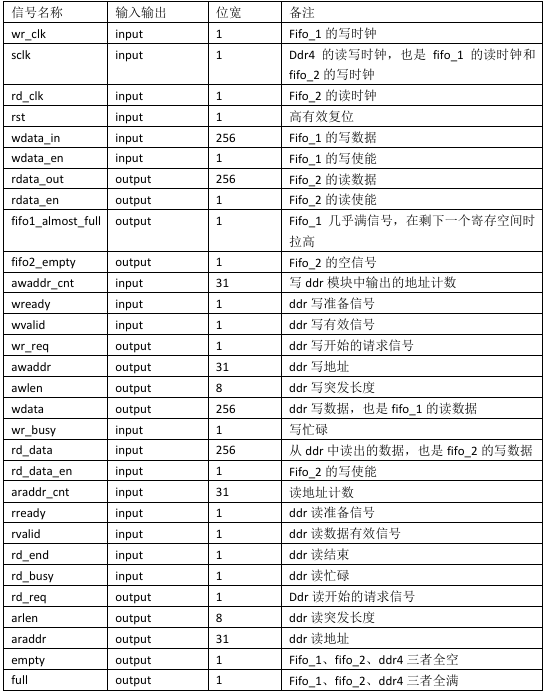

第一种:araddr_cnt<awaddr_cnt

左边绿色为写地址,右边黄色为读地址,由下往上计数,max为ddr_data_max。

写地址还差50个数据写满,ddr中还剩20个数据,读写地址都没有到最大值,这时如果想要写ddr的话,写长度aw_len为50-1。如果想要读ddr的话,读长度ar_len为20-1。

第二种:araddr_cnt>awaddr_cnt

当读地址大于写地址时,说明写地址已经在写第2圈,读地址还在读第一圈,这时如果想要写ddr的话,写长度aw_len为50-20-1。因为写完的第一圈还有20的数据没读出去,第二圈又写了max-50的数据。所以还可以写进30个数据。如果想要读ddr的话,读长度ar_len为20-1。

四、仲裁功能

通常写请求和读请求会同时拉高,所以要设计一个仲裁模块,先写后读。

仲裁模块接口列表:

仲裁模块功能说明:

由于读写控制模块通常会同时发送写请求和读请求,但DDR4只能满足其中一种请求,要么实现写功能,要么实现读工能,在这里我们做一个仲裁,当两种请求同时来的时候,我们先发送写开始,当接收到写结束信号后,再发送读开始。

五、总结

到此,我们的单通道的读写功能已经完成,下一章节增加测试模块,并上板验证。

本文章由威三学社出品

对课程感兴趣可以私信联系