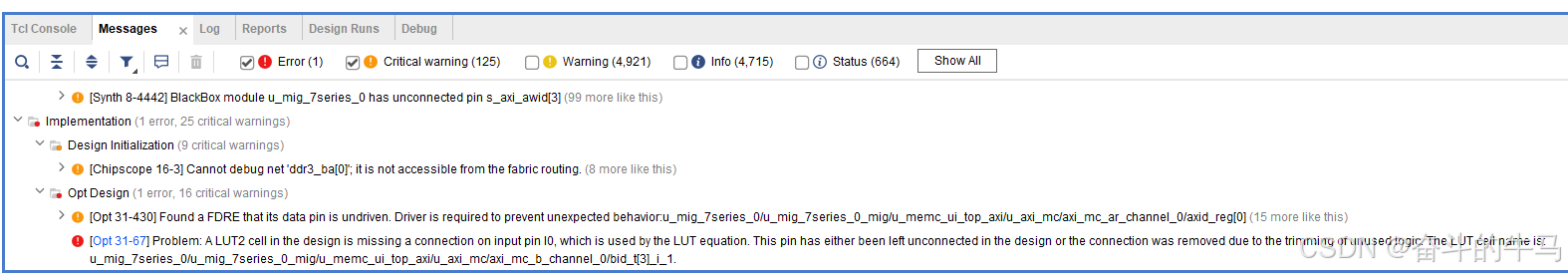

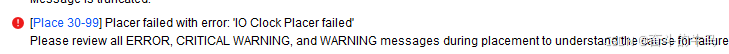

1otp 31-67

解决 端口没连接 必须赋值;

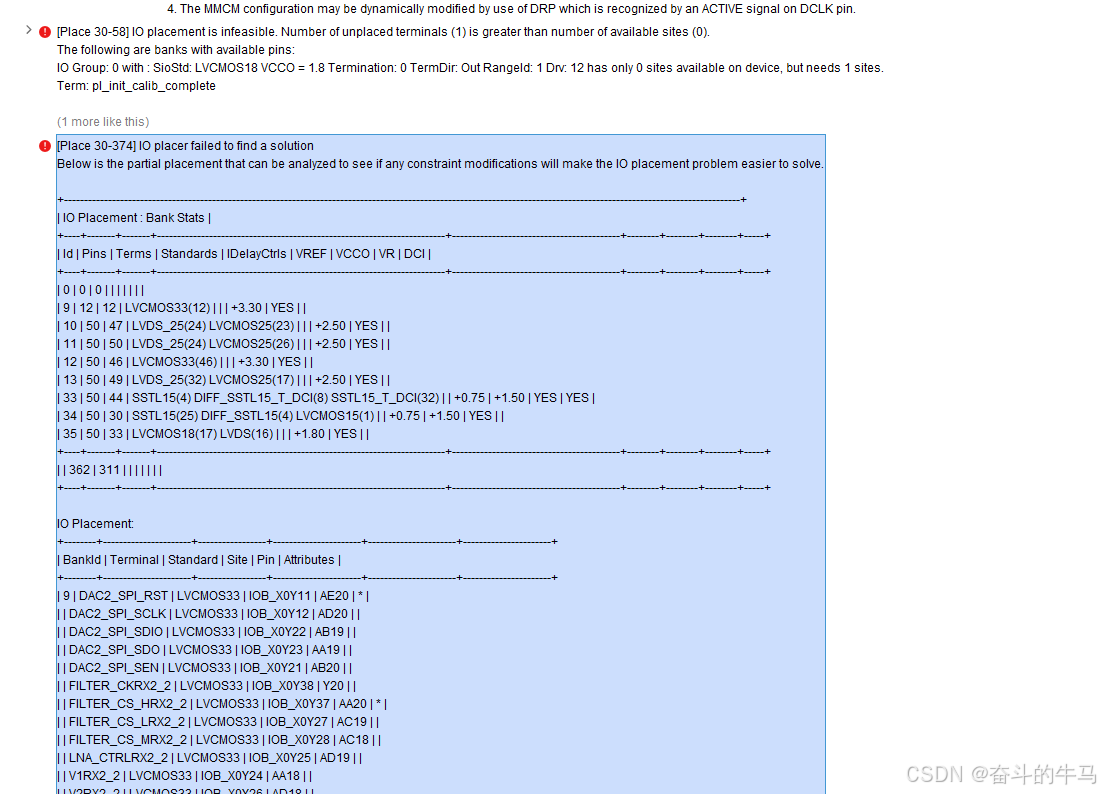

2.PLACE 30-58 TERM PLINITCALIBZ这里有问题 在顶层输出但是没有管脚约束报错

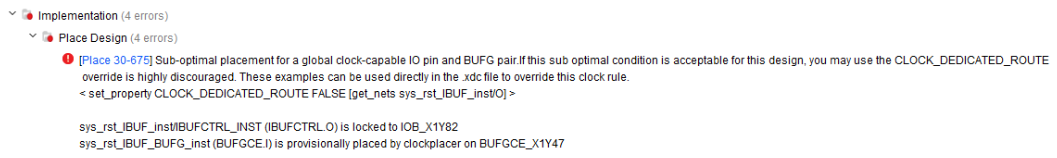

3.ERROR: [Place 30-675]

3.ERROR: [Place 30-675]

这是时钟不匹配IBUF不在同一个时钟域,时钟不在同一个时钟域里,推荐的不建议修改

问题

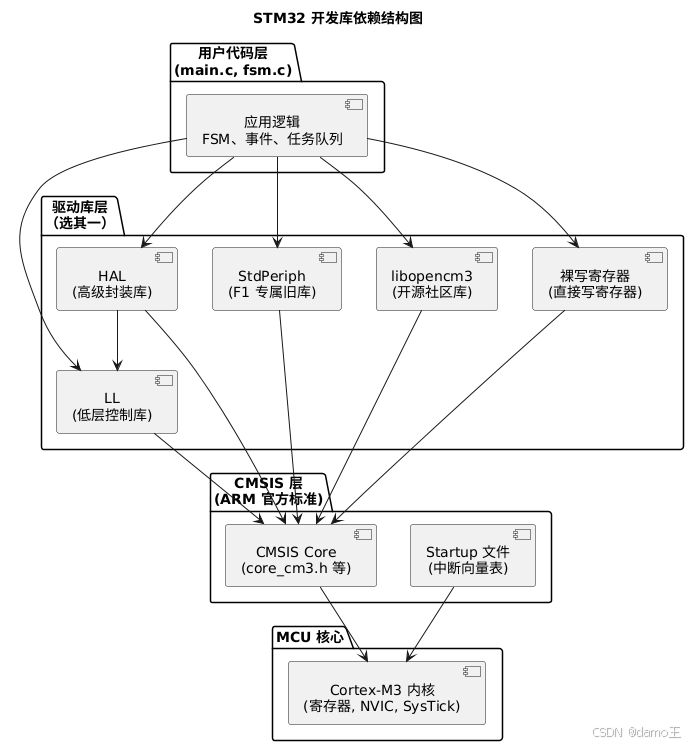

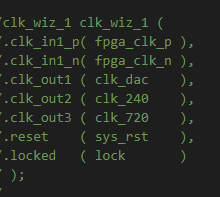

原本的时钟是从fpga端口输出给pll,pll产生的时钟给各个模块。选的是 nobuffer,会报错并且没有进ibuff bufg

解决:

生成两个pll,一个是给所有的模块所用到的时钟,一个是专门给migddr3的时钟。

端口的差分时钟进入IBUFDS,把差分转单端,并且进入一个BUFG,从BUFG出来的时钟作为pll锁相环的输入,同时在配置pll的时候选择global_buffer.

//+FHEADER ===============================================================================

// Copyright(c) Comlighten TECHNOLOGY Co.,LTD. All rights reserved.

// =======================================================================================

//

// File Name :

// Department :

// Author :

// Author's Email:

//

// =======================================================================================

// PURPOSE:

//

//

// =======================================================================================

// RELEASE HISTORY

// VERSION DATE AUTHOR DESCRIPTION

//

//

//

//

//-FHEADER ===============================================================================

`timescale 1 ps / 1 ps

module dcm_wrapper(

input fpga_clk_p,

input fpga_clk_n,

input sys_rst ,

output clk_240 ,

output clk_dac ,

output clk_720,

output reg rf_init ,

output asy_rst

);

wire clk40_s;

wire clk40_g;

wire clk600_lock;

wire lock;

assign asy_rst = (~lock)&(~clk600_lock);

//clk_wiz_1 clk_wiz_1 (

//.clk_in1_p( fpga_clk_p ),

//.clk_in1_n( fpga_clk_n ),

//.clk_out1 ( clk_dac ),

//.clk_out2 ( clk_240 ),

//.clk_out3 ( clk_720 ),

//.reset ( sys_rst ),

//.locked ( lock )

// );

//

//reg [31: 0] power_up_dly;

//

//always @( posedge clk_240 or posedge asy_rst ) begin

// if( asy_rst == 1'b1 )

// power_up_dly <= 32'd0;

// else if( power_up_dly == 32'd80000000 )

// power_up_dly <= power_up_dly;

// else

// power_up_dly <= power_up_dly + 32'd1;

//end

//

//

//

//always @( posedge clk_240 or posedge asy_rst ) begin

// if( asy_rst == 1'b1 )

// rf_init <= 1'b1;

// else if( power_up_dly == 32'd80000000 )

// rf_init <= 1'b0;

// else;

//end

IBUFDS #(

.DIFF_TERM("FALSE"), // Differential Termination

.IBUF_LOW_PWR("TRUE"), // Low power="TRUE", Highest performance="FALSE"

.IOSTANDARD("DEFAULT") // Specify the input I/O standard

) IBUFDS_inst (

.O(clk40_s), // Buffer output

.I(fpga_clk_p), // Diff_p buffer input (connect directly to top-level port)

.IB(fpga_clk_n) // Diff_n buffer input (connect directly to top-level port)

);

BUFG BUFG_inst (

.O(clk40_g), // 1-bit output: Clock output

.I(clk40_s) // 1-bit input: Clock input

);

clk_wiz_1 clk_wiz_1 (

.clk_in1 ( clk40_g ),

.clk_out1 ( clk_dac ),

.clk_out2 ( clk_240 ),

//.clk_out3 ( clk_720 ),

.reset ( sys_rst ),

.locked ( lock )

);

clk_wiz_600 instance_name

(

// Clock out ports

.clk_out1(clk_720), // output clk_out1

// Status and control signals

.reset(sys_rst), // input reset

.locked(clk600_lock), // output locked

// Clock in ports

.clk_in1(clk40_g)); //

reg [31: 0] power_up_dly;

always @( posedge clk_240 or posedge asy_rst ) begin

if( asy_rst == 1'b1 )

power_up_dly <= 32'd0;

else if( power_up_dly == 32'd80000000 )

power_up_dly <= power_up_dly;

else

power_up_dly <= power_up_dly + 32'd1;

end

always @( posedge clk_240 or posedge asy_rst ) begin

if( asy_rst == 1'b1 )

rf_init <= 1'b1;

else if( power_up_dly == 32'd80000000 )

rf_init <= 1'b0;

else;

end

endmodule

选择global