由于Verilog中X态的微妙语义,RTL仿真可能PASS,而网表仿真却会fail。

目前进行的网表仿真越来越少,这个问题尤其严重,主要是网表仿真比RTL仿真慢得多,因此对整个回归测试而言成本效益不高。

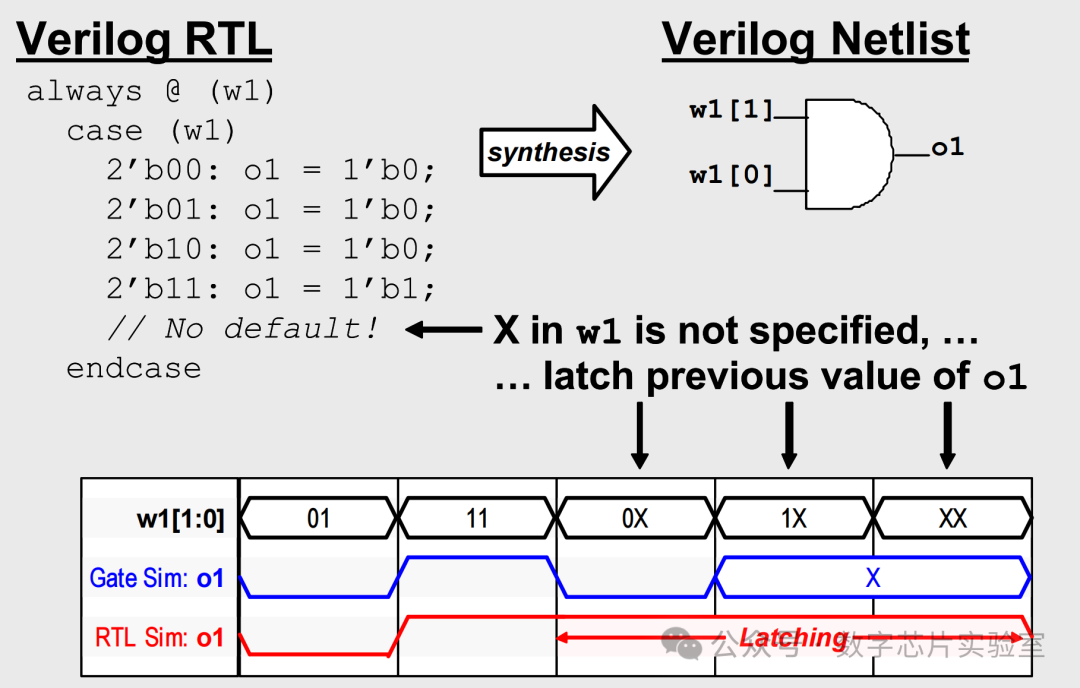

上面的例子中,用Verilog RTL中的case语句描述了一个简单的AND函数,它被综合成AND2门。然而,波形图显示RTL仿真与网表仿真存在差异。

当w1信号上出现任何X值时(可能来自显式的X赋值或未初始化的寄存器),仿真差异就会发生。w1上的X值意味着w1无法匹配任何一个case项。由于没有default行,输出o1必须保持其之前的值,这意味着在上面的波形中o1会保持高电平锁存状态。

最有趣的差异出现在w1==2'b0X时:

-

网表仿真正确地显示o1为低电平

-

RTL仿真错误地保持o1为高电平(相反的值)

无论w1上的X值如何优化,每个网表都会表现得像这样。综合工具不会警告这个“锁存行为”,但当RTL验证仅因为这种X态解释而通过某些测试用例时,RTL和网表仿真之间的差异就变得危险了。

RTL仿真中乐观的X态语义

Verilog RTL中常见的问题是if语句周围的X- optimistic。考虑下面的例子:

always @(i1 or i2)

case({i1, i2})

2'b00,2'b01: o1 =1'bX;// 无关项X赋值

2'b10: o1 =1'b0;

2'b11: o1 =1'b1;

default: o1 =1'bX;// X传播

endcase

always @(i2 or o1)

if(o1) o2 =1'b0;

else o2 = i2;在这个例子中,输出o1上的X只会选择else分支,后续暴露i2被赋值给o2时的问题。如果综合后X态无关项被最小化为1'b1——如果你运行网表仿真,可能会使先前通过的测试用例fail!

关于Verilog X态的40个面试题

![[Linux]解决虚拟机 ubantu系统下网络的问题](https://i-blog.csdnimg.cn/direct/e0df67dff77749bb804349168599f4da.png)