5 SRAM介绍及其应用要点

DRAM的性能在很大程度上受到刷新操作的影响,而SRAM则不涉及刷新,因此在相同时钟频率的条件下,SRAM的性能远高于DRAM。

SRAM的缺点是集成度低、容量小、功耗大、价格高。

在应用的场合上,SRAM毫不逊色于DRAM。CPU的高速缓存(如MPC8548,有指令一级缓存和数据一级缓存各32KB,另有二级缓存512KB)即为SRAM。相比CPU外部1GB、甚至2GB的DRAM存储器,CPU内SRAM的容量则小得多,且CPU内部SRAM容量的大小,在很大程度上决定了CPU性能的高低。

SRAM分为同步SRAM与异步SRAM两大类,同步SRAM接到读写指令后,需参考外部时钟信号的边沿才能发起操作,而异步SRAM则无需参考外部时钟,只要接到读写指令,立即开始工作。

在高速电路设计中,ZBT SRAM和QDRII SRAM是常用的SRAM,这两种SRAM都属于同步SRAM。

1. ZBT SRAM

1)ZBT SRAM概述

ZBT SRAM指零总线翻转(Zero Bus Turnaround)SRAM。对普通SRAM而言,由于读操作和写操作的驱动不同,当出现类似写—读—写这样的操作时,相邻操作之间需插入一个空闲周期以便切换驱动方。在读写操作切换频繁的应用中,这种空闲周期将严重影响存储性能。为此,ZBT SRAM得以诞生,顾名思义,对ZBT SRAM,在读写操作之间不存在空闲周期,即读写操作可无缝连接,从而提高了存储性能。

目前市场上有多家存储器厂商生产支持零总线翻转的SRAM,由于各厂商分别拥有自己的专利,因此对器件的命名并不相同,例如:

GSI公司:NBT(No Bus Turnaround,无总线翻转)。

Cypress公司:NoBL(No Bus Latency,无总线延迟)。

IDT公司:ZBT(Zero Bus Turnaround,零总线翻转)。

Samsung:NiRAM(No Turnaround RAM,无翻转)。

这些器件之间,虽名称不同,但具有相同的特性,且引脚的定义往往也是相同的,这有利于兼容性设计。

2)ZBT SRAM芯片引脚介绍

下文以GSI公司的GS8128Z36B为例,对ZBT SRAM进行介绍(GSI将零延时SRAM定义为NBT SRAM,此处统称为ZBT SRAM)。

GS8128Z36B的存储容量为144Mb,与容量为8Mb、16Mb、36Mb、72Mb的同系列器件封装兼容。

器件引脚定义如下:

A0、A1:地址信号线,为输入信号,提供地址总线的最低两位。

A:地址信号线,为输入信号。与DRAM不同的是,由于不涉及内部寄存器的配置,SRAM的地址信号线没有线序,可任意交换。

DQA、DQS、DQC、DQD:数据信号线,为输入输出双向信号。数据总线分为A、B、C、D四组,每组八位,组内无线序,可任意交换。对GS8128Z36B,有22位地址信号线(包括A0、A1),32位数据信号线,因此存储容量为2^22×32=144Mb,该器件最高存储速率为200MHz,因此峰值带宽为200MHz×32=6.4Gbps。

B、B#、B、B#:字节写使能,为输入信号,低电平有效。与四组数据总线对应,仅在写操作时用于选择待操作的字节,读操作时无效。

CK:时钟,为输入信号,除ZZ、G#和LBO#外,其他信号均通过CK的上升沿采样。

CZE#:时钟使能,为输入信号,低电平有效。

W#:写使能,为输入信号,低电平有效。

E1#、E2#、E3#:片选,为输入信号。只有当这三个信号同时有效(E1#和E3#低电平,E2高电平)时,才表示片选有效。

Q#:输出使能,为输入信号,低电平有效。

ADV:突发操作计数使能,为输入信号,高电平有效。突发操作使能时,第一个周期,ADV为低电平时,地址总线上提供起始地址,随后ADV变为高电平,则地址连续自动地加1以实现突发操作。

ZZ:睡眠模式使能,为输入信号,高电平有效。

FT#:直通模式使能,为输入信号,低电平有效。当FT#为低电平时,选择直通模式(Flow Through),否则选择流水线模式(Pipeline),这两个模式将在下文中介绍。

LBO#:线性突发操作顺序,为输入信号,低电平有效。当LBO#为低电平时,选择线性突发顺序(Linear Burst Sequence),否则选择间接突发顺序(Interleaved Burst Sequence)。

ZQ:输出阻抗控制,为输入信号。当ZQ为高电平或浮空时,选择高阻抗输出(低驱动能力),ZQ为低电平时,选择低阻抗输出(高驱动能力)。驱动能力的选择与PCB上走线长度、匹配电阻的选择有关,应根据仿真结果确定。

VDD:内核电源,可选择为2.5V或3.3V。

VDDQ:接口电源,可选择为2.5V或3.3V。

【案例5】片选处理不当导致SRAM数据丢失

基于环保设计,某产品支持省电模式,进入省电模式后,产品上所有电源全部掉电,用户数据保存在SRAM中,SRAM由一颗纽扣电池供电。测试发现,产品进入省电模式,二十多小时后重新恢复正常模式,SRAM中存储的用户数据丢失。

【讨论】

SRAM电源电路设计如下图所示。

电池使用Energizer公司的CR2032,输出电压3V,储能225毫安时。产品工作于正常模式时,SRAM由3.3V供电,进入省电模式后,3.3V电源下电,SRAM改由电池供电。利用二极管隔离3.3V电源和电池电源。

设计中SRAM的片选信号CS#上拉于3.3V,进入省电模式后,3.3V电源下电,基于其片内的弱下拉,CS#处于低电平有效状态,使SRAM一直处于片选使能,并未真正进入省电状态,此时,即便没有数据传输,SRAM仍消耗电流几十毫安,电池的能量被迅速消耗尽。

改板时,将CS#上拉于Vbattery,进入省电模式后,利用电池的供电,使CS#处于高电平无效状态,SRAM仅消耗电流几十微安,用户数据得到长期的保存。

3)ZBT SRAM工作模式之一:直通模式

直通模式(Flow Through):在读写操作时,地址信息出现在总线上的一个周期后,数据即被驱动到数据总线上。如下图所示为ZBT SRAM直通模式。

周期1:CK上升沿,片选E#有效(E1#和E3#为低电平,E2为高电平),W#为低电平,定义第一个操作为写操作,ADV为低电平,采样地址总线上的信号,获得第一个待操作的地址A,Bn#选择写操作所针对的字节。

周期2:CK上升沿,片选E#有效,W#为低电平,定义第二个操作为写操作,ADV为低电平,采样地址总线上的信号,获得第二个待操作的地址B,Bn#选择写操作所针对的字节,DQ上出现针对第一个操作的待写入数据D(A)。

周期3:CK上升沿,ADV为高电平,表明第三个操作是第二个操作的连续突发,由于第三个操作属突发操作,即指令与第二个操作相同,可无效片选E#和W#,Bn#选择本次写操作所针对的字节,DQ上出现针对第二个操作的待写入数据D(B)。

周期4:CK上升沿,片选E#有效,W#为高电平,定义第四个操作为读操作,ADV为低电平,采样地址总线上的信号,获得第四个待操作的地址C,由于第四个操作是读操作,Bn#无效,DQ上出现针对第三个操作的符号D(B+1)。

周期5:CK上升沿,ADV为高电平,表明第五个操作是第四个操作的连续突发,由于第五个操作属突发操作,即指令与上一个操作相同,可无效片选E#,同时对于读操作,W#和Bn#无效,DQ上出现针对第四个操作的特读出数据Q(C)。

周期6:CK上升沿,片选E#有效,W#为高电平,定义第六个操作为读操作,ADV为低电平,采样地址总线上的信号,获得第六个待操作的地址D,由于第六个操作是读操作,Bn#无效。DQ处于高阻,原因在,在周期6,输出使能信号G#变为无效。

周期7—周期10,分析方法同上,此处不再赘述。

根据直通模式流程图,归纳出以下几点:

要点一,对于ZBT SRAM,读、写操作之间不存在空闲周期,如周期4,数据总线DQ上出现的是待写入的数据D(B+1),周期5,DQ上的数据为待读取的数据Q(C)。而普通的SRAM,在读、写操作之间必须加上空闲周期,以便实现总线控制权的转交,基于这一点,对于读写操作频繁的应用,应用ZBT SRAM无疑能获得更高的性能。

要点二,对于直通模式,数据将在地址、命令发出的一个周期后出现在数据总线上,对于突发操作,其操作节拍为2-1-1-1,即在地址(以A0为例)、命令发出后的第二个周期,A0地址的数据出现在总线上,随后连续地发出A1,A2,…,地址的数据。(操作节拍可

是按照PowerPC或Pentium CPU对高速缓存的操作方法定义的,对于这两类CPU,每次需从高速缓存连续读取4个字的数据,即一次读取的突发长度为4,因此,节拍数为4。)

4)ZBT SRAM工作模式之二:流水线模式

流水线模式(Pipeline):在读写操作时,地址信息出现在总线上的两个周期后,数据才能被驱动到数据总线上。相比直通模式,数据需延迟一个周期以便存入内部寄存器。对于突发操作,其操作节拍为3-1-1-1,即在地址(以A0为例)、命令发出后的第三个周期,A0地址的数据出现在总线上,随后连续地发出A1,A2,…,地址的数据。

流水线模式最初是为提高CPU的执行效率而提出的。CPU的工作分为取指、译码、运算等步骤,各步骤分别由不同的功能模块完成,如按顺序方式执行,则先由取指模块负责取指,此时译码和运算模块空闲,随后译码模块开始工作,而取指模块和运算模块空闲,依次类推。这种顺序执行的方式,与直通模式(Flow Through)相似,对输入的数据无需寄存,但不利于器件内部资源利用率的提高。

CPU的流水线模式如下图所示。

采用流水线模式后,三个功能模块可并行工作,从而提高了资源的利用率,进而使存储性能也得到提升。根据上图,为实现多个功能模块对数据的并行处理,必须在输入/输出接口部分将数据进行缓存,而缓存本身需占用一个时钟周期,此即为传输第一个数据时,流水线模式比直通模式多占用一个时钟周期的原因。

与CPU原理相同,ZBT SRAM的流水线模式(见下图)同样能实现芯片内多个功能模块的并行操作,以提高存储效率。

5)直通模式和流水线模式的比较

通过对器件引脚的配置,可将ZBT SRAM的工作模式配置为直通模式或流水线模式。以GS8128Z36B为例,FT#引脚为低电平时,选择直通模式,否则选择流水线模式。

对存储器件的性能,可根据其支持的最高运行速率分为若干等级,GS8128Z36B有三种速率等级:-250、-200、-167,分别对应器件的最高运行速率为250MHz、200MHz、167MHz。在相同速率等级(此处以-250速率等级为例)的情况下,基于硬件性能,流水线模式和直通模式有以下几点区别:

区别一,时钟周期的差别。流水线模式的最小时钟周期为4ns(最高时钟速率为250MHz),而直通模式最小时钟周期为6.5ns(最高时钟速率为153MHz)。该参数在第5章被定义为Tco,是时序计算中重要的参数。流水线模式的Tco最大值为2.5ns,而直通模式Tco为6.5ns。

区别二,时序参数。流水线模式下,信号的建立时间Tsu要求大于1.2ns,而保持时间Th要求大于0.2ns,而直通模式下,这两个参数分别为1.5ns和0.5ns。可以看出,直通模式对时序参数的要求更严,其原因有二:一方面在相同速率等级下,直通模式的时钟周期更长,另一方面,在直通模式下,数据采样一旦出错,将导致该周期进行的操作完全失效,而不像流水线模式下,只引发该数据的错误,而不影响流水线中正在处理的其他数据。

区别四,功耗。在流水线模式下,芯片的时钟速率和内部功能模块利用率都更高,因此功耗更大。在-250速率等级下,流水线模式的工作电流为550mA,而直通模式的工作电流为405mA。

综合而言,由于直通模式比流水线模式节省一个时钟周期,因此,在时钟速率低于100MHz的场合,直通模式的存储效率更高;由于内置了寄存器,流水线模式比直通模式更易于达到较高的速率,因此,在时钟速率高于100MHz的场合,流水线模式的存储效率更高。高速电路设计中,一般要求ZBT SRAM的时钟速率达到166MHz以上,因此,流水线模式更适于高速应用。

理解要点:

① ZBT SRAM只有在读写操作较均衡的应用中才能体现出其高效性。

② 直通模式和流水线模式的区别在于:支持的最高速率、Tco延时参数、时序参数、功耗等。

③ 在时钟速率高于100MHz的应用中,推荐采用流水线模式。

2. QDR II/DDR II SRAM

SRAM主要应用于高速缓存,是决定整个系统性能的关键部分。

基于高速缓存的均衡式读写特性(即出现读操作和写操作的概率近似相等),支持读写操作零延时切换的ZBT SRAM应运而生。不过,ZBT SRAM的运行频率无法超过200MHz,随着系统的不断升级,ZBT SRAM已无法满足某些更高性能系统的要求,由此又诞生了QDR/DDR SRAM,随后,芯片厂商对QDR/DDR SRAM做了技术更新,这种新一代的SRAM称为QDR II/DDR II SRAM,其中DDR II SRAM又分为CIO(Common IO)和SIO(Separated IO)两大类。

目前生产QDR II/DDR II SRAM的厂家有Cypress、Samsung、IDT等。

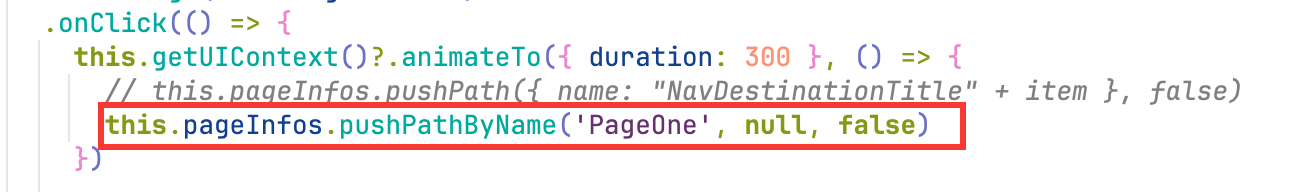

以下是提取的文字:

1)HSTL电平

由于QDRII和DDRII SRAM接口电平为HSTL电平,首先需要对这种电平进行介绍。HSTL(High Speed Transceiver Logic,高速收发逻辑)是由JEDEC定义的一种用于存储接口的电平,相对于SSTL电平(SSTL-2使用2.5V的接口电平,SSTL-18使用1.8V的接口电平),HSTL的摆幅更低,为1.5V,更适于高速的应用。

HSTL并不要求芯片内核电源VDD和芯片接口电源VDDQ的电压相同。

HSTL支持单端电平(与SSTL电平类似,由信号和VREF构成差分对,实质上仍属于差分对电平)和差分对电平,HSTL差分对电平主要应用在某些高速芯片之间的互连,而QDR II/DDR II SRAM一般采用单端电平,因此,本小节主要就单端电平展开讨论。

JEDEC对HSTL输入端各电平的要求如下,一般,各厂家的器件均应符合以下要求:

VDD:无要求;

VDDQ(min)=1.4V VDDQ(Typ)=1.5V VDDQ(max)=1.6V

VREF(min)=0.68V VREF(Typ)=0.75V VREF(max)=0.9V

VIH(DC)(min)=VREF+0.1 VIH(DC)(max)=VDDQ+0.3

VIL(DC)(min)=-0.3 VIL(DC)(max)=VREF-0.3

VIH(AC)(min)=VREF+0.2 VIH(AC)(max)=VREF-0.2

各项参数的定义与SSTL-2相同,此处不再赘述。

对输入信号,要求在信号摆幅的20%80%区间内,变化沿速率不小于1V/ns。

对输出端,JEDEC定义了四种驱动模式:Class IIV,其区别仅在于输出电流的不同:

Class I:Ion≥8mA,IOL≥-8mA;

Class II:Ion≥16mA,IOL≥-16mA;

Class III:Ion≥8mA,IOL≥-24mA;

Class IV:Ion≥8mA,IOL≥-48mA。

Cypress等公司的QDRII/DDRII SRAM采用的驱动模式是Class I。

对HSTL Class I,匹配方式如下图所示。

与SSTL-2匹配方法类似,RTT应布放于信号走线的末端,且靠近接收端。VRT电平为VDDQ的一半。

由于DDR II CIO SRAM、DDRII SIO SRAM与QDR II SRAM类似,首先重点介绍QDR II SRAM。

2)QDR II SRAM

QDR是指四倍数据速率(Quad Data Rate),DDR SDRAM的双倍数据速率是通过双边沿对数据采样而实现的。QDR的数据采样同样基于双边沿,且进一步将数据的读端口和写端口分开,利用同一组地址和控制信号实现对这两个端口的访问,输入和输出同时进行,从而在实现四倍数据速率的同时,消除了读、写操作之间的空闲周期,提高了存储效率。

QDR II相对QDR I的技术更新有以下两点:

一方面,QDR II内部增加了DLL。DLL的正面作用在于,其减小了Tco时间(输出数据Q相对时钟C/C#的延时),将Tco从QDR I的0.5ns减小为QDR II的0.5ns,从而增大了数据有效窗口,有利于存储器件最高工作时钟频率的提高。DLL的负面作用在于,其产生了额外的时钟周期的延迟,对QDR I,在地址和命令对应的C/C#(在单时钟模式下,为K/K#)时钟边沿一个时钟周期后,输出数据出现在数据总线Q上,而对QDR II,则需要一个半时钟周期。

另一方面,同样基于DLL,QDR II能输出一个与输出数据Q同相的时钟CQ/CQ#,以便于接收端的精确采样。

以Cypress公司的CY7C1411BV18为例,对QDRII SRAM进行详细介绍。

CY7C1411BV18的存储容量为32Mb(4M×8bit),最高运行时钟频率为300MHz,由于采用了时钟的双边沿对数据进行采样,单根数据信号线的最高数据传输速率可达600Mbps。

QDR II SRAM的关键引脚定义如下:

K/K#:差分对时钟,为输入信号。

C/C#:差分对时钟,为输入信号。

D7:0:输入数据。在写操作时,存储器利用外部输入的时钟K/K#实现对D7:0的采样。

Q7:0:输出数据。在读操作时,存储器基于外部输入的时钟C/C#(在单时钟模式,则外部仅提供K/K#时钟的情况下,采用K/K#)驱动数据输出到Q7:0上。

CQ/CQ#:回应时钟(Echo Clock),为输出信号。

A:地址总线,为输入信号。在输入时钟K/K#下,对A进行采样,QDR II SRAM对地址总线的线序没有要求,设计中可根据PCB设计的要求而任意交换顺序。

CY7C1411BV18的地址总线宽度为20,可组合的地址数目为2^20=1M。CY7C1411BV18的读写操作以长度为4字节的突发传输为一个单位,因此一个地址对应4字节数据,从而实现了以1M的地址数目,对片内4M地址空间的寻址。此处需要注意,不同芯片的突发长度不一定相同,例如,Samsung公司K7R32098ZC的突发长度为2,而不是4。

WPS#:写使能,为输入信号。

RPS#:读使能,为输入信号。

ZQ:输出阻抗配置,为输入信号。QDR II SRAM通过该引脚实现对输出阻抗的调节,在ZQ引脚与GND之间连接电阻RZQ,则CQ/CQ#、Q7:0的输出阻抗将被配置为0.2×RZQ,例如,为配置CQ/CQ#、Q7:0引脚的输出阻抗为50Ω,应选择RZQ电阻的阻值为250Ω(选择常用的阻值249Ω即可)。

DOFF#:DLL关闭,为输入信号。当DOFF#信号接地时,内部DLL被关闭,工作为QDR I的模式,在QDR I的模式下,数据有效窗口减小,最高工作时钟频率只能达到167MHz(C工作于QDR II模式时,CY7C1411BV18的最高工作时钟频率可达300MHz)。

VREF:参考电平。电平值为VDDQ的一半,即0.75V,与DDR SDRAM的VREF产生方法相同。

VDD:内核电源。对CY7C1411BV18,内核电源的电压要求为1.8V。

VDDQ:接口电源。根据HSTL电平标准,接口电源的电压应为1.5V。

由于CY7C1411BV18在输入、输出方向上会有八位数据总线,且采用双边沿采样,因此其峰值带宽计算为:300MHz×8×2×2=9.6Gbps。

CY7C1411BV18的基本结构图如下图所示。

对QDRII SRAM的地址、数据采样归纳如下:

地址A的采样:利用K的上升沿。

输入数据D的采样:利用K/K#的边沿交叉点。

输出数据Q的参考:基于C/C#的边沿交叉点,在单时钟模式,即外部不提供C/C#输入时钟的情况下(此时C/C#被上拉到VDDQ),输出数据Q将参考K/K#的边沿交叉点。

回应时钟CQ/CQ#的使用:在读数据的操作时,QDR II SRAM基于内部的延迟锁相环DLL,输出一对相位与Q完全相同的差分对时钟信号CQ/CQ#,以构成源同步时钟,简化接收端对数据Q的采样。

根据突发长度的不同,QDR II SRAM可分为两类,一类的突发长度为2,一类为4。例如,Cypress公司的CY7C1411BV18的突发长度是4,而Samsung公司的K7R32098ZC的突发长度是2。对这两类SRAM,操作方式略有不同,以下仅以突发长度为4的QDR II SRAM进行介绍,如图7.52所示。

在读操作时,时钟K的上升沿采样到有效的RPS#信号,这标志着读操作的开始,地址总线上提供地址信息,在下一个K上升沿之后的第一个C#上升沿(在单时钟模式下,采用K#的上升沿)将触发输出第一个数据(从采样到读命令开始,至第一个有效数据的发出,需1.5个时钟周期),随后,由C的上升沿触发输出第二个数据,直到四个数据发送完成,即一次读操作需占用两个时钟周期。由下图可知,读操作时,CQ/CQ#与K相同。

在写操作时,时钟K的上升沿采样到有效的WPS#信号,这标志着写操作的开始,地址总线上提供地址信息,SRAM利用下一个时钟K的上升沿采样第一个数据(从采样到写命令开始,至第一个有效数据的采样,需1个时钟周期),随后,利用K#的上升沿采样第二个数据,直到四个数据采样完成。同样,一次写操作需占用两个时钟周期。

图中有几个延时参数需进行说明。

tKHCH:K/K#边沿与C/C#边沿之间的相位差,在某些设计中,这两项对信号通过不同的时钟源驱动,此时,需注意设计以满足该参数的要求。

tCO:输出数据Q相对时钟C/C#的延时。

tCQQ:CQ/CQ#与Q之间的相位差,该参数很小,但在使用回应时钟对Q采样的设计中,该参数必须被考虑到时序分析中。

3)DDR II CIO SRAM、DDR II SIO SRAM

DDR II CIO(共用输入/输出端口)与QDR II类似,不同点仅在于DDR II CIO的读端口和写端口引脚是复用的,数据传输率为QDR II的一半。

DDR II SIO(独立输入/输出端口)与QDR II都具有某些共同点。与QDR II类似,其读端口和写端口是分离的,与DDR II CIO类似,每一次只能处理一个读或写操作。因此DDR II SIO的数据传输率仍然只有QDR II的一半。DDR II SIO相对DDR II CIO的优势在于,前者的读、写端口分离,读写操作之间可以无缝切换(与ZBT SRAM类似),而后者的读、写操作之间必须插入一个空闲周期。

选型时需注意,虽然在性能上QDR II SRAM、DDR II SIO SRAM显得更有优异,但在很少发生读、写操作切换的场合下,它们的性能与DDR II CIO SRAM类似。例如,查找表的应用,以读操作为主,仅在更新表的时候才涉及写操作,在这种场合,选择QDR II SRAM或DDR II SIO SRAM则无法体现它们的优势,又如,以太网交换芯片的数据包缓冲,读、写操作基本平衡,在这种场合,宜选择QDR II SRAM。

3. QDR II SRAM时序设计

QDR II SRAM有三对差分时钟信号对K/K#、C/C#、CQ/CQ#,写操作时,SRAM一侧的采样都是通过K/K#实现的,而在读操作时,存储器控制器对数据的采样,则有以下几种方法:

方法一,使用存储器控制器的主时钟,SRAM的输入时钟有K/K#。

方法二,使用存储器控制器的主时钟,SRAM的输入时钟有K/K#、C/C#。

方法三,使用存储器控制器发出的、经绕线后回到存储器控制器的K/K#信号,SRAM的输入时钟有K/K#、C/C#。

方法四,使用SRAM发出的CQ/CQ#信号。

1)使用存储器控制器的主时钟,SRAM的输入时钟为K/K#

如下图所示为QDR II SRAM时钟模式1。

假定主时钟频率为133MHz(时钟周期7.5ns),存储器控制器的内部延迟为2ns,在PCB上,存储器控制器到SRAM1和SRAM2的走线延时都是0.5ns,SRAM的Tco时间为0.5ns,则时序设计如下图所示。

上图中,①为存储器控制器内部延时0.5ns加上存储器控制器到SRAM的走线延时0.5ns,共2.5ns,即2.5ns延时后,K上升沿到达SRAM输入端,等待1.5个时钟周期(见②),即11.25ns后SRAM准备输出数据,等待Tco=0.5ns(见③)后,输出数据Q0出现在总线上,经走线延时0.5ns后,到达存储器控制器输入端。因此,从第一个主时钟上升沿输出到数据Q0回到存储器控制器,延时共14.75ns,在存储器控制器端,利用主时钟对Q0采样,建立时间Tsu=0.25ns。

2)使用存储器控制器的主时钟,SRAM的输入时钟为K/K#和C/C#

如下图所示为QDR II SRAM时钟模式2。

假定主时钟频率为166MHz(时钟周期6ns),存储器控制器的内部延迟为2ns,在PCB上,对数据Q而言,存储器控制器到SRAM1以及SRAM1到SRAM2的走线延时都是0.5ns,SRAM的Tco时间为0.5ns,且满足以下两点以便实现SRAM1和SRAM2的输出数据同时到达存储器控制器:

第一点,L3=L1+L2;

第二点,在PCB上,C/C#走线成菊花链状,先到达距离存储器控制器最远的SRAM2,然后再连接到距离存储器控制器最近的SRAM1。

时序设计如下图所示。

在主时钟第一个上升沿2.5ns后,C到达SRAM2的输入端,再过0.5ns后,C到达SRAM1的输入端(C/C#的走线先到SRAM2,再到SRAM1),各自延迟1.5个时钟周期加上Tco,即9.5ns后,Q2和Q1出现在数据总线上,并分别经过PCB上的走线延时1ns和0.5ns后,到达存储器控制器的输入端。因此,从第一个主时钟上升沿到数据Q1和Q2到相对时钟模式1,时钟模式2通过对C/C#走线长度的调整,使所有读取到的数据同时到达存储器控制器的输入端,有利于获得最佳的时序裕量。

3)使用绕线后回到存储器控制器的K/K#信号

如下图所示为QDR II SRAM时钟模式3。

对于模式3,将K/K#送往SRAM的同时,通过在PCB上绕线回到存储器控制器的Kr/Kr#引脚。假定主时钟频率为250MHz(时钟周期4ns),存储器控制器的内部延迟为2ns,在PCB上,对数据Q而言,存储器控制器到SRAM1以及SRAM1到SRAM2的走线延时都是0.5ns,SRAM的Tco时间为0.45ns。在PCB上,K/K#到Kr/Kr#的走线延迟时间为8.95ns。

相对前两种模式,模式3的优势在于通过调整K/K#到Kr/Kr#的走线延迟,可将Kr/Kr#的上升沿与到达存储器控制器的数据Q的中央对齐,以实现最佳的时序裕量。

如下图所示,在主时钟第一个上升沿2.5ns后,C到达SRAM2的输入端,再过0.5ns后,C到达SRAM1的输入端(C/C#的走线先到SRAM2,再到SRAM1),各自延迟1.5个时钟周期加上Tco,即6.45ns后,Q02和Q01出现在数据总线上,并分别经过PCB上的走线延时1ns和0.5ns后,到达存储器控制器的输入端。从第一个主时钟上升沿的发出到数据Q01和Q02回到存储器控制器的输入端,延时共9.95ns。在存储器控制器端,利用Kr/Kr#对Q01和Q02采样,建立时Tsu=1ns。

4)使用SRAM发出的CQ/CQ#信号

如下图所示为QDR II SRAM时钟模式4。

对于模式4,在存储器控制器一侧,利用SRAM发来的CQ/CQ#实现对数据Q的采样,由于CQ/CQ#与Q相同,在PCB上,应通过绕线将CQ/CQ#延迟四分之一个时钟周期(当工作于250MHz时,为1ns),使采样边沿与Q的中央对齐。设计时需注意,某些存储器控制器支持对接收的CQ/CQ#自动延时四分之一个时钟周期,在这种情况下,应利用该特性,避免通过PCB上的绕线实现延时。

假定主时钟频率为250MHz(时钟周期4ns),存储器控制器的内部延迟为2ns,在PCB上,对数据Q而言,存储器控制器到SRAM1以及SRAM1到SRAM2的走线延时都是0.5ns,SRAM的Tco时间为0.45ns。

如下图所示,在主时钟第一个上升沿2.5ns后,K到达SRAM1的输入端,延迟1.5个时钟周期加上Tco,即6.45ns后,Q01出现在数据总线上,并经过PCB上的走线延时0.5ns后,到达存储器控制器的输入端。因此从第一个主时钟上升沿的发出到数据Q01回到存储器控制器的输入端,延时共9.45ns。在SRAM1发送端,CQ/CQ#和Q01相同,在PCB上,通过绕线使CQ/CQ#相对Q01延时1ns,在存储器控制器的输入端,利用CQ/CQ#对Q01采样,由于CQ/CQ#的边沿位于Q01的中央,因此时序裕量最佳,建立时间Tsu=1ns。

作为归纳总结,简要地对比以上四种时钟模式:

模式1,随着工作时钟频率的提高,时序裕量将不断减小,因此,模式1仅适用于时钟频率低于167MHz的场合。

模式2、3,需通过在PCB上的绕线,补偿时钟信号的延时,由于这种延时的精度差,只适用于时钟频率低于200MHz的场合。

模式4,在存储器控制器的输入端利用CQ/CQ#对数据采样,实现了源同步的时序设计,根据第5章的知识,这种设计与时钟频率完全无关,适用于任何场合。

理解要点:

① QDR II SRAM和DDR II SRAM采用的电平方式是HSTL。

② DDR II CIO SRAM、DDR II SIO SRAM、QDR II SRAM在应用存储效率上的区别。

③ QDR II SRAM的四种时钟模式及其在应用上的区别。