【硬件设计细节】缓冲驱动器使用注意事项

一、缓冲驱动器核心功能与选型原则

信号增强与隔离

驱动能力匹配 :根据负载电流需求选择缓冲器,例如CMOS缓冲器驱动能力通常为4-8mA,需搭配大电流负载时选用图腾柱输出或专用驱动芯片(如TI的SN74LVC系列)。电压域转换 :跨电压域传输时需使用电平转换缓冲器(如TXB0108),避免电平不匹配导致逻辑错误或器件损坏。阻抗匹配与信号完整性

高速信号(>100MHz) :选用低传播延迟(如SN74LVC1G17延迟<3ns)且输入电容≤5pF的缓冲器,并匹配传输线阻抗(如50Ω或75Ω)。终端电阻 :在长走线末端并联端接电阻(如22Ω),抑制信号反射。二、电路设计关键点

电源与噪声管理

去耦电容 :每个缓冲器电源引脚就近放置0.1μF陶瓷电容,高频场景(如DDR接口)增加10μF钽电容。地弹抑制 :多通道缓冲器需采用分离地平面设计,避免共地路径引起噪声耦合。保护电路设计

ESD防护 :接口类缓冲器(如USB缓冲器)需串联TVS二极管(如SMAJ5.0A),钳位电压≤5.5V。浪涌抑制 :在电源入口处添加RC缓冲电路(如R=10Ω,C=100nF),吸收开关机瞬态能量。三、布局与布线规范

物理布局优化

走线长度 :关键信号(如时钟)走线长度差控制在±5mm以内,减少时序偏差。交叉干扰规避 :高速信号线与模拟信号线间距≥3倍线宽,必要时添加地屏蔽层。散热设计

功率密度计算 :根据缓冲器功耗(如SN74LVC8T245功耗≤50mW)设计散热铜箔面积,温升控制在40℃以内。四、特殊场景处理

三态总线应用

总线冲突预防 :使用使能信号(OE)控制缓冲器输出,确保同一时刻仅一个设备驱动总线。上/下拉电阻 :总线空闲时通过10kΩ电阻拉高/低,避免悬空导致逻辑不定态。隔离型缓冲器

光耦隔离 :在工业控制中选用高速光耦(如HCPL-072L,延迟<40ns),隔离电压≥5kV。磁隔离 :对高频信号(如CAN总线)采用ADuM系列磁隔离缓冲器,带宽≥100MHz。五、测试与验证

信号质量测试

眼图测试 :对USB/HDMI接口缓冲器进行眼图分析,确保抖动(Jitter)<0.1UI。时序余量 :通过示波器测量建立时间(Setup Time)和保持时间(Hold Time),预留20%余量。环境适应性验证

温度循环测试 :在-40℃~85℃范围内验证缓冲器功能,确保输出电平偏差<5%。湿度测试 :85℃/85%RH环境下运行500小时,检查引脚氧化与绝缘性能。六、典型问题与解决方案

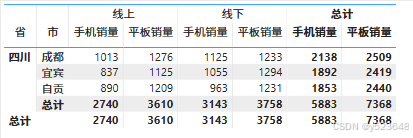

问题现象 可能原因 解决方案 信号上升沿过冲 阻抗失配或走线过长 缩短走线长度,添加终端电阻(如22Ω)7 多路输出时序不一致 缓冲器内部通道延迟差异 选用通道间延迟差<100ps的器件(如SN74LVC244A)7 电源噪声耦合 去耦电容不足 增加0.1μF+10μF组合电容,电源层分割为数字/模拟独立区域7 高温下输出电平漂移 器件温漂特性差 选用工业级缓冲器(如SN74LVC系列,温漂≤0.1%/℃)3

七、设计流程建议

需求分析 :明确信号类型(单端/差分)、速率、负载特性及环境条件。器件选型 :根据驱动能力、延迟、功耗筛选型号,优先选择JEDEC认证产品。仿真验证 :使用SPICE或HyperLynx进行信号完整性仿真,优化参数。原型测试 :重点验证极限工况(如满载、高温)下的稳定性。量产管控 :制定来料检验标准(如批次抽样耐压测试),避免假货混入。

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2299781.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!