SRAM型FPGA在宇航领域有广泛的应用,为解决FPGA在空间环境中的单粒子翻转问题,增强设计的可靠性,本文介绍一种低成本的抗辐照解决方案。该方案从外置高可靠存储器中读取配置数据,通过定时刷新结合三模冗余的方式消除单粒子影响,提高系统的鲁棒性。

1.总体设计

SRAM型FPGA的刷新方式主要有两种:一种是通过反熔丝FPGA进行回读刷新控制;另一

种是通过专用的ASIC芯片进行回读刷新控制,但其支持的外围存储器件较为有限。基于通用性设计及灵活性考虑,本文采用方式一进行抗SEU设计,该方案可以兼容多种XILINX VIRTEX系列FPGA,可通过跳线进行FPGA选型配置。

本文所提出的抗SEU方案结构如下图所示。其中XC5VFX130T芯片主要实现高速数字信号处理,AX500反熔丝芯片主要完成对V5 FPGA的配置、监控及刷新功能,Nor Flash用于存放配置程序。

系统工作时,反熔丝FPGA首先会读取三片Nor FLASH中存储的配置文件,采用表决通过的数据作为正确配置信息对XILINX V5系列FPGA进行加载,然后通过SelectMap接口实现对Virtex5 FPGA的定时刷新。

2.软件设计

对XILINX V5系列FPGA的刷新控制主要由AX500反熔丝FPGA完成,本文设计的FPGA刷

新模块的工作流程如下图所示,主要分为以下3部分。

(1)FPGA初始化。Xilinx FPGA上电稳定期间,设计将PROG_B信号拉低3ms对被加载的FPGA配置进行初始化复位,在复位过程中INIT_B信号将保持低电平。等待TPOR时间后若INIT_B拉高则表示FPGA配置区内存已清除,可以执行下一步流程;若INIT_B一直为低,则不断检测该信号,直至拉高为止。

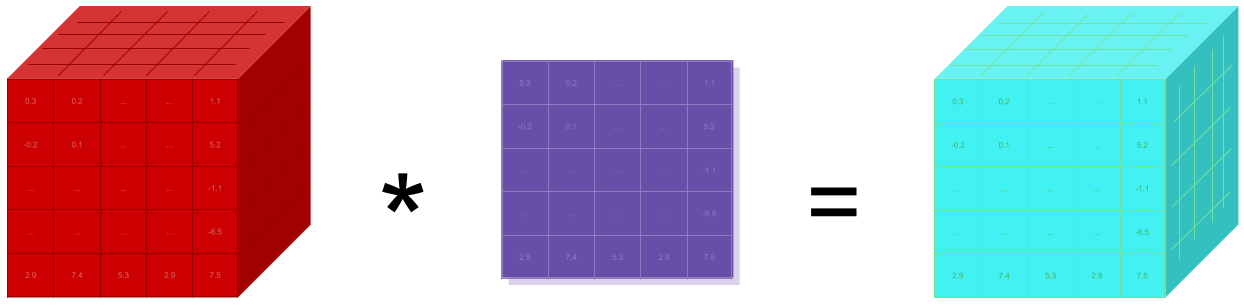

(2)配置FPGA。初始化结束后,开始配置FPGA,设置FPGA管脚M2~M0为110,FPGA将在INIT_B拉高期间设置pin脚,设置加载模式为SelectMap方式。随后反熔丝FPGA将按指定时序从Nor Flash中读取配置数据进行表决,将表决通过的配置数据沿CCLK送至SelectMap接口数据线上。然后模块将持续监测DONE信号查看是否加载成功,若超过预设的配置时间仍未拉高,则产生PROG_B低电平脉冲对Xilinx FPGA进行重载,重载8次仍不成功则回到初始化状态对FPGA进行复位。反熔丝FPGA与Nor Flash接口信号主要由Address[22:0]、CE#、OE#、WE#、Data[15:0]、RY/BY#等信号构成,接口时序图如下图所示。

(3)定时刷新。当监测到DONE信号拉高后,则说明Xilinx FPGA加载成功。随后按10MHz

的工作频率执行定时刷新操作并对写读FAR寄存器进行SEFI检测,检测到单粒子翻转则进行

FPGA重载。根据用户手册,XC5VFX130 FPGA的配置数据共有1065221字(25981帧*41字/帧)。如下图所示,刷新FPGA与待加载FPGA接口信号主要由PROG_B、INIT_B、DATA[0:7]、CCLK、DONE、RDWR_B、CS_B等信号构成。

3.应用验证

使用Modelsim对设计的RTL电路进行了仿真,并进行了应用验证。下图所示为刷新控制模块的仿真验证波形,从图中可以看出,控制模块将读取的配置数据通过SelectMap接口对FPGA进行定时刷新,刷新时序符合FPGA芯片手册的要求。随后通过模拟故障注入的方式对单粒子翻转进行了模拟,禁止刷新功能,并且经JTAG调试接口对XILINXFPGA加载错误的bit文件;注入错误的配置文件后单机遥测存在异常,打开刷新功能后单机功能恢复正常。上述验证方案表明本文设计的系

统功能能够及时纠正单粒子错误。