Note:文章内容以Xilinx 7系列FPGA进行讲解

1、什么是时钟抖动

时钟抖动就是时钟周期之间出现的偏差。比如一个时钟周期为10ns的时钟,理想情况下,其上升沿会出现在0ns,10ns,20ns···时刻,假设某个上升沿出现的时刻为30ns,那么下一个上升沿出现的时刻应该为40ns。但是实际上下一个上升沿出现的时刻可能是40.1ns或39.9ns。那么这个0.1ns的偏差就称为时钟抖动。如下图所示:

时钟抖动是在时钟发生器内部产生的,和晶振或MMCM/PLL内部电路有关,布线对其没有影响。

2、时钟抖动与时钟偏移的区别

对比时钟偏移和时钟抖动,如下图所示:

我们从图中可以看出,时钟偏移反映的是两个时钟之间的相位关系,而时钟抖动是每个时钟都具有的基本特征。

3、时钟抖动对时序的影响

以下图为例进行说明:

根据静态时序分析理论,对于单周期时序路径,发起沿为图中标记①对应的上升沿,捕获沿为图中标记③对应的上升沿。若标记①对应0ns,则标记③可能对应Tclk+Jitter或Tclk-Jitter(Jitter表示时钟抖动)。考虑到最坏情况,应按Tclk-Jitter进行分析。这意味着有效时钟周期为Tclk-Jitter。由此可见,时钟抖动进一步减小了建立时间裕量,增加了建立时间收敛的难度。对于保持时间裕量,由于发送沿与捕获沿均为图中标记①对应的上升沿,因此时钟抖动对保持时间裕量没有影响。

4、优化方法

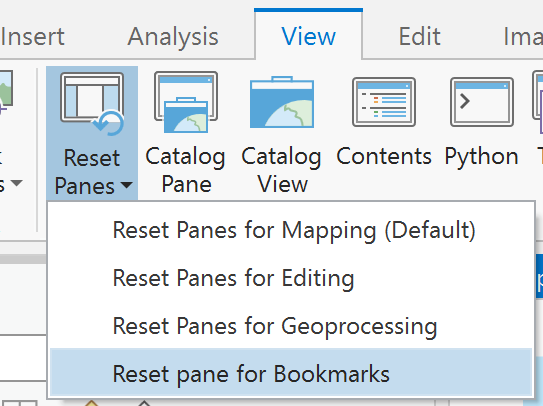

常用的降低时钟抖动的方法是利用Clocking Wizard IP中的Minimize Output Jitter选项进行优化,如下图所示:

其中,Balanced用于在功耗和抖动之间获得折中。Minimize Output Jitter则是以牺牲功耗(有时也包括输出时钟的相位误差)为代价换取最小的输出时钟抖动。Maximize Input Jitter filtering则允许输入时钟有较大的抖动,但对输出时钟抖动有负面影响。

实际上,Jitter Optimization与MMCM的属性BANDWIDTH是对应的。例如:

- 当Jitter Optimization选择Balanced时 ,对应的BANDWIDTH是OPTIMIZED

- 当Jitter Optimization选择Minimize Output Jitter时 ,对应的BANDWIDTH是HIGH

- 当Jitter Optimization选择Maximize Input Jitter filtering时,对应的BANDWIDTH是LOW

~End~

![[CKS] K8S AppArmor Set Up](https://i-blog.csdnimg.cn/direct/882683808a7f4174b6c1be9748c2682b.png)