Tomasulo算法详细解释

Tomasulo算法是一种用于处理器中的动态调度技术,它允许指令在保持数据依赖性的同时进行乱序执行。这种算法由IBM的Robert Tomasulo在1967年首次实现于IBM 360/91处理器中。

算法核心思想

Tomasulo算法的核心在于使用一组称为“保留站”(Reservation Stations, RS)的结构来跟踪指令的状态,并通过“公共数据总线”(Common Data Bus, CDB)将执行结果广播给所有需要的硬件单元。算法通过寄存器重命名消除了WAR(Write After Read)和WAW(Write After Write)相关的危险,并利用转发(Forwarding)机制来解决RAW(Read After Write)相关的危险。

关键组件

保留站(Reservation Stations)

保留站是Tomasulo算法中用于缓存指令的结构,它们等待操作数(operands)变得可用,以便可以执行指令。每个保留站可以包含以下信息:

- 操作类型(Op)

- 操作数的值(Vj, Vk)

- 操作数是否就绪的标志(Ready flags)

- 功能单元的标识(FU)

- 寄存器结果状态(Register result status)

公共数据总线(Common Data Bus)

CDB是连接功能单元和保留站的总线,用于广播完成指令的结果。CDB上的信息包括数据和来源标识,这样所有监听CDB的保留站和寄存器都可以根据来源标识获取数据。

寄存器重命名

Tomasulo算法通过寄存器重命名来消除WAR和WAW相关的危险。每次写入架构寄存器时,都会分配一个物理寄存器,直到该架构寄存器再次被写入。这种方法保留了RAW依赖性,但简化了硬件设计。

算法流程

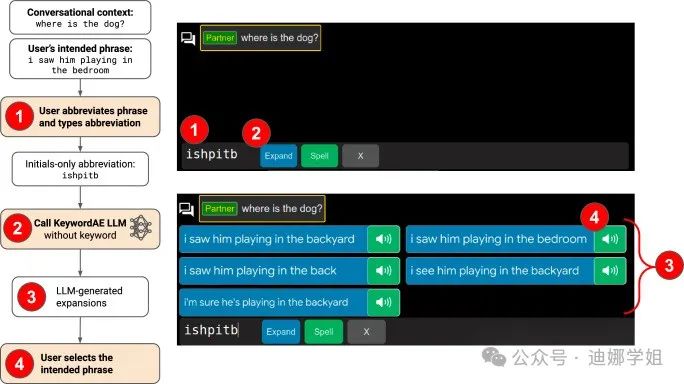

- 发射(Issue):从操作队列中获取指令,如果保留站空闲且没有结构性危险,记分牌将发出指令并将操作数重命名。

- 执行(Execution):当操作数就绪时执行操作;如果没有就绪,则监视CDB以获取结果。

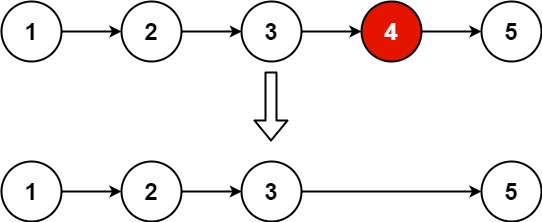

- 写回(Write-back):在CDB上向所有等待的单元广播结果;标记保留站为可用。

优势与应用

Tomasulo算法的优势在于它能够动态调度指令,包括加载/存储操作,而不需要静态调度所需的复杂编译器支持。它通过增加可用于保存寄存器值的位置、动态地基于指令实际完成和操作数可用性做出调度决策,以及完全消除内存引用的歧义,从而更有效地利用并行性,提高指令吞吐量和功能单元利用率。