|

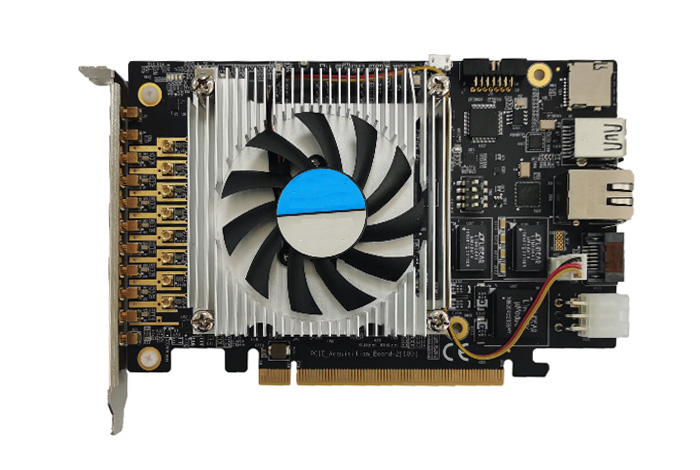

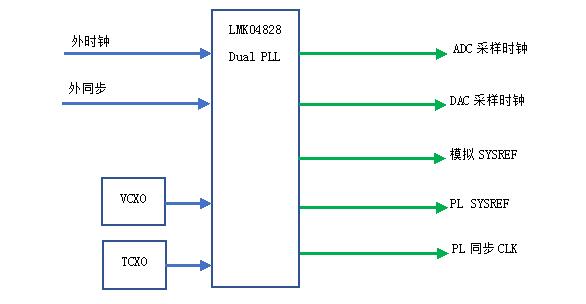

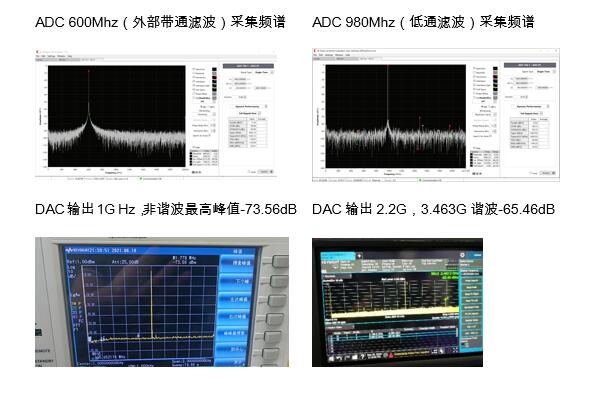

430-基于RFSOC的8路5G ADC和8路10G的DAC PCIe卡

| |

|

太速科技-430-基于RFSOC的8路5G ADC和8路10G的DAC PCIe卡

news2026/2/11 7:43:02

本文来自互联网用户投稿,该文观点仅代表作者本人,不代表本站立场。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如若转载,请注明出处:http://www.coloradmin.cn/o/2227779.html

如若内容造成侵权/违法违规/事实不符,请联系多彩编程网进行投诉反馈,一经查实,立即删除!相关文章

SpringBoot篇(运维实用篇 - 临时属性)

目录 一、临时属性设置

1. 简介

2. 属性加载优先级

那是否还有其他的配置方式呢?

3. 知识小结

二、开发环境中使用临时属性

1. 如何操作

2. 知识小结

3. 思考

三、配置文件分类

1. 简介

2. 4个级别

3. 为什么设计多种配置文件?

一个典型的应…

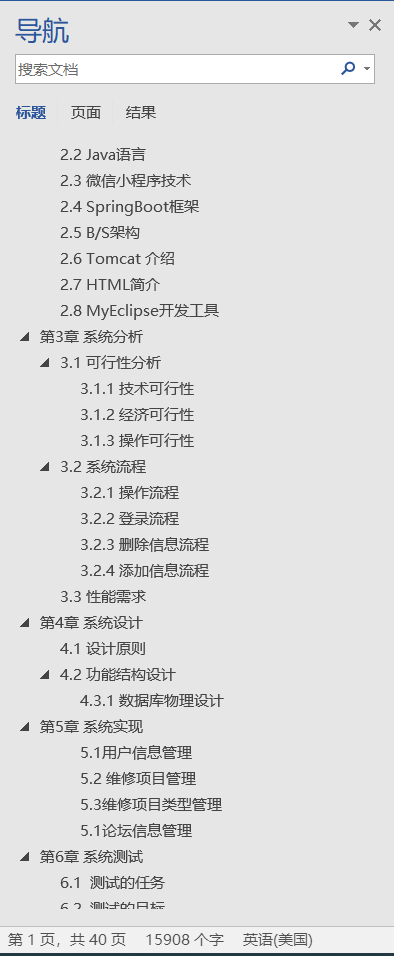

基于SSM+微信小程序的汽车维修管理系统(汽车5)

👉文末查看项目功能视频演示获取源码sql脚本视频导入教程视频

1、项目介绍

基于SSM微信小程序的汽车维修管理系统实现了三个角色:管理员、员工、用户。

1、管理员实现了首页、管理员管理员、员工管理、用户管理、车辆信息管理、配件管理等

2、员工实…

【51 Pandas+Pyecharts | 深圳市共享单车数据分析可视化】

文章目录 🏳️🌈 1. 导入模块🏳️🌈 2. Pandas数据处理2.1 读取数据2.2 查看数据信息2.3 处理起始时间、结束时间2.4 增加骑行时长区间列2.5 增加骑行里程区间列 🏳️🌈 3. Pyecharts数据可视化3.1 各…

海亮科技亮相第84届中国教装展 尽显生于校园 长于校园教育基因

10月25日,第84届中国教育装备展示会(以下简称“教装展”)在昆明滇池国际会展中心开幕。作为国内教育装备领域规模最大、影响最广的专业展会,本届教装展以“数字赋能教育,创新引领未来”为主题,为教育领域新…

Mac 电脑 使用sudo创建项目后,给了读写权限,仍报权限问题

问题:sudo创建的项目,都已经改成读写权限了,但是修改项目中的内容还是报没权限。

原因:当你使用 sudo 创建项目时。这是因为 sudo 会以 root 用户的身份创建文件和目录,这些文件和目录默认属于 root 用户,…

【JavaScript】入门详解

JavaScript 作为 Web 开发的基石,赋予了网页动态交互的能力。本文将深入浅出地讲解 JavaScript 的核心概念,并结合最新用法进行详细解释和示例。 1. JavaScript 简介

JavaScript 是一种解释型脚本语言,也称弱类型语言,最初设计用…

标准正态分布的数据 tensorflow 实现正态分布图,python 编程,数据分析和人工智能...

登录后复制 import tensorflow as tfimport matplotlib.pyplot as plt# 设置随机种子以获得可重复的结果tf.random.set_seed(42)# 生成正态分布的数据# mean0 和 stddev1 表示生成标准正态分布的数据# shape(1000,) 表示生成1000个数据点data tf.random.normal(mean0, stddev1…

Web3 与人工智能的跨界合作:重塑数字经济的新引擎

在当今数字化浪潮汹涌澎湃的时代,Web3 和人工智能这两大前沿技术的跨界合作正逐渐成为重塑数字经济的强大新引擎。

Web3 代表着互联网的新一代发展方向,强调去中心化的理念、用户主权以及数据隐私保护。它致力于打破传统互联网由少数巨头掌控的格局&…

【问题记录】当机器人存在多个串口需要绑定时udevadm的作用

一、正常绑定

输入sudo udevadm info -a /dev/ttyUSBx | grep KERNELS 命令

会出现KERNELS的编号,记录编号。 修改规则文件/etc/udev/rules.d/99-usb.rules 添加以下命令

KERNEL"ttyUSB*", KERNELS"2-1.2:1.0", MODE:"0666", GROU…

江协科技STM32学习- P24 DMA数据转运DMA+AD多通道

🚀write in front🚀 🔎大家好,我是黄桃罐头,希望你看完之后,能对你有所帮助,不足请指正!共同学习交流 🎁欢迎各位→点赞👍 收藏⭐️ 留言📝…

论文阅读 - Pre-trained Online Contrastive Learning for Insurance Fraud Detection

Pre-trained Online Contrastive Learning for Insurance Fraud Detection| Proceedings of the AAAI Conference on Artificial Intelligence

目录

摘要

Introduction

Methodology

Problem Formulation

Pre-trained Model for Enhanced Robustness

Detecting Network a…

pycharm与anaconda下的pyside6的安装记录

一、打开anaconda虚拟环境的命令行窗口,pip install,加入清华源:

pip install PySide6 -i https://pypi.tuna.tsinghua.edu.cn/simple

二、打开pycharm,在文件--设置--工具--外部工具中配置一下三项: 1、 QtDesigner…

GitHub Star 数量前 5 的开源应用程序生成器

欢迎来的 GitHub Star 数量排名系列文章的第 7 篇——最受欢迎的应用程序生成器。

之前我们已经详细探讨过:在 GitHub 上最受欢迎的——无代码工具、低代码项目、内部工具、CRUD项目、自部署项目和 Airtable 开源替代品。累计超过 50 个优质项目!&#…

【主机游戏】塔尼蚀:神之堕落 游戏介绍

《塔尼蚀:神之堕落》是一款2D横版动作游戏支持简体和繁体中文

https://pan.baidu.com/s/1UT5XSwUcxGQzPOoSuNt3vw?pwdfxbt 。 游戏的基本操作包括:

移动:使用键盘的WASD或方向键进行角色的移动。攻击:鼠标左键或键盘的攻击…

【优选算法篇】前缀之序,后缀之章:于数列深处邂逅算法的光与影

文章目录 C 前缀和详解:基础题解与思维分析前言第一章:前缀和基础应用1.1 一维前缀和模板题解法(前缀和)图解分析C代码实现易错点提示代码解读题目解析总结 1.2 二维前缀和模板题解法(二维前缀和)图解分析C…

【小白学机器学习26】 极大似然估计,K2检验,logit逻辑回归(对数回归)(未完成----)

目录 1 先从一个例题出来,预期值和现实值的差异怎么评价?

1.1 这样一个问题

1.2 我们的一般分析

1.3 用到的关键点1

1.4 但是差距多远,算是远呢?

2 极大似然估计

2.1 极大似然估计的目的

2.1.1 极大似然估计要解决什么问题…

Mount Image Pro,在取证安全的环境中挂载和访问镜像文件内容

天津鸿萌科贸发展有限公司从事数据安全服务二十余年,致力于为各领域客户提供专业的数据恢复、数据备份解决方案与服务,并针对企业面临的数据安全风险,提供专业的相关数据安全培训。 天津鸿萌科贸发展有限公司是 GetData 公司数据恢复与取证工…

什么是元件符号什么是封装

话不多说直接上图 左上角就可以理解为元件的符号,右上角可以理解为元件的封装,右下角是封装得3D图,左下角是真实的芯片。

同时注意我们元件符号的小孔,在封装和焊接时我们可以参照小孔的位置以及对应的引脚。如下图所示ÿ…

AUTOSAR 规范中的设计模式:传感器执行器模式

在 AUTOSAR Adaptive Platform (AP) 规范中,传感器执行器模式是一种典型的设计模式,主要用于实时控制系统中,用来实现传感器数据的获取和执行器指令的发送。该模式通过分离传感器和执行器的实现,使其独立运行并且能够通过某种通信…