目录

1. 简介

2. 设计调试

2.1 Physical Layer

2.2 Link Layer

2.3 Receiver

2.4 IP 接口

2.5 调试过程

2.5.1 Block Design

2.5.2 释放 gt_reset

2.5.3 观察数据

3. 实用技巧

3.1 GT 坐标与布局

3.1.1 选择器件并进行RTL分析

3.1.2 进入平面设计

3.1.3 收发器布局(基础IP)

3.1.4 收发器布局(平面视图)

3.1.5 示例 aurora(zcu106)

3.1.6 示例 aurora(zcu102)

3.1.7 时钟区域与Quad区域

3.2 共享逻辑

3.3 例化模板

3.4 Block Design TCL

4. 总结

1. 简介

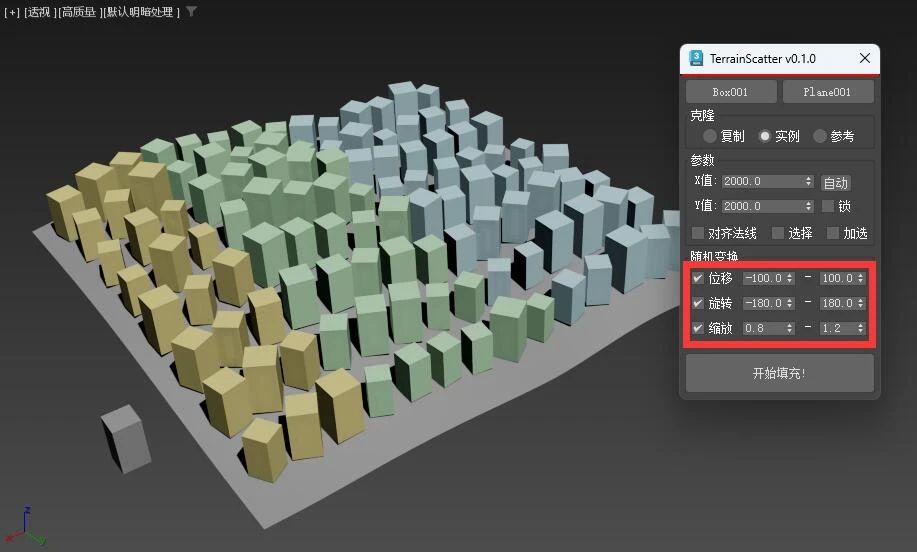

本文介绍在 Block Design 中添加 Aurora 8B/10B IP 并加以调试。

- 使用 Streaming 接口

- 使用 VIO 控制回环方式

- 探究收发器的位置信息

- 共享逻辑和例化模板

- 附带 Block Design 的 TCL 代码

2. 设计调试

2.1 Physical Layer

- INIT clk

由于在 gt_reset 断言时 user_clk 会停止工作,因此需要 init_clk_in 提供时钟信号来确保系统的正常复位过程。

2.2 Link Layer

接口(帧与数据流)

Aurora 8B/10B Core 在连接到 Aurora 通道对象时会自动初始化通道,并以帧或数据流的形式在通道中自由传递数据。

Aurora 帧可以是任意大小,并且可以随时中断。有效数据字节之间的间隙会自动用空闲填充,以保持锁定并防止电磁干扰。流量控制可用于降低传入数据的速率或通过通道发送简短的高优先级消息。

流是单个、无休止的帧。在没有数据的情况下,会传输空闲信号以保持链路处于活动状态。 Aurora 8B/10B内核使用 8B/10B 编码规则检测单位错误和大多数多位错误。过多的位错误、断开连接或设备故障会导致内核重置并尝试重新初始化新通道。

2.3 Receiver

2.4 IP 接口

本示例使用 Block Design 直接连接。

如果还要继续在同一个 Block Design 中添加此 IP,会出现额外端口,用于级联。

重要信号解释:

- channel_up:通道初始化完成,且通道准备好进行数据传输时,生效。

- lane_up:在每个通道成功初始化时进行断言,每个比特代表一个通道。

- user_clk_out:由 Aurora 8B/10B 核心共享的并行时钟(共享逻辑在 IP 中)。

- reset:高电平有效。

- gt_reset:高电平有效。

- loopback:

| Port | Dir | Clock Domain | Description |

|---------------|-----|--------------|----------------------------|

| LOOPBACK[2:0] | In | Async | 000: Normal operation |

| | | | 001: Near-end PCS Loopback |

| | | | 010: Near-end PMA Loopback |

| | | | 011: Reserved |

| | | | 100: Far-end PMA Loopback |

| | | | 101: Reserved |

| | | | 110: Far-end PCS Loopback |《UltraScale Architecture GTH Transceivers User Guide (UG576)》(Table-36)

2.5 调试ZCU106

2.5.1 Block Design

器件:xczu7ev-ffvc1156-2-e

对于 ZCU106 板卡,主要约束为:

set_property PACKAGE_PIN U10 [get_ports GT_DIFF_REFCLK1_0_clk_p]

set_property PACKAGE_PIN AH12 [get_ports {CLK_IN_D_0_clk_p[0]}]

set_property IOSTANDARD DIFF_SSTL12 [get_ports {CLK_IN_D_0_clk_p[0]}]

set_property IOSTANDARD LVCMOS12 [get_ports ext_reset_in_0]

set_property PACKAGE_PIN AP20 [get_ports ext_reset_in_0]Debug hub 相关约束会自动生成。

2.5.2 释放 gt_reset

通过释放 gt_reset,Aurora IP 将自动建立链接。

2.5.3 观察数据

从 tx_valid 被选中 '1'(数据有效)后,便可从 ILA 中观察到回传的数据了。

由于 tx_valid 是一直为高,回传数据也一直有效,除了收发器周期性发送的控制码期间。

2.6 调试ZCU102

2.6.1 Block Design

Block Design 与 2.5 章节保持一致。不同的是,ZCU102 的时钟输入、复位输入可以使用预先配置的信息,因此只需指定 REFCLK 即可:

set_property PACKAGE_PIN C8 [get_ports GT_DIFF_REFCLK1_0_clk_p]2.6.2 观察数据

3. 实用技巧

3.1 GT 坐标与布局

- 收发器 GTX/GTH/GTY 等位置信息(XxYy)

- 收发器的 Bank 编号怎么确定

- 收发器的 Quad 是指什么

3.1.1 选择器件并进行RTL分析

新建工程时选择,或者在 Project Summary 中选择。

要进行 RTL 分析,需要指定 top module,可以通过创建一个空白 Block Design,然后生成一个空 wraper。

`timescale 1 ps / 1 ps

module design_1_wrapper

();

design_1 design_1_i

();

endmodule然后可以打开 Elaborated Design。

3.1.2 进入平面设计

平面设计,即 Floorplanning 视图。

打开 Elaborated Design 后,可以选择 Floorplanning 视图。

Floorplanning 视图如下:

3.1.3 收发器布局(基础IP)

收发器一般都放置在芯片的边缘,因为其主要功能时与外部设备通讯,这样可以简化 I/O 布线,并减少信号路径的长度,从而降低信号衰减和干扰。

在 Vivado 软件 中,有多种途径可查看到收发器的分布信息,首先演示基础 IP 所展示的信息:

UltraScale FPGAs Transceivers Wizard v1.7

从基础 IP 看到 xczu9eg-ffvb1156-2-e 器件的一些收发器信息:

- 左右两侧各有3个 Quad,12个 Channel

- 每个 Channel 对应有自己的 XxYy 坐标标号

- 每个 Quad 的 Bank 和对应 Pin 的信息

- 在 Physical Resources 中,也可以看到各自资源的位置分布

3.1.4 收发器布局(平面视图)

1)根据资源种类进行筛选

Floorplanning 视图下,通过右侧的 Resource Types 可以筛选视图内容。

2)未启用的 GT 资源

通过筛选 GT transceiver 资源,可以明显观察到有7个 Quad,似乎与基础 IP 描述不符?

放大 Clock Regin X0Y3 这个区域的 Quad 并未启用,故收发器资源有6个可用。

3)公共资源

4)Site Properties

SITE 即不同类型逻辑资源,包括 SLICE/CLBs,这些是基本逻辑元素(BELs)的集合,例如查找表(LUTs)、触发器、多路复用器、以及用于实现快速加法、减法或比较操作的进位逻辑资源。SLICE/CLBs 中包含宽位宽的多路复用器,并有专用的进位链垂直从一个 SLICE 运行到另一个SLICE。

在 Site Properties 中,同样可以看到所有的 Transceivers Wizard 中的信息。

3.1.5 示例 aurora(zcu106)

器件:xczu7ev-ffvc1156-2-e

IP:Aurora 8B10B v11.1

1)需要确认的信息包括:

- Column 位置信息(Column Used)

- Quad 信息(Starting GT Quad)

- Channel信息(Starting GT Lane)

- 参考时钟(GT Refclk Selection)

2)查看原理图

确认如下信息:

- 使用 Channel 0,对应的引脚是 U6、U5

- 参考时钟取自 REFCLK1

在基础 IP 中搜索 Pin 信息:

即可确认位置信息:

- Column 位置信息(Column Used)= right

- Quad 信息(Starting GT Quad)= Quad X0Y3

- Channel信息(Starting GT Lane)= X0Y12

- 参考时钟(GT Refclk Selection)= MGTREFCLK1

3)最终配置如下

3.1.6 示例 aurora(zcu102)

1)原理图

2)GT IP 搜索结果

3)最终配置如下

- Column 位置信息(Column Used)= right

- Quad 信息(Starting GT Quad)= Quad X1Y3

- Channel信息(Starting GT Lane)= X1Y12

- 参考时钟(GT Refclk Selection)= MGTREFCLK0

3.1.7 时钟区域与Quad区域

时钟区域与 GT Quad 区域有各自的位置坐标编码规则,GT Quad 的坐标是跨越时钟区域坐标的,如下图:

- 时钟区域从左到右共4列:X0,X1,X2,X3

- GT Quad 区域只在最左侧和最右侧分布,共2列:Quad_X0,Quad_X1

- Quad_X0 属于时钟区域 X0 中,Quad_X1 属于时钟区域 X3

3.2 共享逻辑

《Aurora 8B/10B LogiCORE IP Product Guide (PG046)》,由于选择共享逻辑选项导致的一些端口变化,增加一些端口。

1)共享逻辑的概念:

Include Shared Logic in Core:将共享逻辑资源包含在 IP 核内部,即所有需要的逻辑资源(如 时钟、复位、缓冲区等)都在 IP 核内部实现。

Include Shared Logic in Example Design:将共享逻辑资源从 IP 核内部移除,并在示例设计中实现。这种方式允许多个 IP 核实例共享同一组逻辑资源。

2)信号变化的原因:

资源共享:当选择共享逻辑时,多个 IP 核实例可能会共享同一组资源。

端口配置:共享逻辑选项会影响到端口的配置。例如,某些时钟和复位信号可能会从 IP 核内部移到外部,以便与其他实例共享。

共享逻辑的连接方法:

3.3 例化模板

通过 IP Sources 可以查看完整的例化模板:

//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

aurora_8b10b_0 your_instance_name (

.s_axi_tx_tdata (s_axi_tx_tdata ), // input wire [0 : 15] s_axi_tx_tdata

.s_axi_tx_tvalid (s_axi_tx_tvalid ), // input wire s_axi_tx_tvalid

.s_axi_tx_tready (s_axi_tx_tready ), // output wire s_axi_tx_tready

.m_axi_rx_tdata (m_axi_rx_tdata ), // output wire [0 : 15] m_axi_rx_tdata

.m_axi_rx_tvalid (m_axi_rx_tvalid ), // output wire m_axi_rx_tvalid

.hard_err (hard_err ), // output wire hard_err

.soft_err (soft_err ), // output wire soft_err

.channel_up (channel_up ), // output wire channel_up

.lane_up (lane_up ), // output wire [0 : 0] lane_up

.txp (txp ), // output wire [0 : 0] txp

.txn (txn ), // output wire [0 : 0] txn

.reset (reset ), // input wire reset

.gt_reset (gt_reset ), // input wire gt_reset

.loopback (loopback ), // input wire [2 : 0] loopback

.rxp (rxp ), // input wire [0 : 0] rxp

.rxn (rxn ), // input wire [0 : 0] rxn

.gt0_drpaddr (gt0_drpaddr ), // input wire [9 : 0] gt0_drpaddr

.gt0_drpen (gt0_drpen ), // input wire gt0_drpen

.gt0_drpdi (gt0_drpdi ), // input wire [15 : 0] gt0_drpdi

.gt0_drprdy (gt0_drprdy ), // output wire gt0_drprdy

.gt0_drpdo (gt0_drpdo ), // output wire [15 : 0] gt0_drpdo

.gt0_drpwe (gt0_drpwe ), // input wire gt0_drpwe

.power_down (power_down ), // input wire power_down

.tx_lock (tx_lock ), // output wire tx_lock

.tx_resetdone_out (tx_resetdone_out ), // output wire tx_resetdone_out

.rx_resetdone_out (rx_resetdone_out ), // output wire rx_resetdone_out

.link_reset_out (link_reset_out ), // output wire link_reset_out

.init_clk_in (init_clk_in ), // input wire init_clk_in

.user_clk_out (user_clk_out ), // output wire user_clk_out

.pll_not_locked_out (pll_not_locked_out ), // output wire pll_not_locked_out

.sys_reset_out (sys_reset_out ), // output wire sys_reset_out

.gt_refclk1_p (gt_refclk1_p ), // input wire gt_refclk1_p

.gt_refclk1_n (gt_refclk1_n ), // input wire gt_refclk1_n

.sync_clk_out (sync_clk_out ), // output wire sync_clk_out

.gt_reset_out (gt_reset_out ), // output wire gt_reset_out

.gt_refclk1_out (gt_refclk1_out ), // output wire gt_refclk1_out

.gt_powergood (gt_powergood ) // output wire [0 : 0] gt_powergood

);

// INST_TAG_END ------ End INSTANTIATION Template ---------3.4 Block Design TCL

################################################################

# This is a generated script based on design: design_1

#

# Though there are limitations about the generated script,

# the main purpose of this utility is to make learning

# IP Integrator Tcl commands easier.

################################################################

namespace eval _tcl {

proc get_script_folder {} {

set script_path [file normalize [info script]]

set script_folder [file dirname $script_path]

return $script_folder

}

}

variable script_folder

set script_folder [_tcl::get_script_folder]

################################################################

# Check if script is running in correct Vivado version.

################################################################

set scripts_vivado_version 2022.1

set current_vivado_version [version -short]

if { [string first $scripts_vivado_version $current_vivado_version] == -1 } {

puts ""

catch {common::send_gid_msg -ssname BD::TCL -id 2041 -severity "ERROR" "This script was generated using Vivado <$scripts_vivado_version> and is being run in <$current_vivado_version> of Vivado. Please run the script in Vivado <$scripts_vivado_version> then open the design in Vivado <$current_vivado_version>. Upgrade the design by running \"Tools => Report => Report IP Status...\", then run write_bd_tcl to create an updated script."}

return 1

}

################################################################

# START

################################################################

# To test this script, run the following commands from Vivado Tcl console:

# source design_1_script.tcl

# If there is no project opened, this script will create a

# project, but make sure you do not have an existing project

# <./myproj/project_1.xpr> in the current working folder.

set list_projs [get_projects -quiet]

if { $list_projs eq "" } {

create_project project_1 myproj -part xczu7ev-ffvc1156-2-e

set_property BOARD_PART xilinx.com:zcu106:part0:2.6 [current_project]

}

# CHANGE DESIGN NAME HERE

variable design_name

set design_name design_1

# If you do not already have an existing IP Integrator design open,

# you can create a design using the following command:

# create_bd_design $design_name

# Creating design if needed

set errMsg ""

set nRet 0

set cur_design [current_bd_design -quiet]

set list_cells [get_bd_cells -quiet]

if { ${design_name} eq "" } {

# USE CASES:

# 1) Design_name not set

set errMsg "Please set the variable <design_name> to a non-empty value."

set nRet 1

} elseif { ${cur_design} ne "" && ${list_cells} eq "" } {

# USE CASES:

# 2): Current design opened AND is empty AND names same.

# 3): Current design opened AND is empty AND names diff; design_name NOT in project.

# 4): Current design opened AND is empty AND names diff; design_name exists in project.

if { $cur_design ne $design_name } {

common::send_gid_msg -ssname BD::TCL -id 2001 -severity "INFO" "Changing value of <design_name> from <$design_name> to <$cur_design> since current design is empty."

set design_name [get_property NAME $cur_design]

}

common::send_gid_msg -ssname BD::TCL -id 2002 -severity "INFO" "Constructing design in IPI design <$cur_design>..."

} elseif { ${cur_design} ne "" && $list_cells ne "" && $cur_design eq $design_name } {

# USE CASES:

# 5) Current design opened AND has components AND same names.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 1

} elseif { [get_files -quiet ${design_name}.bd] ne "" } {

# USE CASES:

# 6) Current opened design, has components, but diff names, design_name exists in project.

# 7) No opened design, design_name exists in project.

set errMsg "Design <$design_name> already exists in your project, please set the variable <design_name> to another value."

set nRet 2

} else {

# USE CASES:

# 8) No opened design, design_name not in project.

# 9) Current opened design, has components, but diff names, design_name not in project.

common::send_gid_msg -ssname BD::TCL -id 2003 -severity "INFO" "Currently there is no design <$design_name> in project, so creating one..."

create_bd_design $design_name

common::send_gid_msg -ssname BD::TCL -id 2004 -severity "INFO" "Making design <$design_name> as current_bd_design."

current_bd_design $design_name

}

common::send_gid_msg -ssname BD::TCL -id 2005 -severity "INFO" "Currently the variable <design_name> is equal to \"$design_name\"."

if { $nRet != 0 } {

catch {common::send_gid_msg -ssname BD::TCL -id 2006 -severity "ERROR" $errMsg}

return $nRet

}

set bCheckIPsPassed 1

##################################################################

# CHECK IPs

##################################################################

set bCheckIPs 1

if { $bCheckIPs == 1 } {

set list_check_ips "\

xilinx.com:ip:aurora_8b10b:11.1\

xilinx.com:ip:ila:6.2\

xilinx.com:ip:proc_sys_reset:5.0\

xilinx.com:ip:util_ds_buf:2.2\

xilinx.com:ip:vio:3.0\

xilinx.com:ip:xlconstant:1.1\

"

set list_ips_missing ""

common::send_gid_msg -ssname BD::TCL -id 2011 -severity "INFO" "Checking if the following IPs exist in the project's IP catalog: $list_check_ips ."

foreach ip_vlnv $list_check_ips {

set ip_obj [get_ipdefs -all $ip_vlnv]

if { $ip_obj eq "" } {

lappend list_ips_missing $ip_vlnv

}

}

if { $list_ips_missing ne "" } {

catch {common::send_gid_msg -ssname BD::TCL -id 2012 -severity "ERROR" "The following IPs are not found in the IP Catalog:\n $list_ips_missing\n\nResolution: Please add the repository containing the IP(s) to the project." }

set bCheckIPsPassed 0

}

}

if { $bCheckIPsPassed != 1 } {

common::send_gid_msg -ssname BD::TCL -id 2023 -severity "WARNING" "Will not continue with creation of design due to the error(s) above."

return 3

}

##################################################################

# DESIGN PROCs

##################################################################

# Procedure to create entire design; Provide argument to make

# procedure reusable. If parentCell is "", will use root.

proc create_root_design { parentCell } {

variable script_folder

variable design_name

if { $parentCell eq "" } {

set parentCell [get_bd_cells /]

}

# Get object for parentCell

set parentObj [get_bd_cells $parentCell]

if { $parentObj == "" } {

catch {common::send_gid_msg -ssname BD::TCL -id 2090 -severity "ERROR" "Unable to find parent cell <$parentCell>!"}

return

}

# Make sure parentObj is hier blk

set parentType [get_property TYPE $parentObj]

if { $parentType ne "hier" } {

catch {common::send_gid_msg -ssname BD::TCL -id 2091 -severity "ERROR" "Parent <$parentObj> has TYPE = <$parentType>. Expected to be <hier>."}

return

}

# Save current instance; Restore later

set oldCurInst [current_bd_instance .]

# Set parent object as current

current_bd_instance $parentObj

# Create interface ports

set CLK_IN_D_0 [ create_bd_intf_port -mode Slave -vlnv xilinx.com:interface:diff_clock_rtl:1.0 CLK_IN_D_0 ]

set_property -dict [ list \

CONFIG.FREQ_HZ {300000000} \

] $CLK_IN_D_0

set GT_DIFF_REFCLK1_0 [ create_bd_intf_port -mode Slave -vlnv xilinx.com:interface:diff_clock_rtl:1.0 GT_DIFF_REFCLK1_0 ]

set_property -dict [ list \

CONFIG.FREQ_HZ {156250000} \

] $GT_DIFF_REFCLK1_0

set GT_SERIAL_RX_0 [ create_bd_intf_port -mode Slave -vlnv xilinx.com:display_aurora:GT_Serial_Transceiver_Pins_RX_rtl:1.0 GT_SERIAL_RX_0 ]

set GT_SERIAL_TX_0 [ create_bd_intf_port -mode Master -vlnv xilinx.com:display_aurora:GT_Serial_Transceiver_Pins_TX_rtl:1.0 GT_SERIAL_TX_0 ]

# Create ports

set ext_reset_in_0 [ create_bd_port -dir I -type rst ext_reset_in_0 ]

set_property -dict [ list \

CONFIG.POLARITY {ACTIVE_HIGH} \

] $ext_reset_in_0

# Create instance: aurora_8b10b_0, and set properties

set aurora_8b10b_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:aurora_8b10b:11.1 aurora_8b10b_0 ]

set_property -dict [ list \

CONFIG.CHANNEL_ENABLE {X0Y12} \

CONFIG.C_DRP_IF {false} \

CONFIG.C_LINE_RATE {3.125} \

CONFIG.C_REFCLK_FREQUENCY {156.25} \

CONFIG.C_REFCLK_SOURCE {MGTREFCLK1 of Quad X0Y3} \

CONFIG.C_START_LANE {X0Y12} \

CONFIG.C_START_QUAD {Quad_X0Y3} \

CONFIG.Interface_Mode {Streaming} \

CONFIG.SupportLevel {1} \

CONFIG.TransceiverControl {false} \

] $aurora_8b10b_0

# Create instance: ila_1, and set properties

set ila_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:ila:6.2 ila_1 ]

set_property -dict [ list \

CONFIG.C_ENABLE_ILA_AXI_MON {false} \

CONFIG.C_MONITOR_TYPE {Native} \

CONFIG.C_NUM_OF_PROBES {2} \

] $ila_1

# Create instance: proc_sys_reset_0, and set properties

set proc_sys_reset_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:proc_sys_reset:5.0 proc_sys_reset_0 ]

set_property -dict [ list \

CONFIG.RESET_BOARD_INTERFACE {Custom} \

CONFIG.USE_BOARD_FLOW {true} \

] $proc_sys_reset_0

# Create instance: util_ds_buf_0, and set properties

set util_ds_buf_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:util_ds_buf:2.2 util_ds_buf_0 ]

# Create instance: util_ds_buf_1, and set properties

set util_ds_buf_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:util_ds_buf:2.2 util_ds_buf_1 ]

set_property -dict [ list \

CONFIG.C_BUFGCE_DIV {6} \

CONFIG.C_BUF_TYPE {BUFGCE_DIV} \

] $util_ds_buf_1

# Create instance: vio_0, and set properties

set vio_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:vio:3.0 vio_0 ]

set_property -dict [ list \

CONFIG.C_NUM_PROBE_IN {3} \

CONFIG.C_NUM_PROBE_OUT {4} \

CONFIG.C_PROBE_OUT0_WIDTH {16} \

CONFIG.C_PROBE_OUT2_INIT_VAL {0x2} \

CONFIG.C_PROBE_OUT2_WIDTH {3} \

CONFIG.C_PROBE_OUT3_INIT_VAL {0x1} \

CONFIG.C_PROBE_OUT4_INIT_VAL {0x1} \

CONFIG.C_PROBE_OUT5_INIT_VAL {0x1} \

] $vio_0

# Create instance: xlconstant_0, and set properties

set xlconstant_0 [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconstant:1.1 xlconstant_0 ]

# Create instance: xlconstant_1, and set properties

set xlconstant_1 [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconstant:1.1 xlconstant_1 ]

set_property -dict [ list \

CONFIG.CONST_VAL {0} \

] $xlconstant_1

# Create instance: xlconstant_2, and set properties

set xlconstant_2 [ create_bd_cell -type ip -vlnv xilinx.com:ip:xlconstant:1.1 xlconstant_2 ]

set_property -dict [ list \

CONFIG.CONST_VAL {0} \

] $xlconstant_2

# Create interface connections

connect_bd_intf_net -intf_net CLK_IN_D_0_1 [get_bd_intf_ports CLK_IN_D_0] [get_bd_intf_pins util_ds_buf_0/CLK_IN_D]

connect_bd_intf_net -intf_net GT_DIFF_REFCLK1_0_1 [get_bd_intf_ports GT_DIFF_REFCLK1_0] [get_bd_intf_pins aurora_8b10b_0/GT_DIFF_REFCLK1]

connect_bd_intf_net -intf_net GT_SERIAL_RX_0_1 [get_bd_intf_ports GT_SERIAL_RX_0] [get_bd_intf_pins aurora_8b10b_0/GT_SERIAL_RX]

connect_bd_intf_net -intf_net aurora_8b10b_0_GT_SERIAL_TX [get_bd_intf_ports GT_SERIAL_TX_0] [get_bd_intf_pins aurora_8b10b_0/GT_SERIAL_TX]

# Create port connections

connect_bd_net -net aurora_8b10b_0_channel_up [get_bd_pins aurora_8b10b_0/channel_up] [get_bd_pins vio_0/probe_in1]

connect_bd_net -net aurora_8b10b_0_lane_up [get_bd_pins aurora_8b10b_0/lane_up] [get_bd_pins vio_0/probe_in2]

connect_bd_net -net aurora_8b10b_0_m_axi_rx_tdata [get_bd_pins aurora_8b10b_0/m_axi_rx_tdata] [get_bd_pins ila_1/probe0]

connect_bd_net -net aurora_8b10b_0_m_axi_rx_tvalid [get_bd_pins aurora_8b10b_0/m_axi_rx_tvalid] [get_bd_pins ila_1/probe1]

connect_bd_net -net aurora_8b10b_0_s_axi_tx_tready [get_bd_pins aurora_8b10b_0/s_axi_tx_tready] [get_bd_pins vio_0/probe_in0]

connect_bd_net -net ext_reset_in_0_1 [get_bd_ports ext_reset_in_0] [get_bd_pins proc_sys_reset_0/ext_reset_in]

connect_bd_net -net proc_sys_reset_0_peripheral_reset [get_bd_pins aurora_8b10b_0/reset] [get_bd_pins proc_sys_reset_0/peripheral_reset]

connect_bd_net -net util_ds_buf_0_IBUF_OUT [get_bd_pins aurora_8b10b_0/init_clk_in] [get_bd_pins ila_1/clk] [get_bd_pins proc_sys_reset_0/slowest_sync_clk] [get_bd_pins util_ds_buf_1/BUFGCE_O] [get_bd_pins vio_0/clk]

connect_bd_net -net util_ds_buf_0_IBUF_OUT1 [get_bd_pins util_ds_buf_0/IBUF_OUT] [get_bd_pins util_ds_buf_1/BUFGCE_I]

connect_bd_net -net vio_0_probe_out0 [get_bd_pins aurora_8b10b_0/s_axi_tx_tdata] [get_bd_pins vio_0/probe_out0]

connect_bd_net -net vio_0_probe_out1 [get_bd_pins aurora_8b10b_0/s_axi_tx_tvalid] [get_bd_pins vio_0/probe_out1]

connect_bd_net -net vio_0_probe_out2 [get_bd_pins aurora_8b10b_0/loopback] [get_bd_pins vio_0/probe_out2]

connect_bd_net -net vio_0_probe_out3 [get_bd_pins aurora_8b10b_0/gt_reset] [get_bd_pins vio_0/probe_out3]

connect_bd_net -net xlconstant_0_dout [get_bd_pins util_ds_buf_1/BUFGCE_CE] [get_bd_pins xlconstant_0/dout]

connect_bd_net -net xlconstant_1_dout [get_bd_pins util_ds_buf_1/BUFGCE_CLR] [get_bd_pins xlconstant_1/dout]

connect_bd_net -net xlconstant_2_dout [get_bd_pins aurora_8b10b_0/power_down] [get_bd_pins xlconstant_2/dout]

# Create address segments

# Restore current instance

current_bd_instance $oldCurInst

validate_bd_design

save_bd_design

}

# End of create_root_design()

##################################################################

# MAIN FLOW

##################################################################

create_root_design ""4. 总结

理解 IP 重要信号:

- channel_up:通道初始化完成,且通道准备好进行数据传输时,生效。

- lane_up:在每个通道成功初始化时进行断言,每个比特代表一个通道。

- user_clk_out:由 Aurora 8B/10B 核心共享的并行时钟(共享逻辑在 IP 中)。

- reset:高电平有效。

- gt_reset:高电平有效。

- loopback:回环控制

IP 使用非常简单,只需简单配置即可。

使用基础 IP 查找位置信息非常方便。