这里写目录标题

- 前言

- MCU时钟介绍

- PLL

- CRG_ConfigPLL时钟配置

- 另附完整系统时钟结构图

前言

Hi3061M使用过程中,AD和APT输出,都需要考虑到时钟频率,特别是APT,关系到PWM的输出频率。于是就研究了下相关的时钟。

MCU时钟介绍

MCU共有三个源时钟:HOSC、LOSC和XTAL。

HOSC是MCU集成的高精度高速振荡器,提供25MHz时钟clk_hosc。clk_hosc是MCU CORE电源域的默认时钟。

LOSC是MCU集成的低速振荡器,提供32kHz时钟clk_losc。clk_losc是MCU AON电源域的默认时钟,也为IWDG(Independent Watch Dog)模块提供计数时钟。

XTAL支持高速外部晶体或外部时钟源,提供4MHz ~ 30MHz时钟clk_xtal。

clk_hosc是MCU CORE电源域的默认时钟,说明系统的主要时钟是clk_hosc,也就是25MHz。

当然,之后还需要经过PLL锁相环来进行调节频率提供给外设工作时钟。

PLL

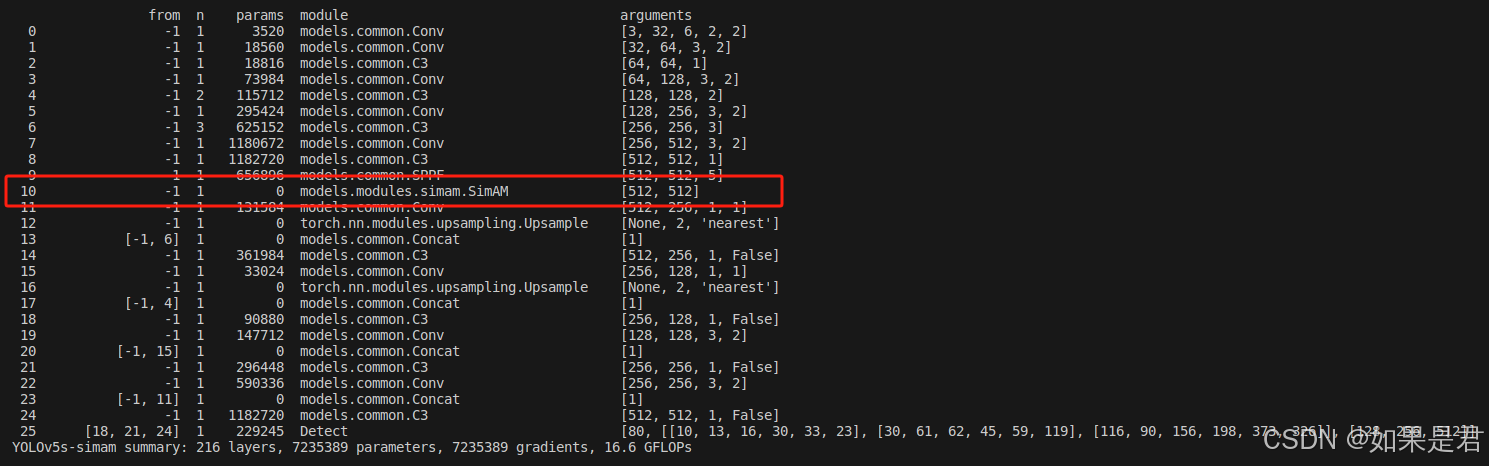

由上图是Hi3061M系统的时钟图,PLL部分,由上节我们知道,数据选择器(MUX)将会选择clk_hosc作为主要时钟,也就是25MHz。

之后会先经过prediv前置分频器进行分频后,再通过反馈分频器fbdiv进行倍频处理,再通过后面两个后置分频器进行分频作为两个工作时钟提供给外设。

对应的数据选择器和分频器都可以通过寄存器进行配置,软件进行设置。

在system_init.c文件中通常有一个相关时钟配置的函数CRG_Config如下:

BASE_StatusType CRG_Config(CRG_CoreClkSelect *coreClkSelect)

{

CRG_Handle crg;

crg.baseAddress = CRG;

crg.pllRefClkSelect = CRG_PLL_REF_CLK_SELECT_HOSC;

crg.pllPreDiv = CRG_PLL_PREDIV_4;

crg.pllFbDiv = 48; /* PLL Multiplier 48 */

crg.pllPostDiv = CRG_PLL_POSTDIV_2;

crg.coreClkSelect = CRG_CORE_CLK_SELECT_PLL;

crg.handleEx.pllPostDiv2 = CRG_PLL_POSTDIV2_3;

crg.handleEx.clk1MSelect = CRG_1M_CLK_SELECT_HOSC;

crg.handleEx.clk1MDiv = (25 - 1); /* The 1 MHz freq is equal to the input clock frequency / (clk_1m_div + 1). 25 is the div of the clk_1m in CLOCK. */

if (HAL_CRG_Init(&crg) != BASE_STATUS_OK) {

return BASE_STATUS_ERROR;

}

*coreClkSelect = crg.coreClkSelect;

return BASE_STATUS_OK;

}

改函数会在初始化时进行调用,当然似乎是上电会自动运行的,并没有在用户main中初始化调用,具体也没有仔细研究。在下面的函数中进行调用了。chipinit.c中

void Chip_Init(void)

{

CRG_CoreClkSelect coreClkSelect;

/* Config CRG */

if (CRG_Config(&coreClkSelect) != BASE_STATUS_OK) {

Chip_InitFail();

}

CRG_ConfigPLL时钟配置

接下来详细分析下CRG_Config函数中相关频率的选择和分频。

crg.pllRefClkSelect = CRG_PLL_REF_CLK_SELECT_HOSC;

//图中第一个选择器,系统时钟源选择,clk_hosc,25MHz.

crg.pllPreDiv = CRG_PLL_PREDIV_4;

//前置分频器,4分频,25/4MHz

crg.pllFbDiv = 48; /* PLL Multiplier 48 */

//反馈分频器,48倍频,25/4*48 = 300MHz

crg.pllPostDiv = CRG_PLL_POSTDIV_2;

//后置分频器,2分频,300/2 = 150MHz

crg.coreClkSelect = CRG_CORE_CLK_SELECT_PLL;

//系统时钟选择,选择为经过PLL后置分频输出的时钟,也就是150MHz

crg.handleEx.pllPostDiv2 = CRG_PLL_POSTDIV2_3;

//后置分频器,3分频,300/3 = 100MHz 主要用于ADC

clk_pll_pst1即是150MHz,也就是系统的时钟,大多数外设都是在这个时钟频率上工作。

clk_pll_pst2即是100MHz,是ADC工作的主要时钟。

ADC的时钟在使用时还需要特定的配置,进行时钟选择。

另附完整系统时钟结构图