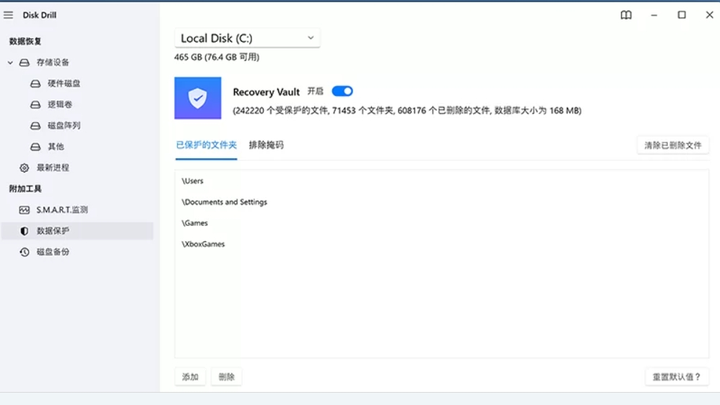

一、分层结构

PCIe定义了一个分层架构,如图2-12所示。这些层逻辑上分为两个部分,分别独立运行:一个用于发送侧,另一个用于接收侧。分层方法对硬件设计者是很有好的,因为如果逻辑划分得当,在迁移到新版本的PCIe规范时,可以只改变现有设计的某一层,而不影响其他层。

如图2-12所示,设备的层次结构包括以下部分:

-

设备核心和事务层接口( Device core and interface to Transaction Layer):核心实现设备的主要功能。如果设备是一个终端,可能包含多达8个功能(functions),每个功能都有自己的配置空间。如果设备是一个交换机,交换机核心包含数据包路由逻辑和内部总线来完成这个任务。如果设备是根复合体,根核心则实现虚拟的PCI总线0,其中包含所有嵌入的端点和虚拟桥接器。

-

事务层(Transaction Layer):该层负责在发送侧创建事务层数据包(TLP),并在接收侧解码TLP。此外,事务层还有QoS(Quality of Service)和流量控制(Flow Control)以及Transaction Ordering等功能。

-

数据链路层(Data Link Layer):该层负责在发送侧创建数据链路层数据包(DLLP),并在接收侧解码DLLP。此外,它还负责链路错误检测和纠正,这一功能称为Ack/Nak协议。

-

物理层(Physical Layer):物理层负责Ordered-Set Packet的创建于解码。同时负责发送与接收所有类型的包(TLPs、DLLPs和Ordered-Sets)。当前在发送之前,还需要对包进行一些列的处理,如Byte Striping、Scramble(扰码)和Encoder(8b/10b for Gen1&Gen2, 128b/130b for Gen3& Gen4)。对应的,在接收端就需要进行相反的处理。此外,物理层还实现了链路训练(Link Training)和链路初始化(Link Initialization)的功能,这一般是通过链路训练状态机(Link Training and Status State Machine,LTSSM)来完成的。

二、架构概述

总的来说,PCIe的分层架构有助于数据传输的模块化设计和灵活性,每一层各自负责特定的功能并相互协作,以完成设备之间的数据通信。每个PCIe接口都支持这些层的功能,包括交换机端口:

原则上,每个层与链路另一端设备的对应层进行通信。上面的两层通过将一串比特组织成数据包来实现通信,形成一个可以被接收端相应层识别的模式。这些数据包通过其他层传递,最终到达链路的发送端或接收端。物理层也直接与另一设备的物理层通信,但方式有所不同。为了更好地理解这一点,我们可以先简单了解一下各层如何交互。

总体来说,设备发出的请求或完成数据包的内容首先在事务层(Transaction Layer)中组装,这个过程基于设备核心逻辑提供的信息,这些信息有时也被称为软件层(虽然规范中没有使用这个术语)。这些信息通常包括所需命令的类型、目标设备的地址、请求的属性等。新创建的数据包会被存储在一个称为虚拟通道(Virtual Channel)的缓冲区中,直到它准备好传递给下一层。

当数据包传递到数据链路层(Data Link Layer)时,会在数据包中添加额外的信息,以便在相邻的接收端进行错误检查,并且数据包的副本会在本地存储,以便在发生传输错误时能够重新发送。随后,数据包到达物理层(Physical Layer),在该层中,数据包会被编码并通过链路上所有可用的通道进行差分传输。

这种分层的通信机制确保每个层能够有效处理数据并确保数据在设备之间安全且可靠地传输。

接收端在物理层对传入的比特流进行解码,检查该层能够检测到的错误。如果没有发现错误,生成的数据包将被传递到数据链路层。在数据链路层,数据包会被进一步检查是否存在其他错误,如果没有错误,数据包会继续传递到事务层。在事务层,数据包会被缓冲、进行错误检查,并解包为原始信息(如命令、属性等),以便将内容传递给接收设备的核心逻辑。

接下来,我们可以更深入地探讨每一层在这个过程中所需要完成的任务,参考图2-14,我们将在后续的文章中详细讨论这部分的内容。