实验 3 存储器实验

1、实验目的

- 掌握静态随机存储器 RAM 的工作特性。

- 掌握静态随机存储器 RAM 的读写方法。

2、实验要求

(1)做好实验预习,熟悉MEMORY6116 芯片各引脚的功能和连接方式,熟悉其他实验元器件的功能特性和使用方法,看懂电路图。

(2) 按照实验内容与步骤的要求,认真仔细地完成实验

(3)写出实验报告。

3、实验电路

本实验使用的主要元器件有: 2Kx8 静态随机存储器 6116 , 8 位数据锁存器 74LS273 (实验用作地址寄存器AR),三态输出的 8 组总线收发器 74LS245 ,与非门、与门、开关、指示灯等。芯片详细说明请见附录。

下图为本实验所用的存储器原理图,图中尾端带加粗标记的信号为控制信号,其余为数字信号或地址信号。实验电路中涉及的控制信号如下:

(1) CE : 6116 片选信号。为 0 时 6116 正常工作。

(2) OE : 存储器读信号。 CE=0 , OE=0 时为读操作, 实验中将其接地,恒置为 0。

(3) WE : 写信号。 CE=0, 在 OE 恒为 0 的情况下,WE=1 为写操作,WE=0 为读操作。

(4) P1 : 脉冲信号,当 WE=1 、P1=1 时,6116 进行写操作。

(5) LDAR : 对地址寄存器 AR 进行加载的控制信号,LDAR=1 时为加载状态。

(6) P2: 脉冲信号,当 LDAR=1 时,在上升沿将地址载入 AR 。74LS273 触发器在时钟输入为高电平或低电平时,输入端的信号不影响输出,仅仅在时钟脉冲的上升沿,输入端数据才发送到输出端,同时将数据锁存。

(7) SW-BUS:开关输出三态门使能信号,为 0 时将 74LS245 输入引脚的值从输出引脚输出,即将 SW7~ SW0 数据发送到数据总线。

4、实验原理

略

5、实验内容与步骤

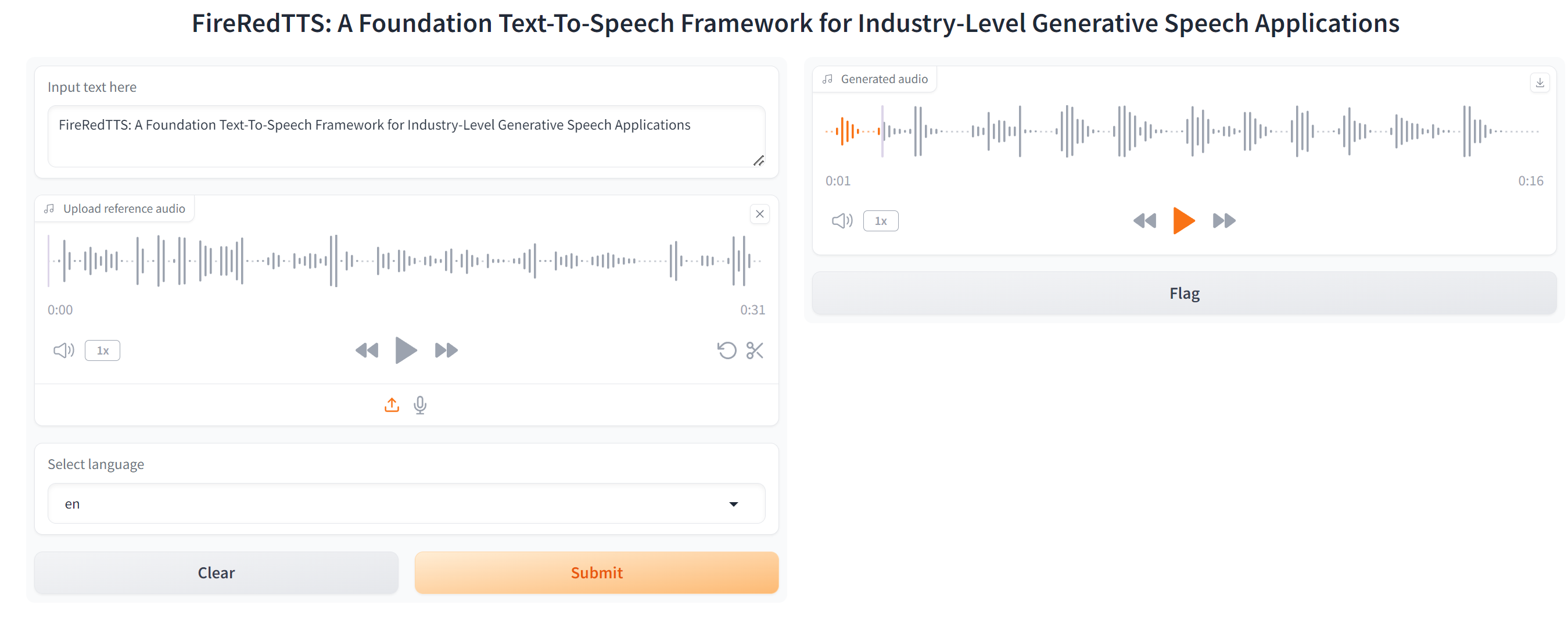

(1) 运行虚拟实验系统,从左边的实验设备列表选取所需组件拖到工作区中,按照上图所示组建实验电路,得到如下图所示的实验电路。注意:图中没有使用总线,元器件通过两两之间连线实现彼此连接。当然,实验时也可以选用总线来连接器件。

(2) 进行电路预设置。

1.将 74LS273 的 MR置 1 , AR 不清零;

2.CE=1, RAM6116 未片选;

3.SW-BUS =1,三态门关闭。

(3) 打开电源开关。

(4) 存储器写操作。向01H、02H、03H、04H、05H存储单元分别写入十六进制数据 11H 、12H 、13H 、 14H 、 15H , 具体操作步骤如下(以向 01 号单元写入 11H 为例):

1.将 SW7~SW0 置为 00000001 ,SW-BUS =0,打开三态门,将地址送入 BUS ;

2.LDAR =1 ,发出 P2 单脉冲信号,在 P2 的上升沿将 BUS 上的地址存入 AR,可通过观察 AR 所连接的地址灯来查看地址, SW-BUS=1 关闭三态门.

3.CE =0,WE=1 , 6116 写操作准备(注意:此时 WE =1,因而会读出此地址原有数据);

4.将 SW7~SW0 置为 00010001 , SW-BUS =0,打开三态门,将数据送入BUS ;

5.发出 P1 单脉冲信号,在P1的上升沿将BUS上的数据 00010001 写入 RAM 的 01 地址;

6.CE=1, 6116 暂停工作,SW-BUS =1 关闭三态门。

提示:可以使用“工具”菜单中的“存储器芯片设置”实时查看存储器芯片中的数据。注意本虚拟实验系统的6116芯片中预存了一些代码和数据。

(5) 存储器读操作。依次读出01H、02H、03H、04H、05H单元中的内容,观察上述单元中的内容是否与前面写入的-致。具体操作步骤如下(以从01号单元读出数据11H为例)

1.将 SW7~SW0 置为 00000001 , SW-BUS =0 ,打开三态门,将地址送入 BUS ;

2.LDAR=1,发出P2单脉冲信号,在P2的上升沿将BUS上的地址存入 AR 中,可通过观察 AR 所连接的地址灯来查看地址,SW-BUS =1 关闭三态门;

3.CE=0 ,WE=0,6116 进行读操作,观察数据灯是否为先前写入的 00010001 。

4.CE =1 ,6116 暂停工作

6思考与分析

1.静态半导体存储器与动态半导体存储器的主要区别是什么?

答:静态RAM(SRAM)速度非常快,只要电源存在内容就不会自动消失。集成度相对较低,功耗也较大。一般高速缓冲存储器用它组成。

动态RAM(DRAM)的内容在10-3或10-6秒之后自动消失,因此必须周期性的在内容消失之前进行刷新。由于它的基本存储电路由一个晶体管及一个电容组成,因此它的集成度高,成本较低,另外耗电也少,但它需要一个额外的刷新电路。DRAM运行速度较慢,SRAM比DRAM要快2~5倍,一般,PC机的标准存储器都采用DRAM组成。

2.由两片6116(2K8)怎样扩展成(2K16)或(4K*8)的存储器?怎样连线?

答:两片进行位(竖着排两个)拓展扩展成2K×16,将两片存储器的地址、片选CS、读写控制端R/W相应并联,数据端分别引出。两位进行字扩展(横着排两个)扩展成4K×8,数据线与两片的数据端相连,地址总线的低位地址与两片的11位地址端相连,而高位地址经过译码器和片选端相连。

3.查阅 6116 芯片的数据手册,在CE=0、OE=0、WE=1的条件下,当输入的地址信息变化时,输出的数据是否会相应变化?是否有延迟?

答:会变化,有延迟。