TMS320F280025 串口SCI的使用

`

文章目录

- TMS320F280025 串口SCI的使用

- 框图分析

- 串口特点

- 可编程数据格式

- SCI端口中断

- 非FIFO/FIFO模式下SCI中断的操作/配置

-

- UartDriver.c

- UartDriver.h

串口时钟由PCLKCR7控制使能,默认位系统时钟4分频

串口接收与发送都可以触发中断

串口使用的引脚需要配置GPIO复用

框图分析

串口配置包括数据格式设置、通讯速率设置、FIFI设置、中断设置

对于发送和接受都可以选择是否使用FIFO

对于发送和接收都可以设置是否触发中断和FIFO中断,对于接收可以检测数据是否正确,如数据错误产生对应标志位

其主要功能单元如下:

①一个发送器(TX) 及相关寄存器。

–SICTXBUF: 发送数据缓冲寄存器, 存放所要发送的数据(由 CPU 装载) 。

–TXSHF 寄存器: 发送移位寄存器, 从 SCITXBUF 寄存器接收数据, 并将数据移位到 SCITXD 引脚上, 每次移 1 位数据。

②一个接收器(RX) 及相关寄存器。

–SCIRXBUF: 接收数据缓冲寄存器, 存放 CPU 所要读取的数据, 来自远程处理器的数据装入寄存器 RXSHF, 然后又装入接收数据缓冲寄存器 SCIRXBUF 和接收仿真缓冲寄存器 SCIRXEMU 中。

–RXSHF 寄存器: 接收移位寄存器, 从 SCIRXD 引脚移入数据, 每次移 1 位。

③一个可编程的波特率产生器。

串口特点

SCI模块的功能包括:

SCI模块的功能包括:

•两个外部针(针都可以用作GPIO,如果不是用于SCI):

- SCITXD: SCI transmit-output

–SCIRXD: SCI接收输入

•波特率可编程64 k不同利率

•数据字格式-一个起始位数据字长度可编程从一到八个比特—

—可选的偶数/奇数/不校验位

-一个或两个停止位区分地址和一个额外的数据(地址模式)

•四个错误检测标志:

•两种唤醒多处理器模式:空闲线和地址位

•半双工或全双工操作

•双缓冲接收和发送功能

•发送和接收操作可以通过中断驱动或轮询算法与状态标志来完成

•发送和接收中断的单独启用位(BRKDT除外)

•NRZ(非归零)格式增强功能包括:

•16级发送/接收FIFO

可编程数据格式

SCI数据的接收和发送都采用NRZ (non-return-to-zero)格式。如图26-3所示,NRZ数据格式包括:

•1个起始位

•1 ~ 8个数据位

•一个奇偶校验位(可选)

•一个或两个停止位

•一个用来区分数据和地址的额外位(仅限地址位模式)

数据的基本单位称为字符,长度为1 ~ 8位。数据的每个字符都用一个起始位、一个或两个停止位以及可选的奇偶校验位和地址位进行格式化。带格式化信息的数据字符称为帧,如图26-3所示。

SCI端口中断

SCI接收和发送可以中断控制。SCICTL2寄存器有一个标志位(TXRDY),它表示活动的中断条件,SCIRXST寄存器有两个中断标志位(RXRDY和BRKDT),加上RX ERROR中断标志,它是FE、OE、BRKDT和PE条件的逻辑或。发送器和接收器具有单独的中断启用位。如果不启用,则不会断言中断;但是,条件标志保持活动状态,反映传输和接收状态。

SCI对于接收端和发送端具有独立的外围中断向量。外围中断请求可以是高优先级的,也可以是低优先级的。这是由外设输出到PIE控制器的优先级位表示的。当RX和TX中断请求处于相同的优先级时,接收端总是比发送端具有更高的优先级,从而减少了接收端溢出的可能性。

外围中断的操作在系统控制和中断一章的外围中断一节中描述。

•如果RX/BK INT ENA位(SCICTL2, bit 1)被设置,当发生以下事件之一时,接收方外设中断请求被断言:—SCI接收到一个完整的帧,并将RXSHF寄存器中的数据传输到SCIRXBUF寄存器中。这个动作设置RXRDY标志(SCIRXST,位6)并启动中断。

-发生中断检测条件(SCIRXD在缺少停止位后的9.625位周期内处于低电平)。这个动作设置BRKDT标志位(SCIRXST,第5位)并启动中断。

•如果设置了TX INT ENA位(SCICTL2.0),当SCITXBUF寄存器中的数据被转移到TXSHF寄存器时,发送器外设中断请求被断言,表明CPU可以写SCITXBUF;这个动作设置TXRDY标志位(SCICTL2,位7)并启动中断。

SCI模块中断反应时间-如果在应用程序中发生紧时序,可能会发生偶尔的BRKDT或其他错误,如FE/PE被触发。

中断不会被触发,直到大约7/8的停止位被检测到(大约0.875位时间)。ISR表项前的实际延迟值为:((7BAUD_CLK_PERIOD)/

8+3SYSCLK_PERIOD)。 在RX

ISR完成之前,SCI不会开始读取额外的位/字符,所以在下一个字节的起始位开始之前完成ISR。不管中断原因是什么,这留下了大约1/8比特时间(大约0.125比特时间)来完成整个ISR。

如果ISR在下一个起始位开始之前没有完成(在RX线再次变低之前),SCI模块在错误的位置开始读取起始位,因此可能会错误地读取所有位,直到下一个正确对齐的起始位(当ISR有足够的时间在再次开始位之前处理)。

避免错误的推荐方法(以适应ISR开始所需的0.875位时间):

- 保持RX ISR短。RX ISR必须仅用于将FIFO/缓冲区中的数据移动到内存中,在内存中数据可以在另一个时间要求较低的函数中进行处理。

- 避免在SCI RX ISR中过多地嵌套其他中断。不要允许嵌套延迟SCI RX ISR完井超过大约0.125位的时间窗口。

- 如果需要额外的时间(超过大约0.125比特的时间),在将额外的数据传输到C2000设备的SCI RX引脚之前,可以在其他设备的固件中添加延迟。 其他设备可以通过以下方式增加延迟:

a.向C2000设备发送带有2个停止位的字节,为C2000 RX ISR完成提供大约1.125位的处理时间。

b.在发送一个字节后,在发送到C2000设备的另一个设备的固件中增加手动延迟,为C2000 RX

ISR完成提供(延迟+大约0.125比特时间)处理时间。 c.在每次C2000

RX中断发生后,在发送到C2000设备的另一个设备的固件中增加手动延迟,为C2000 RX

ISR完成提供(延迟+大约0.125比特时间)处理时间。这很难实现,因为需要另一个设备来预测传输的数据何时触发C2000设备上的RX中断。触发RX中断的例子有:到达RX-

fifo水平、发送BRKDT、发生RXERROR等。RXRDY和BRKDT位的中断产生由RX/BK INT ENA位(SCICTL2,位1)控制。RX ERROR位的中断产生由RX ERR

INT ENA位(SCICTL1,位6)控制。

非FIFO/FIFO模式下SCI中断的操作/配置

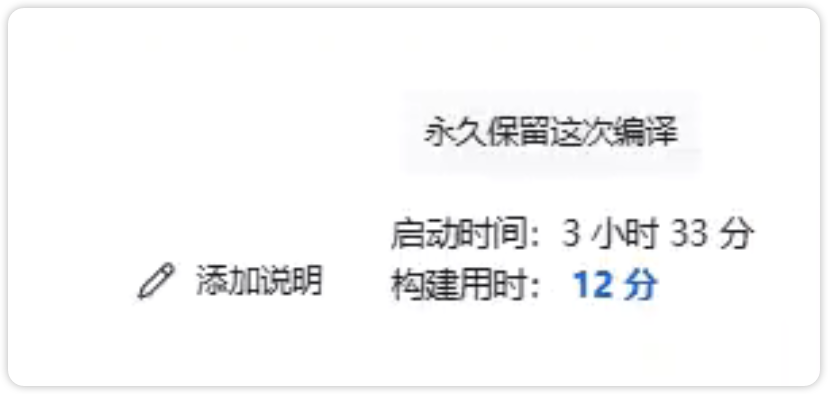

①复位: 在上电复位时, SCI 工作在标准 SCI 模式, 禁止 FIFO 功能。 FIFO的寄存器 SCIFFTX、 SCIFFRX 和 SCIFFCT 都被禁止。

②标准 SCI: TXINT/RXINT 中断作为 SCI 的中断源。

③FIFO 使能: 通过 SCIFFTX 寄存器的 SCIFFEN 位置 1, 使能 FIFO 模式。 在任何操作状态下 SCIRST 都可以复位 FIFO 模式。

④寄存器有效: 所有 SCI 寄存器和 SCI FIFO 寄存器(SCIFFTX、 SCIFFRX 和SCIFFCT) 有效。

⑤中断: FIFO 模式有两个中断, 一个是发送 FIFO 中断 TXINT, 另一个是接收 FIFO 中断 RXINT。 FIFO 接收、 接收错误和接收 FIFO 溢出共用 RXINT 中断。 标准 SCI 的 TXINT 将被禁止, 该中断将作为 SCI 发送 FIFO 中断使用。

⑥缓冲: 发送和接收缓冲器增补了 2 个 16 级的 FIFO, 发送 FIFO 寄存器是 8位宽, 接收 FIFO 寄存器是 10 位宽。 标准 SCI 的一个字的发送缓冲器作为发送FIFO 和移位寄存器间的发送缓冲器。 只有移位寄存器的最后一位被移出后, 一个字的发送缓冲才发送 FIFO 装载。 使能 FIFO 后, 经过一个可选择的延迟(SCIFFCT) , TXSHF 被直接装载而不再使用 TXBUF。

⑦延迟发送: FIFO 中的数据传送到发送移位寄存器的速率是可编程的, 可以通过 SCIFFCT 寄存器的位 FFTXDLY(7~0)设置发送数据间的延迟。 FFTXTDLY(7~0)确定延迟的 SCI 波特率时钟周期数, 8 位寄存器可以定义从 0 个波特率时钟周期的最小延迟到 256 个波特率时钟周期的最大延迟。 当使用 0 延迟时, SCI 模块的FIFO 数据移出时, 数据间没有延时, 一位紧接一位的从 FIFO 移出, 实现数据的连续发送。 当选择 256 个波特率时钟的延迟时, SCI 模块工作在最大延迟模式, FIFO 移出的每个数据字之间有 256 个波特率时钟的延迟。 在慢速 SCI/UART 的通信时, 可编程延迟可以减少 CPU 对 SCI 通信的开销。

⑧FIFO 状态位: 发送和接收 FIFO 都有状态位 TXFFST 或 RXFFST(位 12~0) ,这些状态位显示当前FIFO内数据的个数。当状态位为0时, 发送FIFO复位TXFIFO和接收复位位 RXFIFO 会被设置为 1, 会将 FIFO 指针复位为 0, FIFO 重新开始运行。

⑨可编程的中断级: 发送和接收 FIFO 都能产生 CPU 中断, 只要发送 FIFO 状态位 TXFFST(位 12-8) 与中断触发优先级 TXFFIL(位 4-0) 相匹配, 就产生一个中断触发, 从而为 SCI 的发送和接收提供一个可编程的中断触发逻辑。

UartDriver.c

/*

* UartDriver.c

*

* Created on: 2024年8月8日

* Author: Paranoid

*/

#include "main.h"

//

// Defines

//

// Define AUTOBAUD to use the autobaud lock feature

//#define AUTOBAUD

//

// Globals

//

uint16_t loopCounter = 0;

//

// Function Prototypes

//

__interrupt void Scia_RX_INT_ISR(void);

__interrupt void Scia_TX_INT_ISR(void);

//

// Main

//

void SciaDriver_Init(

![[Notepad++] 文本编辑器的下载及详细安装使用过程(附有下载文件)](https://i-blog.csdnimg.cn/direct/7f936e06ccb548d48521027c2d48749d.png)