1.概述

无论DPLL还是PLL都是由PD,LPF和DCO/VCO组成。

PD:鉴相器,是将VCO/DCO输出的频率信号分频后与refclk进行相位比对,输出一个相位差信号

LFP:是将相位差信号转换为VCO的压控信号或DCO的延迟信号。

VCO:根据不同的输入电压【注意不是电源电压而是输入的控制电压】产生不同的输出频率

DCO:根据不同的输入延迟控制信号,控制DCO内部环路的延迟,以输出不同的频率

以前一直有三个误解

- 认为refclk是VCO/DCO的输入clk,这个是错误的。VCO/DCO都是一个具有负反馈的环路振荡器,振荡器只需要很小的一个扰动就能起振,比如说在关闭的振荡环路打开了,这样一个变化就能启动

- PLL/DPLL只有一个环路也是错误的认识。PLL的PD/LPF/VCO组成一个环路,而VCO内部也必然是一个负反馈环路。DPLL也是类似。

- 以前认为DCO的延迟环是由于控制电压的变化导致每个延迟单元的延迟变化而变化。实际是输入的延迟控制信号通过控制延迟cell的开关来控制的

本文主要介绍振荡器,VCO由于涉及模拟器件,比较复杂。我们以DCO为例来分析,下面的一个由多级反相器组成的环路就是一个简单的DCO

其中第一级采用与非门是为了控制环路的开关,如果A1输入为1,那么环路不会振荡。这个A1可以接DPLL_en.

那么假设A1从1跳变到0,每个反相器和与非门的延迟都是t,m为3.我们分析A0的信号波形

0 : 0

3t: 1

6t: 0

9t: 1

.....

明显A1(out)是一个周期为6t方波输出。

2.DCO

上一节的概述中给出了简单的DCO原理说明,同时可以发现上节的DCO输出周期只能稳定在2mt,如果分开上升沿延迟Tr和下降沿延迟Tf,这个周期就是m×(Tr+Tf).如何才能够做一个能够调节输出频率的DCO呢?

常见的作法如下:

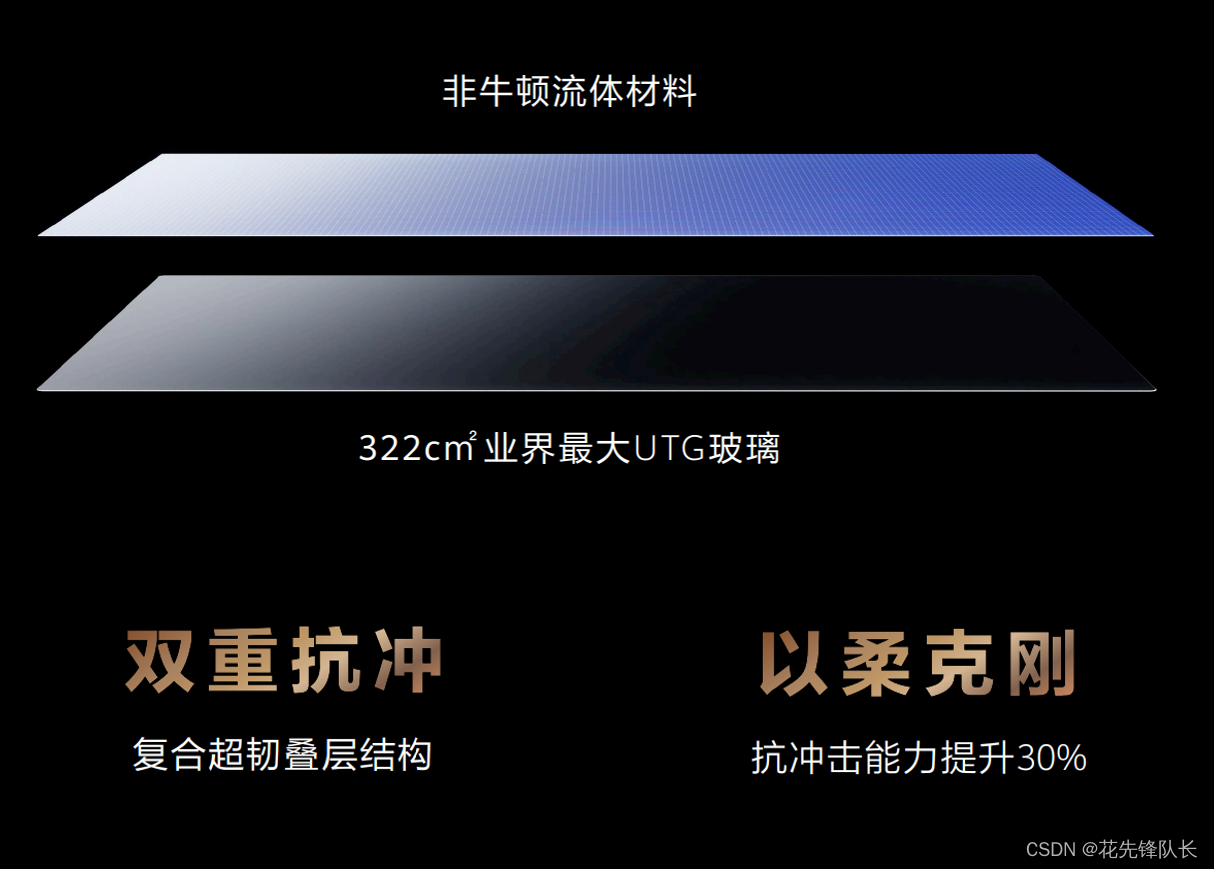

上图的结构中,我们把每一列并联的反相器叫做一级延迟;把每一行串联的反相器叫做一组延迟单元。每一组延迟单元是同时打开和关闭的,不存在一组延迟单元内有些延迟关闭,有些导通,这样对于串联电路来说该组还是关闭状态。

每级延迟单元由一个倒相器和若干个与之并联的三态倒相器组成 ,通过控制导通三态倒相器的数目,控制该级延迟单元的延迟时间 ,从而调整振荡器的振荡频率 ,综合速度、功耗、 分辨率、抗噪声能力等因素 ,DCO的级数选用 9级。 为了使能/禁止 DCO的工作状态 ,第一个倒相器由与非门NAND代替 。

三态倒相器的栅电容与其工作状态无关,也就是说无论三态反相器是否导通,每个倒相器的负载CL保持不变。但导通与否是影响每一级环路中的等效电阻。进而影响了每一级延迟单元的Tr和Tf。

有两个结论:

- 在总反相器个数不变的情况下【如上图共38组反相器的情况下】,打开的反相器组越多输出的周期越小,频率越大。

- 使用相同器件的两个DCO,一个具有n0组×m级延迟单元,另一个具有n1组×m级延迟单元。如果n0<n1则,在两个DCO的全部延迟单元都打开的情况下,n0的输出周期小,频率大

理解起来就是关闭的延迟组,延迟效应最大,会使输出频率变低,导通之后,该延迟组反而延迟效应降低,频率有所上升。但是DCO中所有的延迟组都打开,也不会超过只有一个延迟组的输出最大频率【也即上一节给出的m×(Tr+Tf)】.

这里面参考了两篇文章:

数控振荡器的基本结构以及电路原理解析-CSDN博客

上面这一篇是本人转载的博客,源地址:

数控振荡器的基本结构以及电路原理解析 - 接口/总线/驱动 - 电子发烧友网

这篇文章在介绍时把一行延迟单元叫做一级延迟单元,注意理解上的区别。

还有一篇收集的论文

https://download.csdn.net/download/cy413026/89823956

原作者:邓小莺,杨 军,陈 鑫 ,时龙兴 (东南大学 国家专用集成电路系统工程技术研究中心,南京 210096)

更详细的一些理论推导也可参见:

模拟集成电路设计系列博客——8.4.1 全数字锁相环介绍 - sasasatori - 博客园